Altera FPGA时序约束详解:从入门到精通

FPGA时序约束是FPGA设计中的重要环节,本文档详细介绍了如何在Altera FPGA中进行时序分析和优化,旨在帮助初学者快速理解和掌握这一关键技能。主要内容涵盖以下几个部分:

1. **时序分析基本概念**:首先,文章介绍了同步逻辑的时延模型,包括时钟抖动、偏斜,以及建立时间(Setup Time)、保持时间(Hold Time)、恢复时间(Recovery Time)和移除时间(Removal Time)等基本概念。这些参数是衡量信号传输速度和准确性的关键指标。

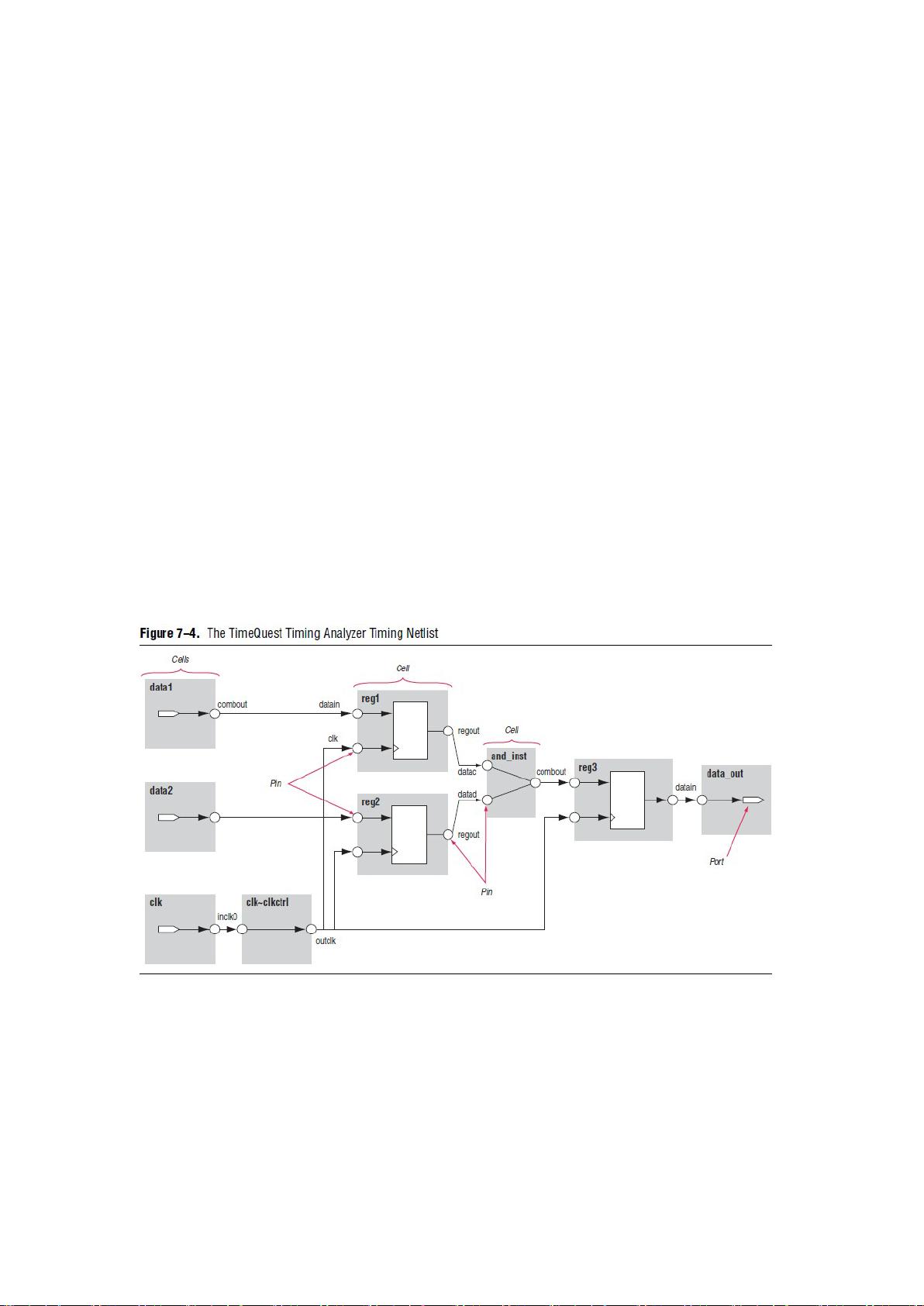

2. **Altera器件时序模型**:文档解释了Altera FPGA特有的时序模型,这有助于设计师了解实际硬件环境下的信号行为。

3. **基本单元与paths**:探讨了FPGA中的基本逻辑单元和信号路径,这对于理解信号流和潜在的时序问题至关重要。

4. **关键路径与时序优化方法**:指出了识别和优化设计中关键路径的方法,通过调整布线、选择适当的逻辑门延迟或使用多级缓冲等方式来改善时序性能。

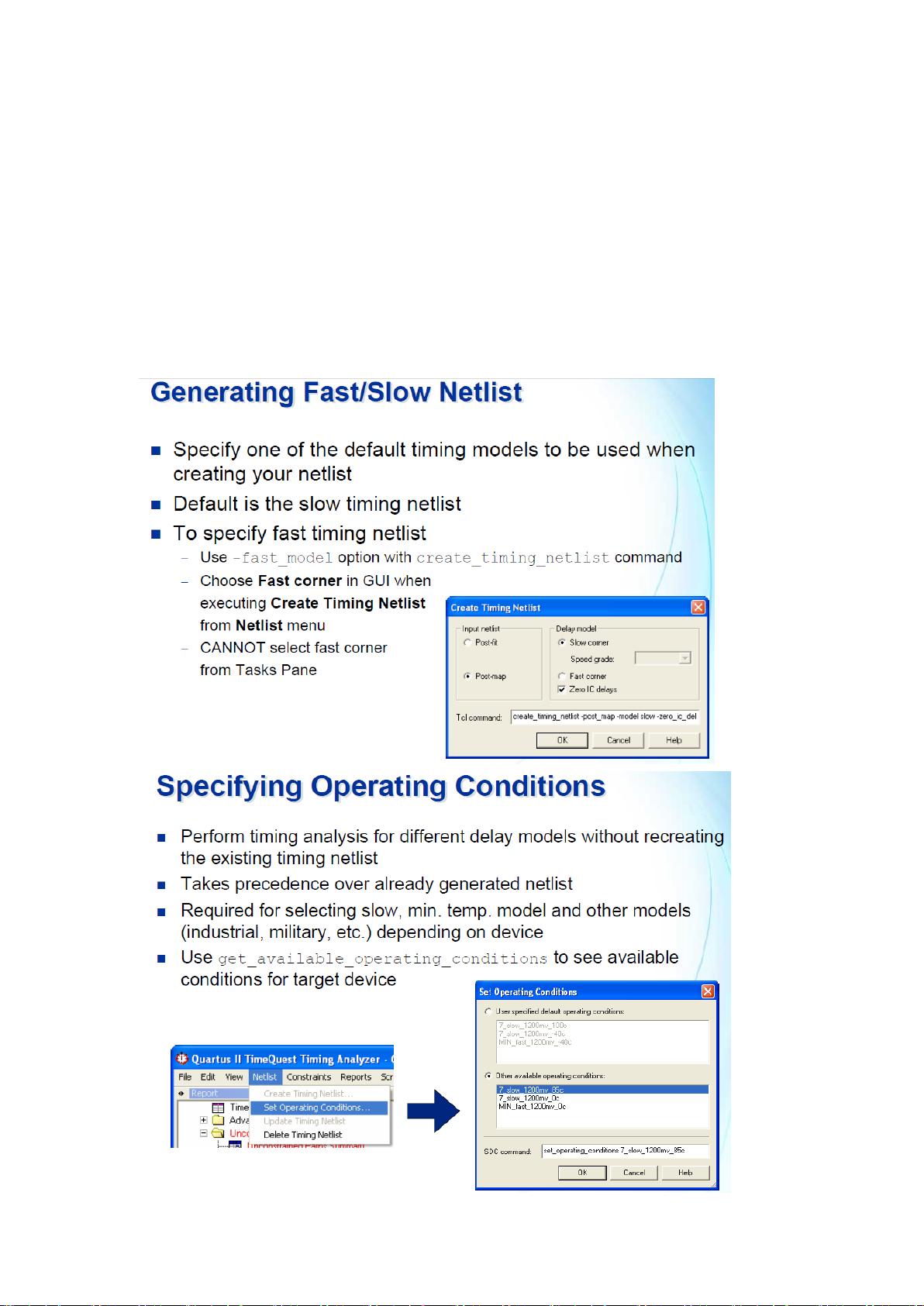

5. **FPGA时序约束的几种方法**:这部分详细介绍了在Timequest工具中设置时序约束的具体步骤,包括创建时钟、生成时钟、PLL时钟处理、自动时钟检测与创建、默认约束、时钟延迟、不确定性和去除常见时序悲观主义等。

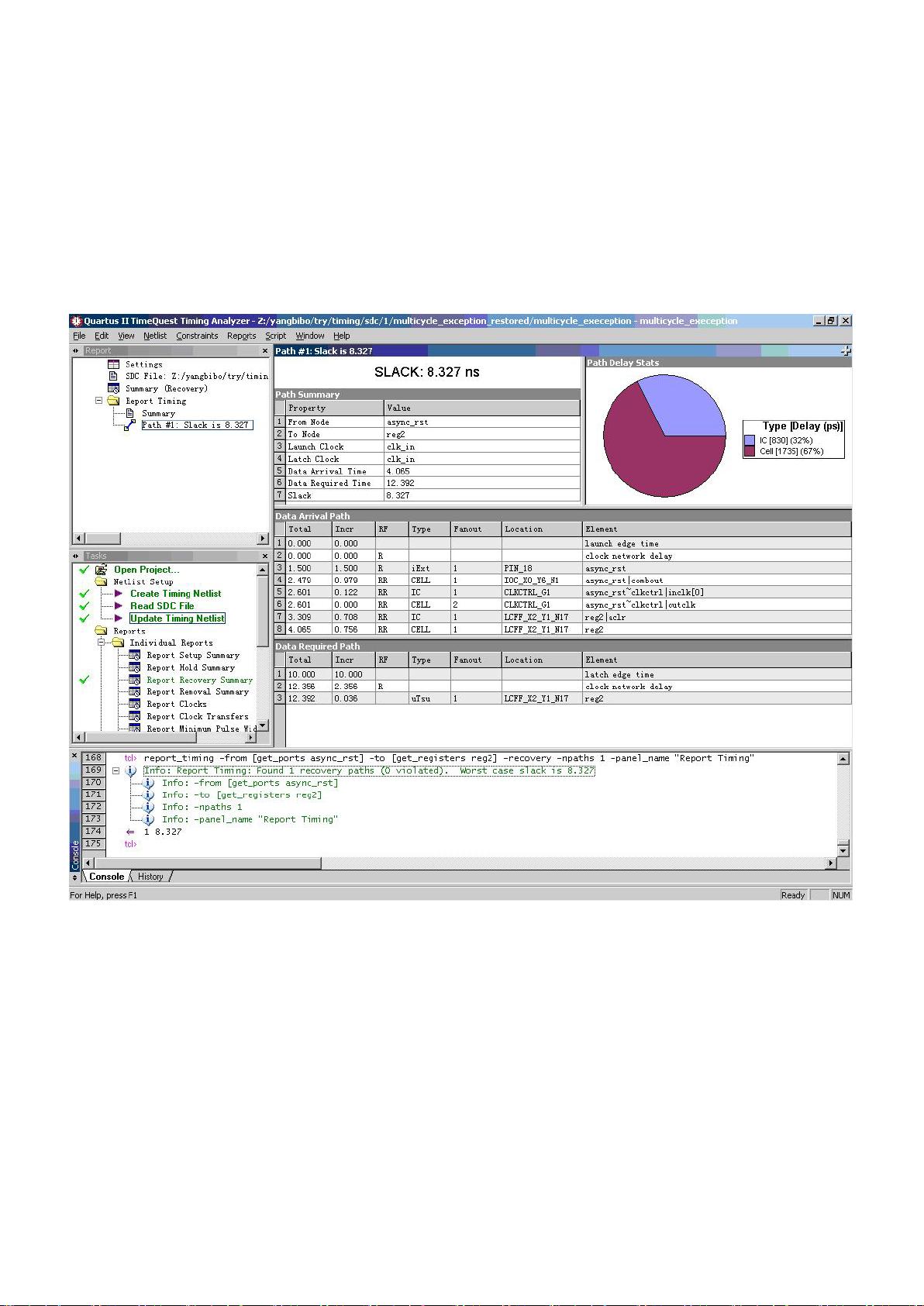

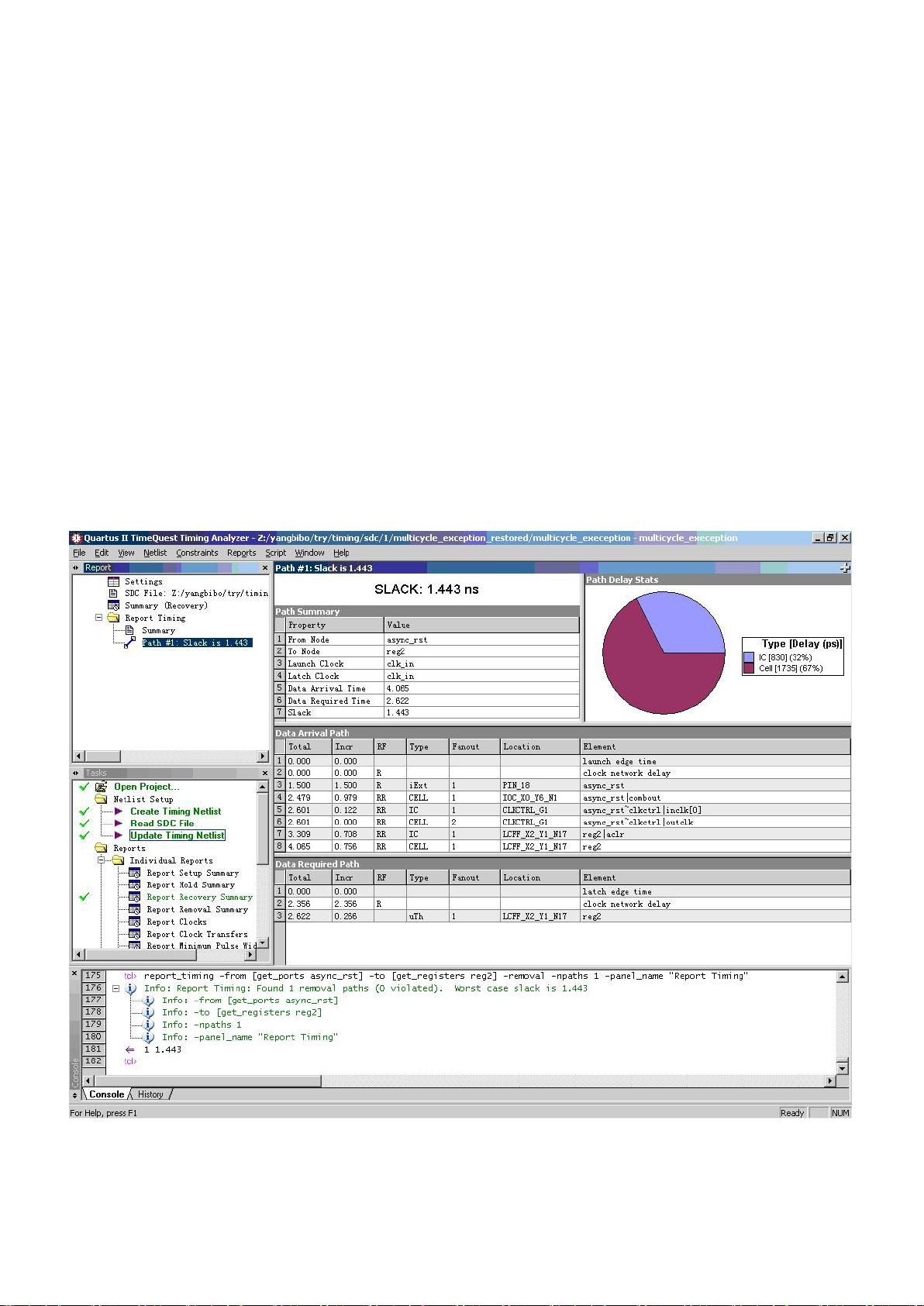

6. **Timequest时序分析器的应用**:用户指南深入讲解了如何使用Timequest进行时序分析,包括理解分析流程、图形用户界面操作、解读时序波形图以及计算时序余量(如Setup Time和Multicycle Path余量)。

7. **具体操作示例**:针对时钟和I/O接口的约束设置了详细的步骤,如创建时钟类型、处理I/O接口的同步和组合逻辑,以及如何检查约束是否满足设计要求。

这份教程提供了从基础理论到实践操作的全面指导,对于学习者理解和实施Altera FPGA的时序约束有着重要的参考价值。通过阅读和实践,设计者可以更有效地确保设计的时序性能,从而实现高效和稳定的FPGA系统。

1298 浏览量

836 浏览量

236 浏览量

364 浏览量

5228 浏览量

点击了解资源详情

点击了解资源详情

飞天猪run

- 粉丝: 0

- 资源: 6

最新资源

- 地产财富手机网页模板

- personal-blog:个人nuxtcontent博客

- 6,SD卡资料.zip

- 锂材料报告(40页).zip

- 奥列达

- STM32+3G4G.rar

- 聚类马氏距离代码MATLAB-SDCOR:用于大规模数据集中局部离群值检测的可扩展的基于密度的聚类

- 公路背景网站开通倒计时响应式网页模板

- protospace-34037-2

- plc精品教程19.rar

- scheduler-app

- SpringMVC文件上传与下载的实现.rar.rar

- 高斯、导数、平均、中值、导向、双边、sobel滤波器的matlab实现

- 简洁微博用户信息登录网页模板

- RPM5_MT4_[ea] - MetaTrader 4EA.zip

- WSL指令:Arch-WSL的设置指令