FPGA实现的BiSS协议光电编码器高速通信模块

100 浏览量

更新于2024-09-01

1

收藏 248KB PDF 举报

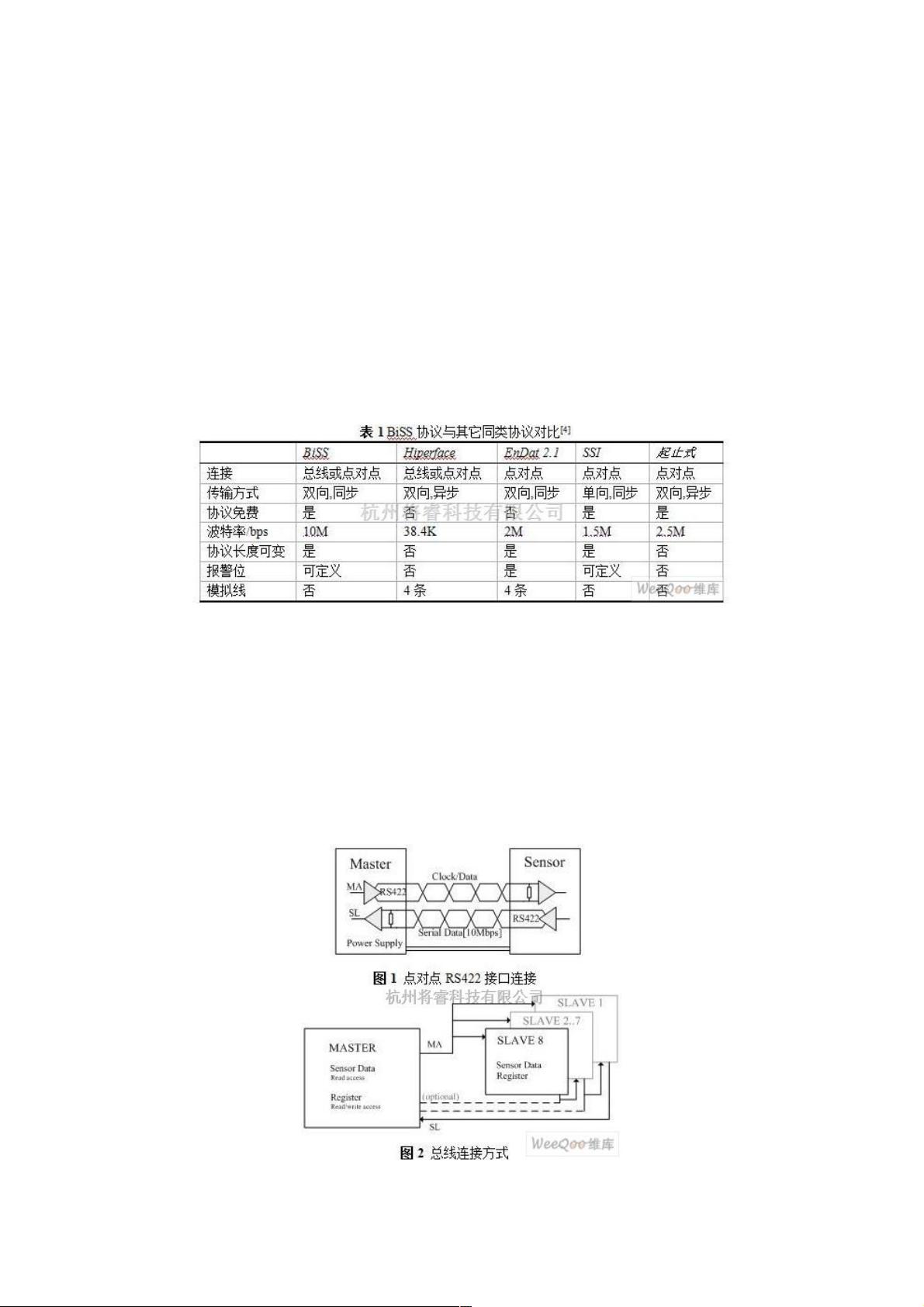

"本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)领域中,基于FPGA(现场可编程门阵列)的BiSS协议用于光电编码器通信模块的设计。BiSS协议作为一种高速、灵活的串行通信协议,其优势在于能够实现10Mbps的通信速率,远超其他常见的串行通信协议,如SSI、EnDat、Hiperface和起止式异步协议。文章介绍了BiSS协议的基本特性和在工业自动化中的应用价值,并详细阐述了BiSS协议的读数模式和寄存器模式的工作原理。"

在工业自动化系统中,位置编码器作为关键的反馈元件,其性能直接影响系统的精度和响应速度。绝对位置式编码器通常采用串行通信来传输数据,以减少信号线的数量和提高数据传输效率。BiSS协议,由德国IC-Haus公司开发,是一种开放式的双向同步串行通信协议,其特点是通信速度快、可定制性强。与传统的RS422接口的波特率上限相同,BiSS协议能够达到10Mbps,显著优于其他协议,从而提高了系统的实时性能。

BiSS协议有两种主要操作模式:读数模式和寄存器模式。在读数模式下,编码器直接返回位置信息;而在寄存器模式下,除了位置信息外,还可以进行配置寄存器的读写操作。这种模式下,主机通过MA信号发送时钟和地址信息,编码器根据这些信息返回相应的内容。通过调整MA信号的占空比,可以编码额外的信息,增强了通信的灵活性。

在工业应用中,BiSS协议的高波特率、灵活的总线连接方式以及无需额外协议许可费用等优点,使其成为高速、低成本解决方案的理想选择。同时,全数字接口避免了模拟器件引入的噪声问题,进一步提高了系统的稳定性和可靠性。因此,基于FPGA的BiSS协议通信模块在设计时需要充分考虑这些特性,以确保在满足高速通信需求的同时,实现系统的高效和稳定运行。

在具体设计时,FPGA因其可编程性,能够灵活地实现BiSS协议的硬件逻辑,包括时钟同步、数据编码和解码、错误检测等功能。设计师需要熟悉FPGA的逻辑设计流程,使用硬件描述语言(如VHDL或Verilog)编写代码,并利用EDA工具进行仿真和验证,最后将设计下载到FPGA中实现实际功能。

总结来说,基于FPGA的BiSS协议光电编码器通信模块设计是一项技术挑战,它涉及到高速串行通信协议的理解、FPGA硬件逻辑设计以及工业应用的优化。通过有效的设计和实施,这样的通信模块能够显著提升工业自动化的反馈性能,实现更快速、更精确的位置控制。

点击了解资源详情

点击了解资源详情

130 浏览量

167 浏览量

188 浏览量

302 浏览量

124 浏览量

104 浏览量

144 浏览量

weixin_38702844

- 粉丝: 2

- 资源: 921