Verilog实现FIR滤波器设计与MATLAB仿真

需积分: 0 133 浏览量

更新于2024-08-04

收藏 1.5MB DOCX 举报

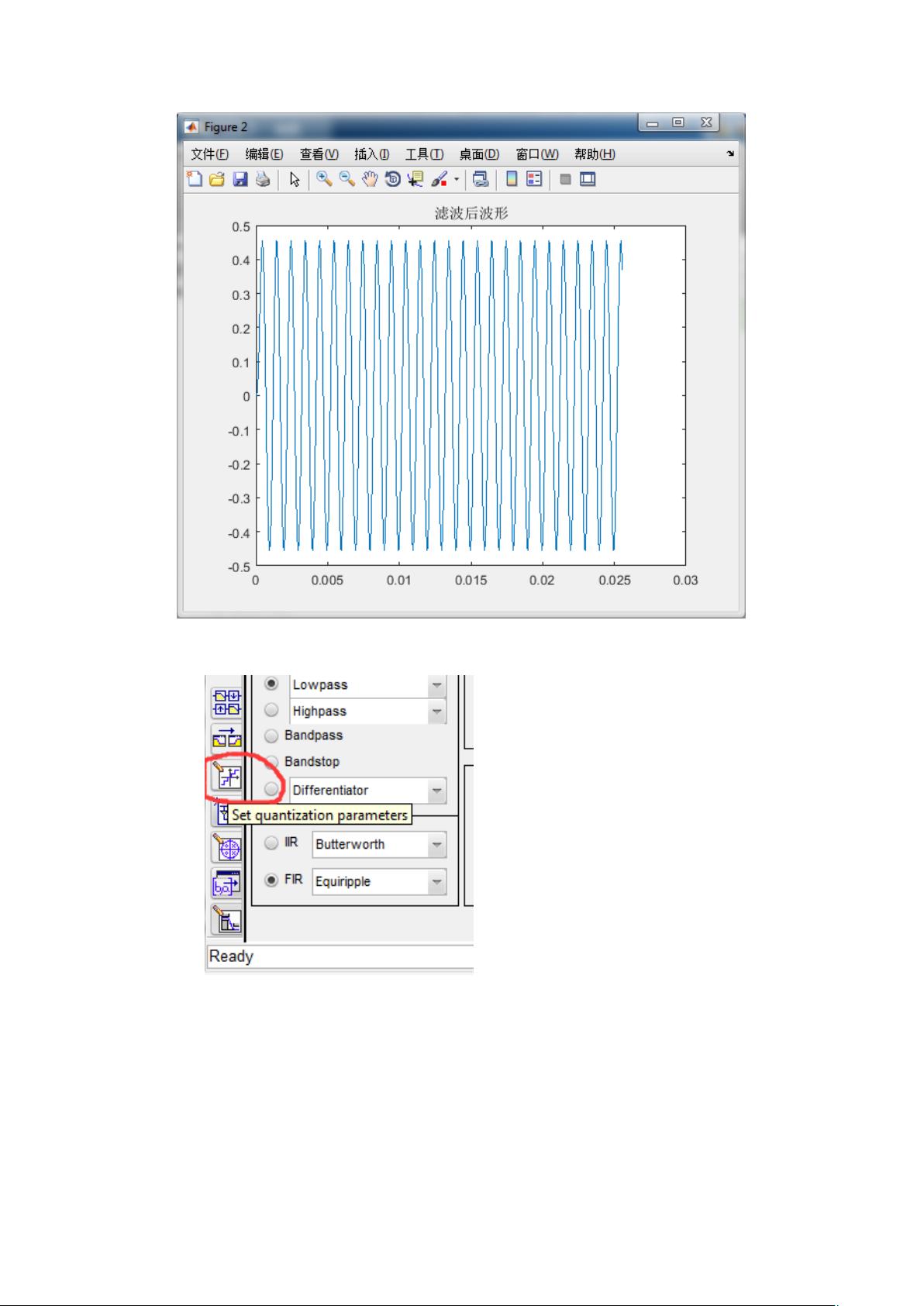

"该实验指导书主要介绍了如何使用MATLAB的fdatool设计FIR滤波器,并在Verilog中实现数字滤波器的设计与验证。实验目标包括学习Verilog语法,掌握VIVADO环境下的Verilog编程,理解Debug技巧,以及熟悉FIR滤波器的实现过程。实验内容涉及在MATLAB中产生混合信号,设计滤波器,量化信号,生成coe文件,然后使用Verilog实现FIR滤波器,并在FPGA开发板上进行验证。"

实验详细步骤:

1. **MATLAB混合信号产生**:在MATLAB环境中,可以利用内置函数生成所需的混合信号,这通常涉及到信号处理的基础知识,如正弦波、白噪声等信号的合成。

2. **fdatool滤波器设计**:通过输入`fdatool`命令,用户可以进入滤波器设计界面。在这个界面,需要设定滤波器的阶数,采样频率,以及通带频率。这些参数的选择依据具体的应用需求,例如高频信号的滤波可能需要更高的阶数和特定的通带范围。其他设置如截止频率、阻带衰减等可根据实际应用进行调整。

3. **生成MATLAB代码**:设计完成后,选择“File”菜单中的“Generate MATLAB code”然后选择“Filter Design Function”,这会自动生成一段MATLAB代码,用于执行滤波操作。

4. **信号量化与滤波器系数保存**:在滤波器设计界面,点击“Targets”然后选择“XILINX (COE) File”可以生成滤波器的系数文件,一般为coe格式。同时,需要对混合信号进行量化,例如采用Q13格式(16位宽度,其中3位为符号位,13位为数值位)。

5. **Verilog实现FIR滤波器**:使用Verilog语言编写FIR滤波器的代码,根据之前生成的滤波器系数,将这些系数加载到滤波器结构中。这通常涉及到移位寄存器、加法器等基本逻辑元件的组合。

6. **VIVADO环境下的设计与验证**:在VIVADO开发环境中,编译和综合Verilog代码,生成比特流文件,然后下载到FPGA开发板上。通过硬件验证,比较FPGA实现的滤波结果与MATLAB仿真结果的差异。

7. **调试与优化**:如果FPGA上的滤波效果与MATLAB设计有出入,需要检查Verilog代码,调整滤波器系数或量化方式,进行调试和优化,确保两者的一致性。

实验中涉及的知识点:

- **MATLAB信号处理**:包括信号的生成、滤波器设计与仿真。

- **数字滤波器理论**:FIR滤波器的基本概念、设计方法,如窗函数法、频率抽样法等。

- **Verilog语言**:用于描述数字逻辑电路,实现FIR滤波器的硬件结构。

- **FPGA开发流程**:从Verilog代码编写到硬件实现,包括编译、综合、下载和验证。

- **量化技术**:理解不同位宽的量化对信号的影响,以及负数的补码表示。

- **数据文件格式**:coe文件的生成和读取,了解其在硬件设计中的作用。

通过这个实验,学生可以深入理解数字滤波器的原理,掌握利用MATLAB和Verilog进行数字信号处理的方法,同时增强硬件实现和验证的能力。

2021-06-26 上传

2023-12-20 上传

2021-09-30 上传

2022-08-08 上传

2018-08-30 上传

2010-06-19 上传

2021-10-02 上传

2021-09-28 上传

2022-07-15 上传

SeaNico

- 粉丝: 26

- 资源: 320

最新资源

- python学习.zip

- hovergame_project04

- leetcode-javascript

- React样式的组件

- I/O交互支持库1.2版(Kernel_IOCtrl.fne)-易语言

- PLC与气压.zip三菱PLC编程案例源码资料编程控制器应用通讯通信例子程序实例

- color-palette-generator:通过识别用户提供的图像中最常见的颜色来生成调色板的Flask网站

- Sublime Text3_64.zip

- tokoacim.github.io

- 变压器设计大师(易语言2005年大赛三等奖)-易语言

- activeportfolio:这是我的个人档案,使您可以了解更多有关我的知识。 我在Full Stack Web开发旅程中的位置以及我的未来目标

- OnlineMobileRecharge

- Portable UPnP SDK-开源

- ex_spice:带有Phoenix + Nx的SPICE模拟器

- 铁路:火车模型控制系统

- PHSX815_Project3