高速电路信号完整性仿真:设计与分析

需积分: 0 85 浏览量

更新于2024-07-30

收藏 513KB PDF 举报

"高速电路信号完整性的分析与设计"

信号完整性(Signal Integrity, SI)是电子工程领域中一个至关重要的概念,特别是在高速数字系统设计中。它涉及到确保信号在电路中传输时能够保持其原始质量和完整性,不受噪声、反射、串扰、电磁干扰(EMI)等因素影响。在本课程中,主要探讨了高速信号的特征和仿真技术。

课程内容包括了对高速信号的定义,其中高频率的信号(通常大于50MHz)和具有极短上升时间(如ns级或ps级)的信号被认为是高速信号。这类信号的快速上升沿可能导致更大的信号噪声(SSN)、更大的串扰(Crosstalk)以及更强的电磁辐射(EMI),这些问题都会对系统的稳定性和可靠性造成影响。

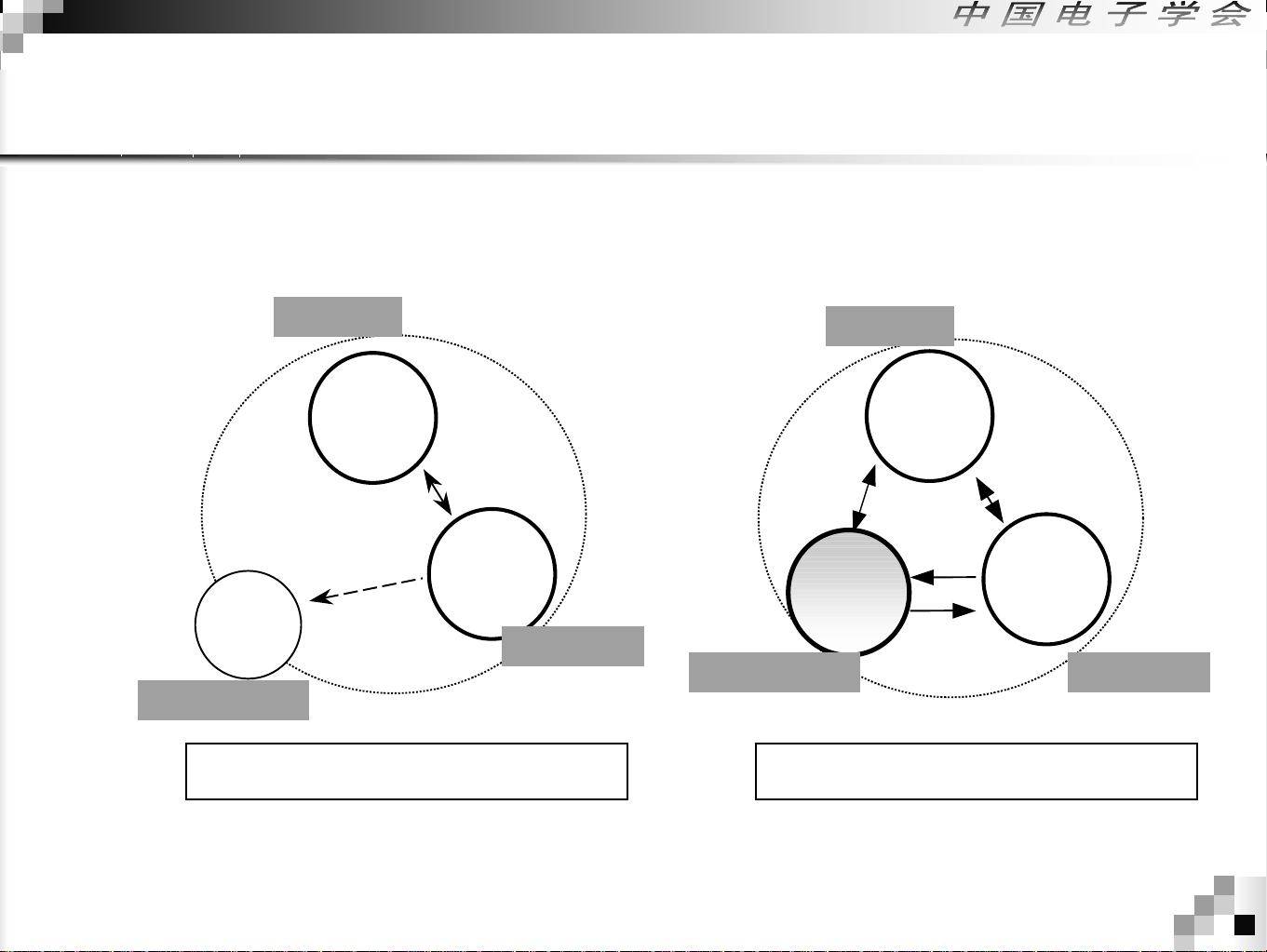

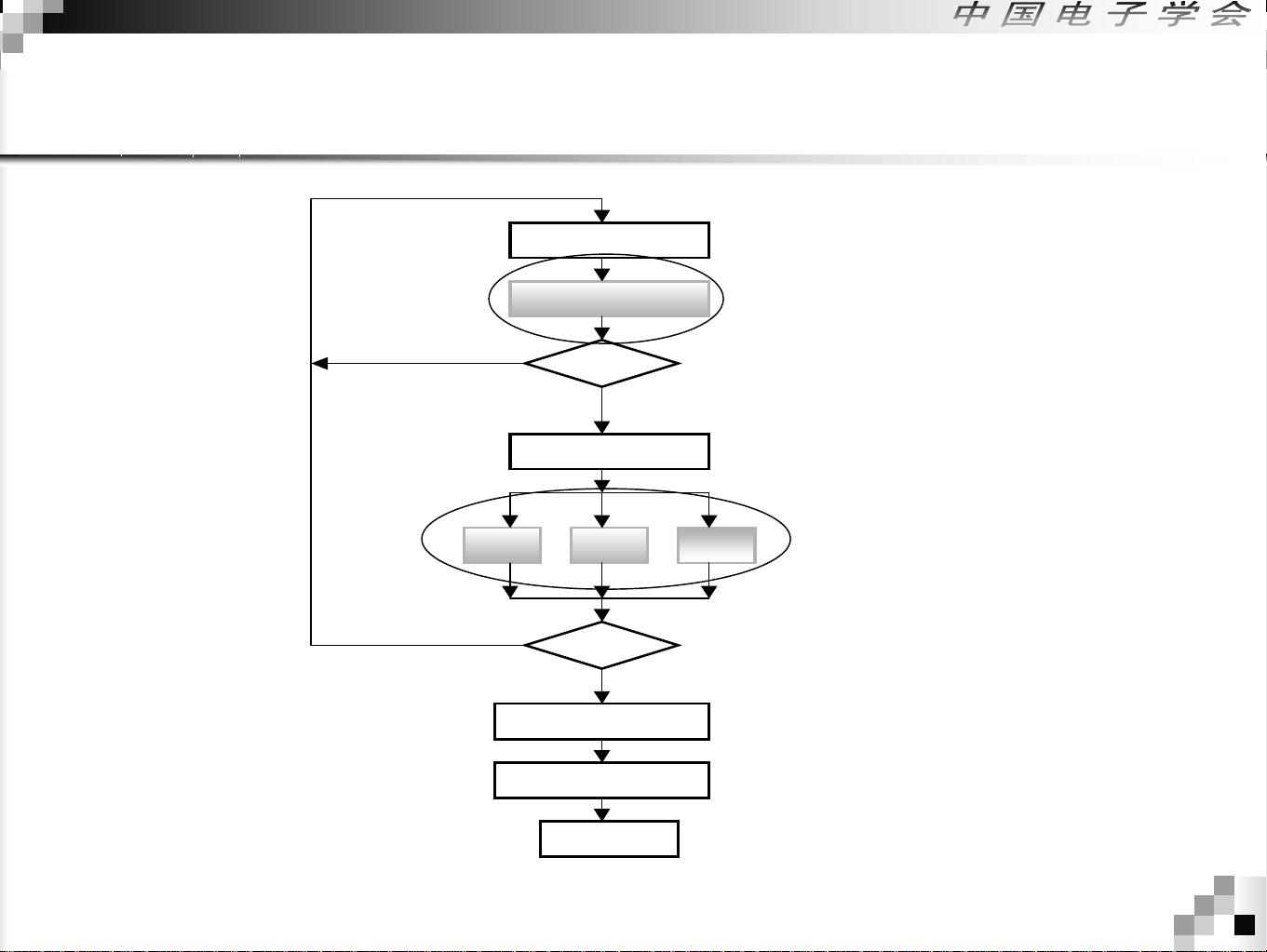

仿真在信号完整性分析中扮演着核心角色。仿真可以分为前仿真和后仿真。前仿真在布局布线之前进行,使用理想传输线模型,目的是为设计提供初步指导,但不考虑实际的损耗因素。而后仿真则在实际布线之后进行,用以验证设计的正确性和精确度,它会考虑到布线参数、损耗、阻抗匹配以及邻近传输线的串扰等实际问题。

在设计流程中,工程师需要遵循最恶劣情况(Worst Case)仿真原则,确保设计能在所有可能的极端条件下正常工作。设计流程也发生了变化,引入了信号完整性(SI)工程师的角色,他们负责在设计的不同阶段进行分析和优化。

高速数字设计方法强调了从逻辑设计到物理实现的整个过程中的信号完整性考虑。在原理图设计阶段就应进行预仿真,接着进行布局和布线,然后是后仿真,以确保PCB制作出的功能和性能满足预期,并通过EMC(Electromagnetic Compatibility)测试。

信号完整性是现代电子设计中不可忽视的关键因素,通过有效的仿真工具和技术,可以预测和解决潜在的问题,从而保证高速数字系统的高效、稳定运行。设计者需要在整个设计流程中持续关注信号完整性,确保从逻辑设计到物理实现的每个步骤都符合要求,以达到最佳的系统性能。

210 浏览量

2010-02-04 上传

104 浏览量

2008-11-26 上传

2020-08-27 上传

2012-09-04 上传

2009-06-26 上传

a40650229

- 粉丝: 0

- 资源: 11

最新资源

- AA4MM开源软件:多建模与模拟耦合工具介绍

- Swagger实时生成器的探索与应用

- Swagger UI:Trunkit API 文档生成与交互指南

- 粉红色留言表单网页模板,简洁美观的HTML模板下载

- OWIN中间件集成BioID OAuth 2.0客户端指南

- 响应式黑色博客CSS模板及前端源码介绍

- Eclipse下使用AVR Dragon调试Arduino Uno ATmega328P项目

- UrlPerf-开源:简明性能测试器

- ConEmuPack 190623:Windows下的Linux Terminator式分屏工具

- 安卓系统工具:易语言开发的卸载预装软件工具更新

- Node.js 示例库:概念证明、测试与演示

- Wi-Fi红外发射器:NodeMCU版Alexa控制与实时反馈

- 易语言实现高效大文件字符串替换方法

- MATLAB光学仿真分析:波的干涉现象深入研究

- stdError中间件:简化服务器错误处理的工具

- Ruby环境下的Dynamiq客户端使用指南