DALTON et al.: CONTINUOUS-RATE CDR WITH AUTOMATIC FREQUENCY ACQUISITION AND DATA-RATE READBACK 2715

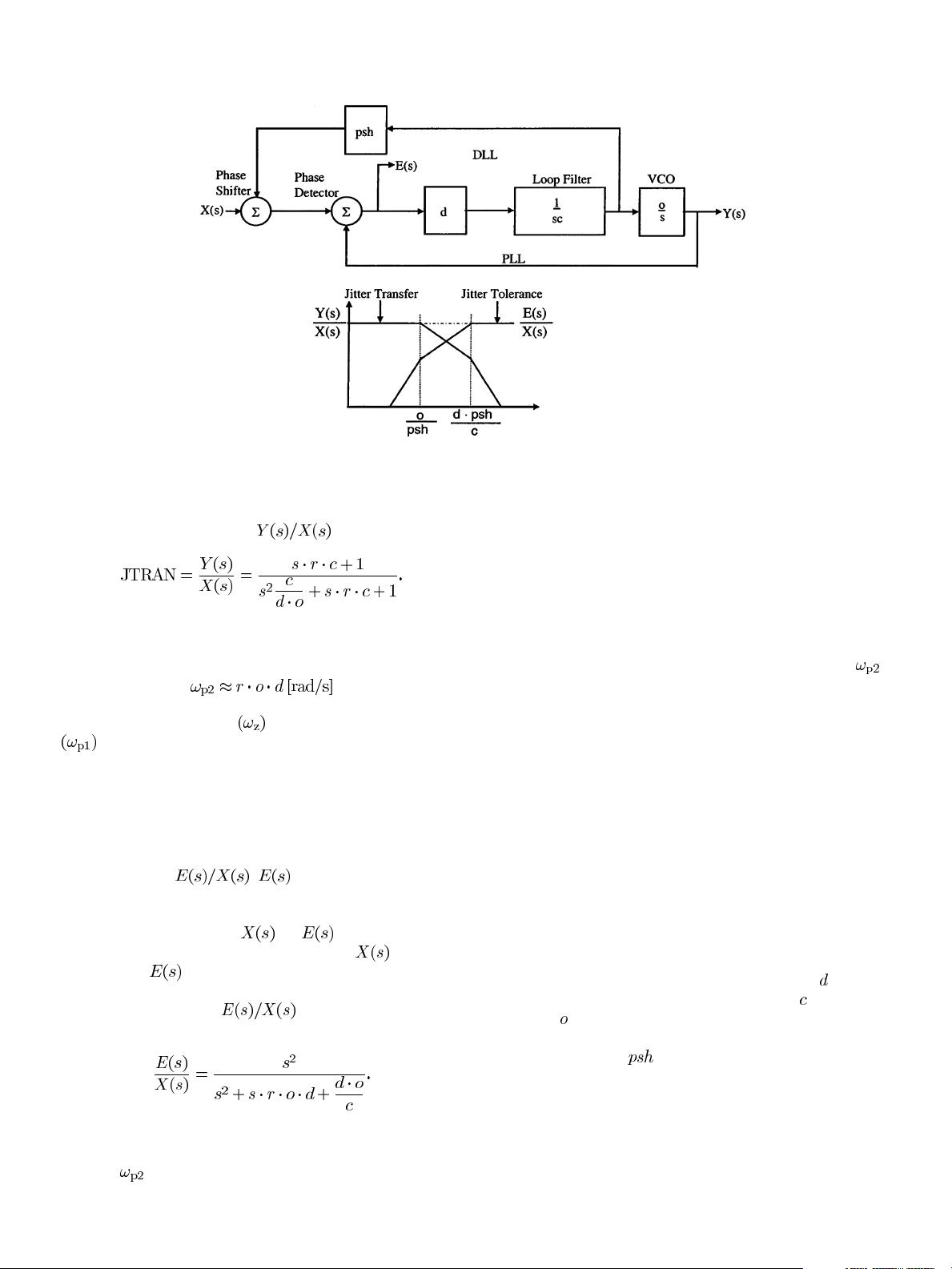

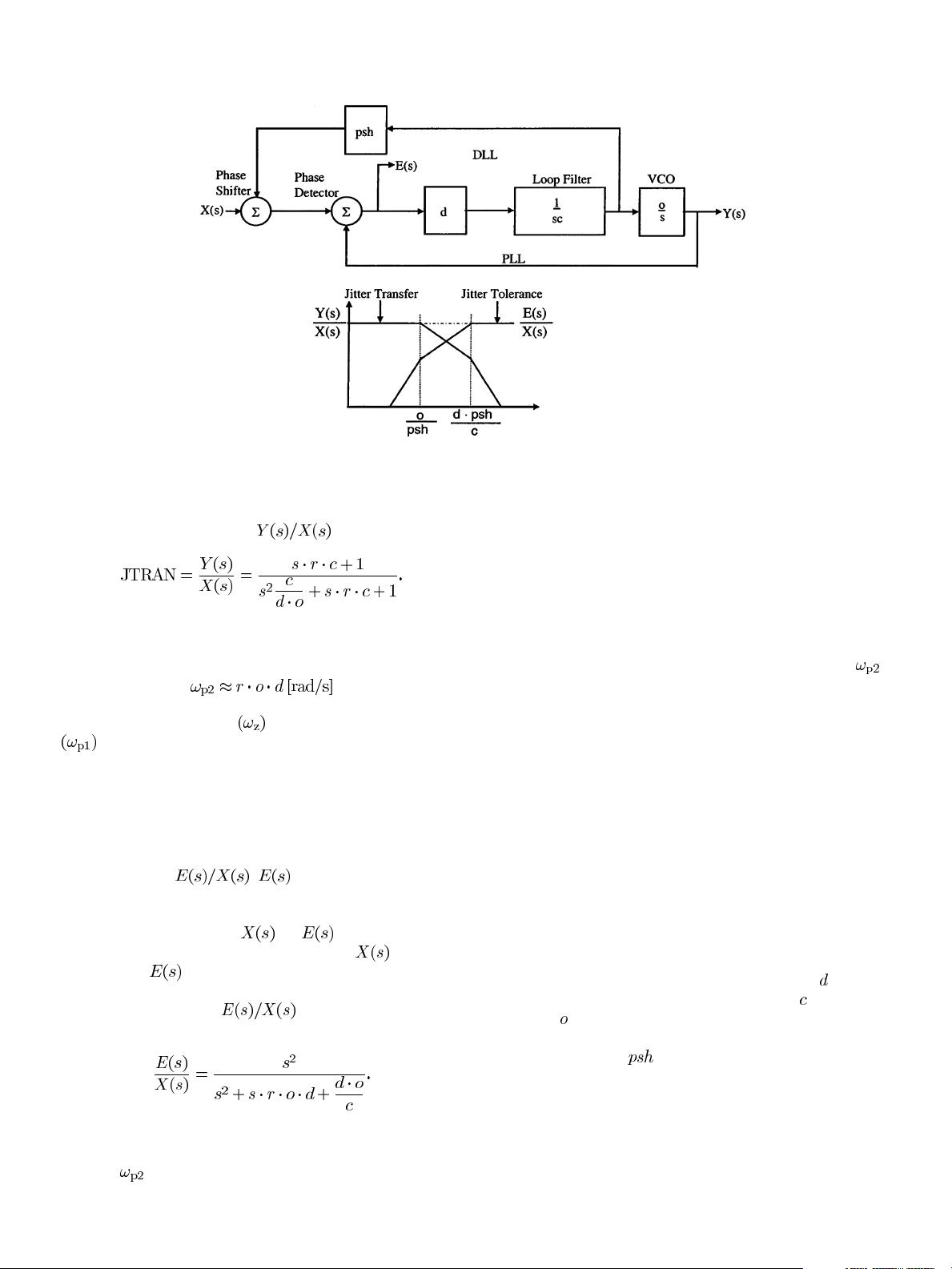

Fig. 4. Small-signal model of D/PLL.

model of Fig. 3. First, JTRAN is given by the overall transfer

function from input to output,

(1)

This displays the required low-pass response and starts to roll

off at the higher of the two closed-loop poles given by

(2)

since the closed-loop zero

and the first closed-loop pole

practically cancel. Exact cancellation, however, would re-

quire infinite loop gain and the extent to which the zero and pole

do not cancel leads to peaking (JPEAK) in the transfer function

where the gain is greater than one. This is unavoidable with this

architecture but can be minimized by using a large loop filter

capacitor.

The JTOL performance can be evaluated by deriving the

transfer function,

. is the phase error between

the input data and the recovered clock. If this error exceeds a

certain limit, a retiming error will occur. The circuit displays

a high-pass function from

to , which means that

low-frequency jitter appearing at the input,

, is greatly

attenuated at

, which, in turn, means that large amounts

of low-frequency jitter can be tolerated. The JTOL is then

inversely proportional to

, which is plotted in Fig. 3

and given by

(3)

This shows the expected high-pass response with the JTOL

corner frequency below which tolerance starts to improve, given

again by

. Above this high-pass corner frequency, the error

transfer is unity and so only small amounts of high-frequency

jitter may be tolerated before retiming errors are committed.

In practice, the high-frequency JTOL is determined by the fol-

lowing: static phase error in the PLL; eye closure in the input

data signal; and jitter generation in the PLL. These details are

beyond the scope of this paper and will not be further developed

here.

The problems with this architecture are now apparent. First,

good JTRAN performance requires a narrowband PLL, while

good JTOL performance requires a wideband PLL, but the

JTRAN and JTOL corner frequencies are both set by

,

making it difficult to meet both specifications simultaneously.

For example, for the OC48 data rate, the SONET standard calls

for a JTRAN corner frequency of 2 MHz and a JTOL corner

frequency of 1 MHz, which means that the PLL bandwidth

must be maintained between these values over all conditions

of process, voltage, and temperature (PVT). Second, because

the closed-loop zero occurs before the first closed-loop pole,

JPEAK greater than 0 dB is unavoidable.

III. D

ELAY- AND PHASE-LOCKED LOOP (D/PLL)

The D/PLL architecture [2] provides significant performance

improvement over the standard second-order loop. Fig. 4 shows

a small-signal model. It consists of two loops: 1) a PLL con-

sisting of a PD and a CP with a combined gain of

[A/rad],

a loop filter implemented with a single capacitor

and a VCO

with a gain

[rad/Vs]; and 2) a delay-locked loop (DLL) that

shares the PD and CP with the PLL and also has a phase shifter

(PSH) with a gain of

[rad/V] in the loop. The PLL is a

second-order loop with narrow bandwidth, while the DLL is

a first-order loop with much wider bandwidth. This architec-

ture is developed in [2], which focuses on the jitter transfer per-

formance and phase/frequency acquisition time. In this paper,

we focus on the following: the decoupling of the jitter transfer

and jitter tolerance corner frequencies; implementing a contin-

uous-rate CDR with this architecture; and, finally, incorporating

a frequency-locked loop (FLL) for wideband operation.