MAX+Plus II软件操作指南:设计半加器

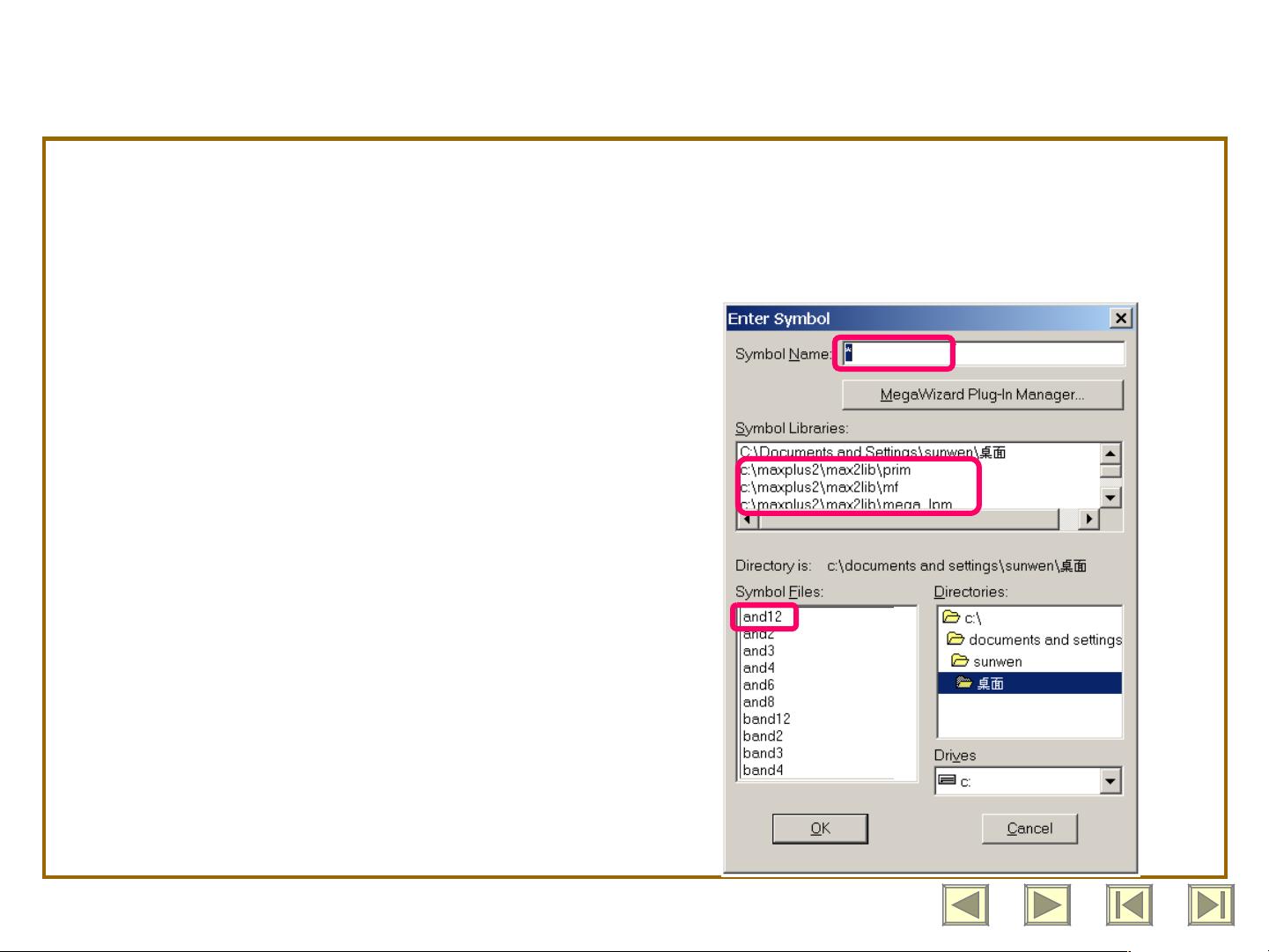

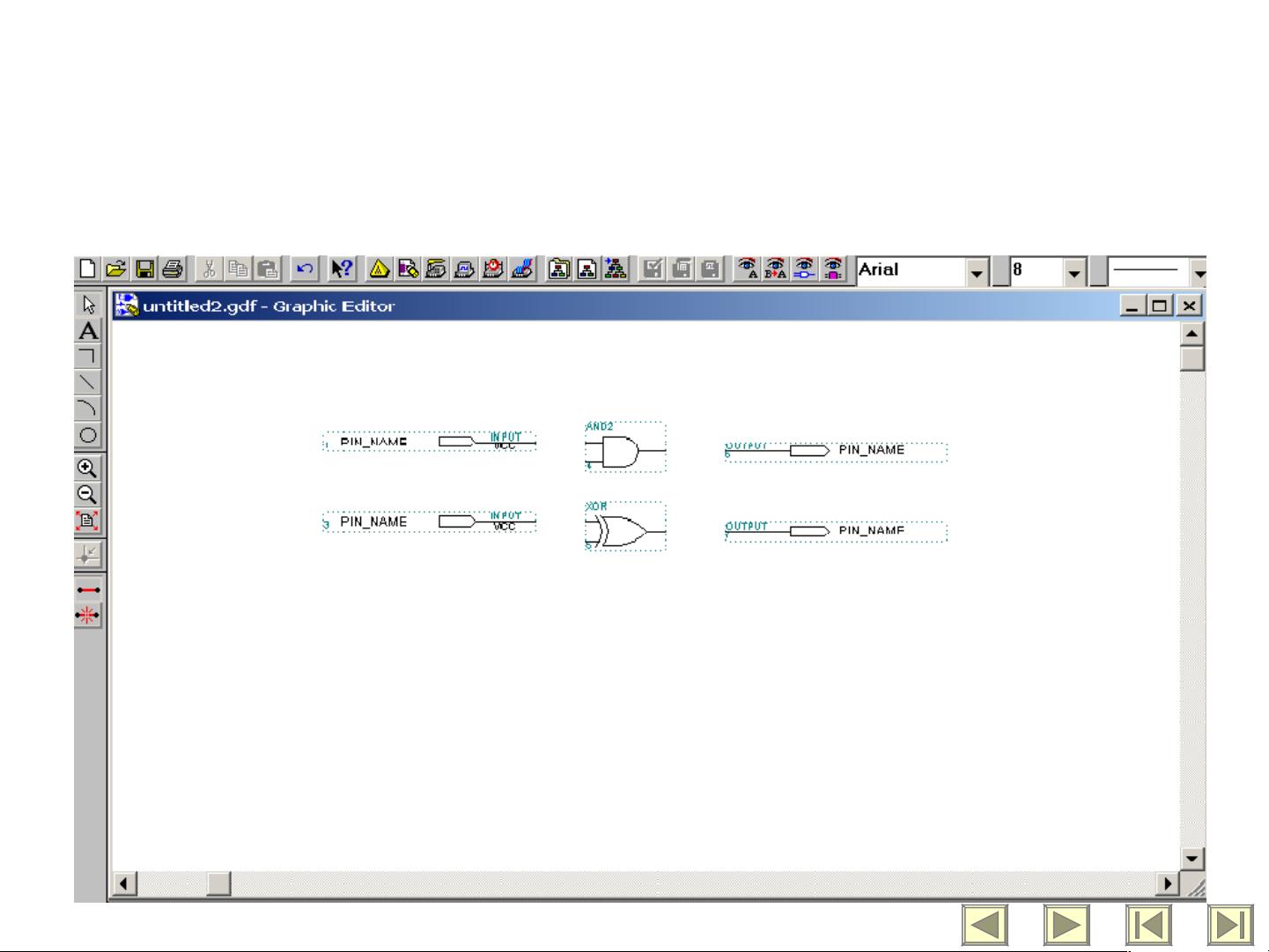

"MAX+Plus II是一款经典的EDA(电子设计自动化)工具,主要用于 FPGA(现场可编程门阵列)的设计和编程。本文将详细介绍如何使用MAX+Plus II进行设计输入,以及电路的编译与适配过程。" 在使用MAX+Plus II进行设计输入时,首先需要创建一个新的文件。这个过程可以通过软件菜单栏选择“File” -> “New”,然后在弹出的对话框中选择“Graphic Editor file”并设置文件扩展名为.gdf。创建新文件后,会打开Graphic Editor窗口,进入电路设计状态。 设计输入的关键步骤包括输入逻辑功能图元。以设计半加器为例,我们需要从元件库中选择必要的逻辑门,如与门(AND)和异或门(XOR),以及输入和输出端口。放置器件时,可以直接双击工作区或通过“Symbol” -> “Enter Symbol”菜单。若需复制器件,可以按住Ctrl键拖动。在连接器件时,将鼠标靠近引脚,光标变为十字,然后按住右键拖动绘制连线。输入/输出端口的标记则通过双击“PIN-NAME”并输入标记符完成,例如半加器的输入端标记为A、B,输出端标记为S、C。 在设计完成后,保存文件至关重要。通过“File” -> “Save As”保存文件,指定文件名(如half_adder.gdf)和保存位置。注意,某些MAX+Plus II版本不支持中文路径,因此在保存时应避免使用含有中文字符的路径。 为了验证设计的正确性,需要进行错误检查。选择“File” -> “Project” -> “Save&Check”会保存当前设计并执行错误检查。这一过程能帮助识别设计中的问题,确保逻辑功能的正确实现。 接下来是电路的编译与适配阶段,这是FPGA设计流程中的关键步骤。编译通常包括逻辑综合、映射和布局布线等步骤,目的是将逻辑设计转化为适合目标FPGA结构的配置数据。适配则是根据FPGA的资源限制优化设计,确保设计能在实际硬件上正确运行。在MAX+Plus II中,用户可以使用相应的菜单选项启动编译和适配流程,生成最终的编程文件,用于对FPGA进行编程。 总结起来,MAX+Plus II提供了一个直观的图形界面,使得用户能够方便地进行FPGA设计。从创建新文件、输入逻辑图元、保存和检查错误,到最后的编译和适配,每个步骤都是FPGA设计不可或缺的部分。了解并熟练掌握这些操作,对于进行有效的FPGA设计至关重要。

剩余25页未读,继续阅读

- 粉丝: 8

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- IPQ4019 QSDK开源代码资源包发布

- 高频组电赛必备:掌握数字频率合成模块要点

- ThinkPHP开发的仿微博系统功能解析

- 掌握Objective-C并发编程:NSOperation与NSOperationQueue精讲

- Navicat160 Premium 安装教程与说明

- SpringBoot+Vue开发的休闲娱乐票务代理平台

- 数据库课程设计:实现与优化方法探讨

- 电赛高频模块攻略:掌握移相网络的关键技术

- PHP简易简历系统教程与源码分享

- Java聊天室程序设计:实现用户互动与服务器监控

- Bootstrap后台管理页面模板(纯前端实现)

- 校园订餐系统项目源码解析:深入Spring框架核心原理

- 探索Spring核心原理的JavaWeb校园管理系统源码

- ios苹果APP从开发到上架的完整流程指南

- 深入理解Spring核心原理与源码解析

- 掌握Python函数与模块使用技巧

信息提交成功

信息提交成功