三星K4S641632C:高性能CMOS同步DRAM技术详解

需积分: 13 199 浏览量

更新于2024-07-10

收藏 1.13MB PDF 举报

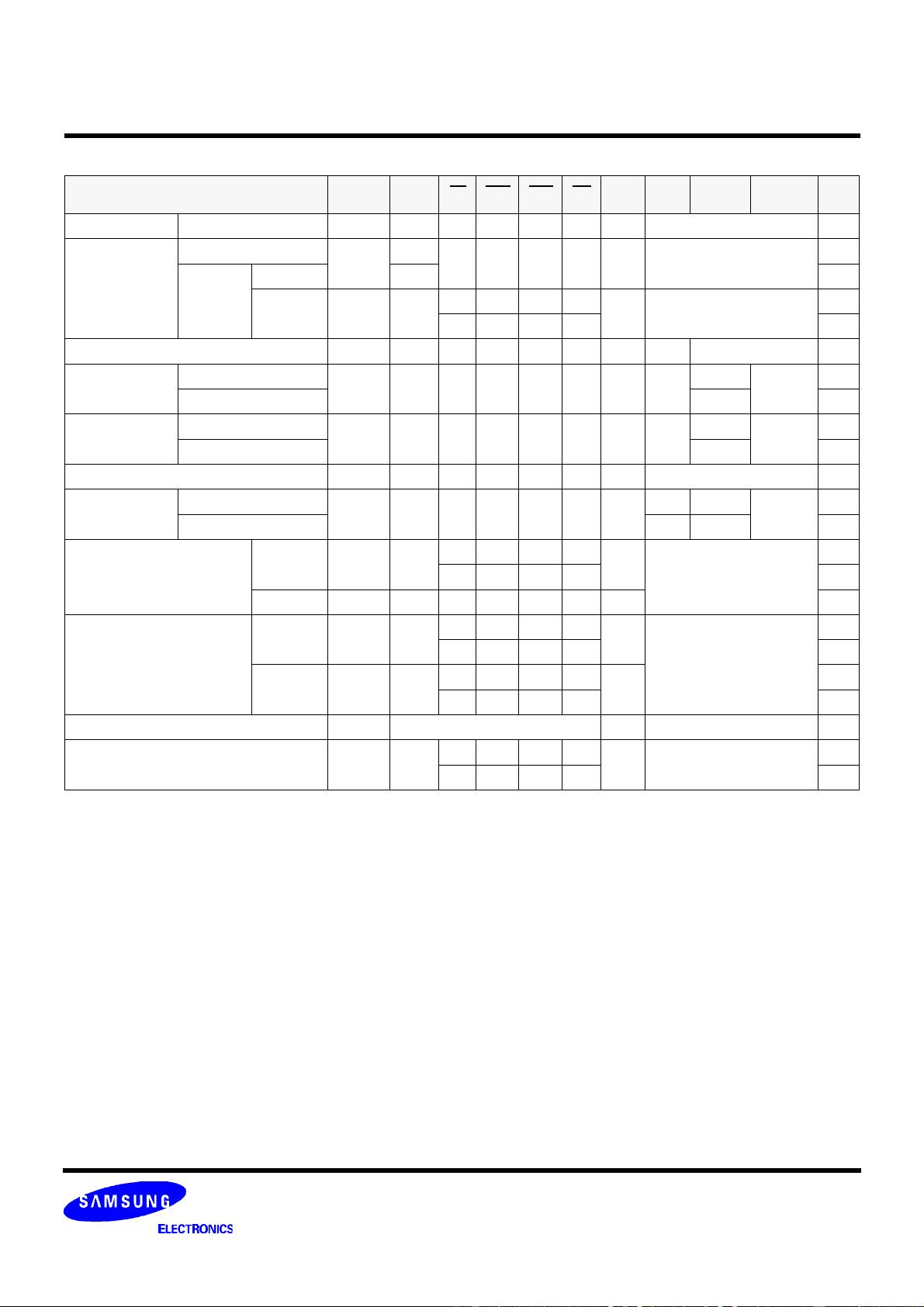

"Samsung K4S641632C是一款由三星制造的67,108,864位同步高速动态随机存取内存(SDRAM),组织形式为4个1,048,576字×16位,采用三星高性能CMOS技术。"

K4S641632C是一款高性能的同步DRAM芯片,其设计特点在于同步性,能够通过系统时钟实现精确的周期控制。这意味着所有的输入/输出操作可以在每个时钟周期内完成,提高了数据传输的速度和效率。这款芯片具有广泛的运行频率范围、可编程的突发长度以及可编程的延迟,使其适用于各种高带宽、高性能内存系统应用。

该芯片的主要特性包括:

1. **符合JEDEC标准的3.3V电源供应**:这是DRAM芯片的行业标准电压,确保了与多种系统的兼容性。

2. **低电压晶体管逻辑(LVTTL)兼容的复用地址**:这意味着它能够与使用LVTTL电平的系统接口,提高了互操作性。

3. **四银行操作**:通过四个独立的内存银行,芯片可以并行处理多个请求,进一步提升性能。

4. **模式寄存器设置(MRS)周期与地址键程序**:允许用户配置芯片的内部参数,如CAS延迟、突发长度和类型等。

5. **CAS延迟支持2&3**:CAS(列地址选择)延迟是指从时钟脉冲到数据有效的时间,可调的延迟选项提供了灵活性。

6. **突发长度支持1,2,4,8及全页**:突发模式允许连续读取或写入多个数据,全页模式允许一次性访问整个页面的数据。

7. **突发类型包括顺序和交错**:顺序模式下数据按顺序传输,交错模式下数据交错传输,两者都提高了数据传输速率。

8. **所有输入在系统时钟的正沿采样**:确保数据的准确同步。

9. **突发读取和单位写操作**:在突发模式下读取数据,同时支持单位写入操作。

10. **数据选择门(DQM)掩码功能**:允许选择性地禁止对某些数据位的写入,增加了数据管理的灵活性。

11. **自动和自我刷新功能**:自动刷新机制确保数据在长时间无操作后仍然保持,64ms的刷新周期(4K周期)是标准的DRAM刷新时间。

此外,K4S641632C还包括了感测放大器、输出缓冲器、I/O控制、列解码器等功能模块,这些都是SDRAM正常工作所必需的硬件结构。感测放大器用于读取存储单元中的数据,输出缓冲器负责将内部数据转换为适合外部总线的信号,列解码器则根据地址选择相应的数据线。

Samsung K4S641632C是一款高度集成、可配置且性能出色的DRAM芯片,适合于需要高速、高带宽数据处理的系统,如服务器、工作站、图形处理器等应用场景。

2010-07-22 上传

2023-08-02 上传

2010-12-27 上传

2023-05-26 上传

2023-10-01 上传

2023-05-13 上传

2023-07-12 上传

2023-06-21 上传

2023-04-29 上传

2023-06-08 上传

LC灵灵

- 粉丝: 1

- 资源: 261

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析