使用Vivado设计AXI USB 2.0设备FPGA IP核心

需积分: 10 39 浏览量

更新于2024-06-29

收藏 1.3MB PDF 举报

"AXI Universal Serial Bus (USB) 2.0 Device v5.0 LogiCORE IP Product Guide Vivado Design Suite PG137 November 18, 2015"

Xilinx的AXI USB 2.0 Device v5.0是一款专为FPGA设计的高速USB 2.0控制器知识产权(IP),它基于先进的AXI(Advanced eXtensible Interface)总线标准。AXI是Xilinx的一种高性能、低延迟的片上互连架构,广泛用于其FPGA和SoC产品中,为系统级设计提供了高效的数据传输能力。

**主要知识点**

1. **AXI总线**:AXI是一种开放的接口规范,用于连接处理器、内存、外设等不同组件。它包括多个协议变体,如AXI4、AXI4-Lite等,提供单向或双向数据传输,并支持多通道和事务层包(TLP)处理,以优化带宽和资源利用率。

2. **USB 2.0技术**:USB 2.0是通用串行总线的一个版本,提供最高480Mbps的传输速度(称为High-Speed模式)。此IP实现了USB 2.0规范,使得FPGA可以作为USB设备,与主机进行高速数据交换。

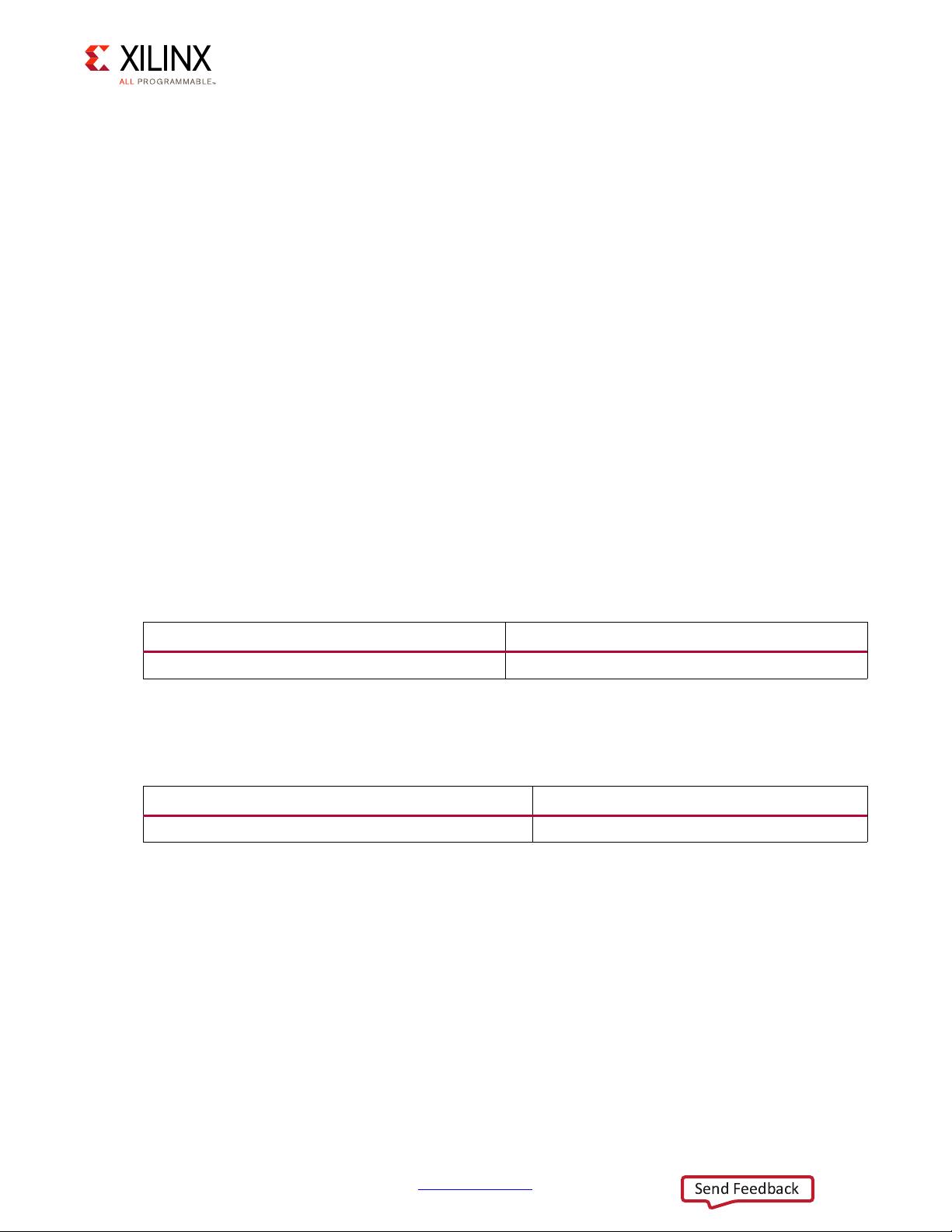

3. **IP Facts**:AXI USB 2.0 Device IP提供了关键的功能描述,包括其应用、不支持的特性以及授权和订购信息。这帮助用户了解IP的核心特性和使用条件。

4. **功能描述**:IP提供USB设备端的功能,支持高速模式,适用于各种应用,如数据采集、嵌入式系统通信等。它还列出了不支持的特性,以指导用户在设计时避免潜在问题。

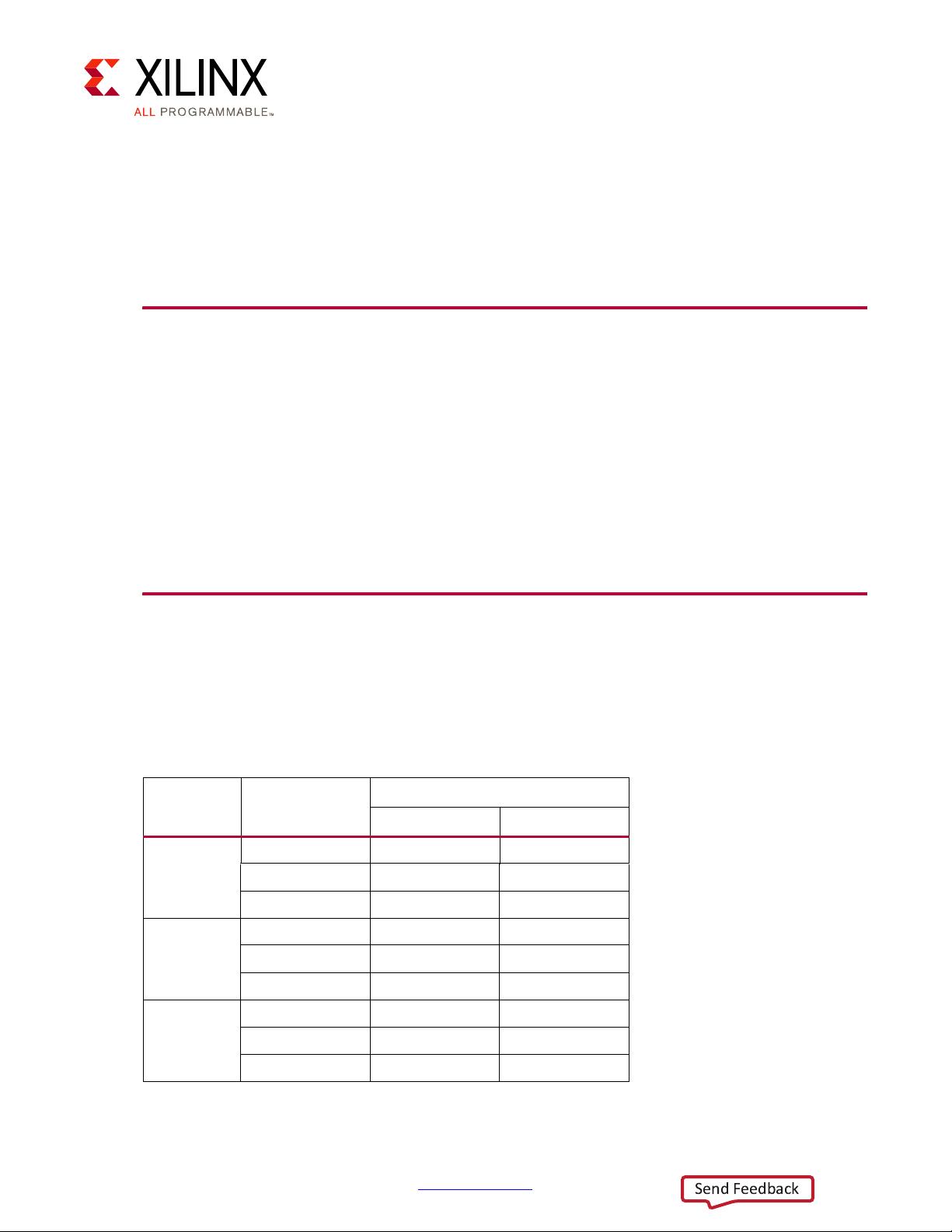

5. **资源利用率**:在设计阶段,IP的资源消耗是至关重要的。AXI USB 2.0 Device IP的资源利用情况包括逻辑单元、触发器、I/O引脚等,这些信息对于评估设计是否适合特定FPGA平台至关重要。

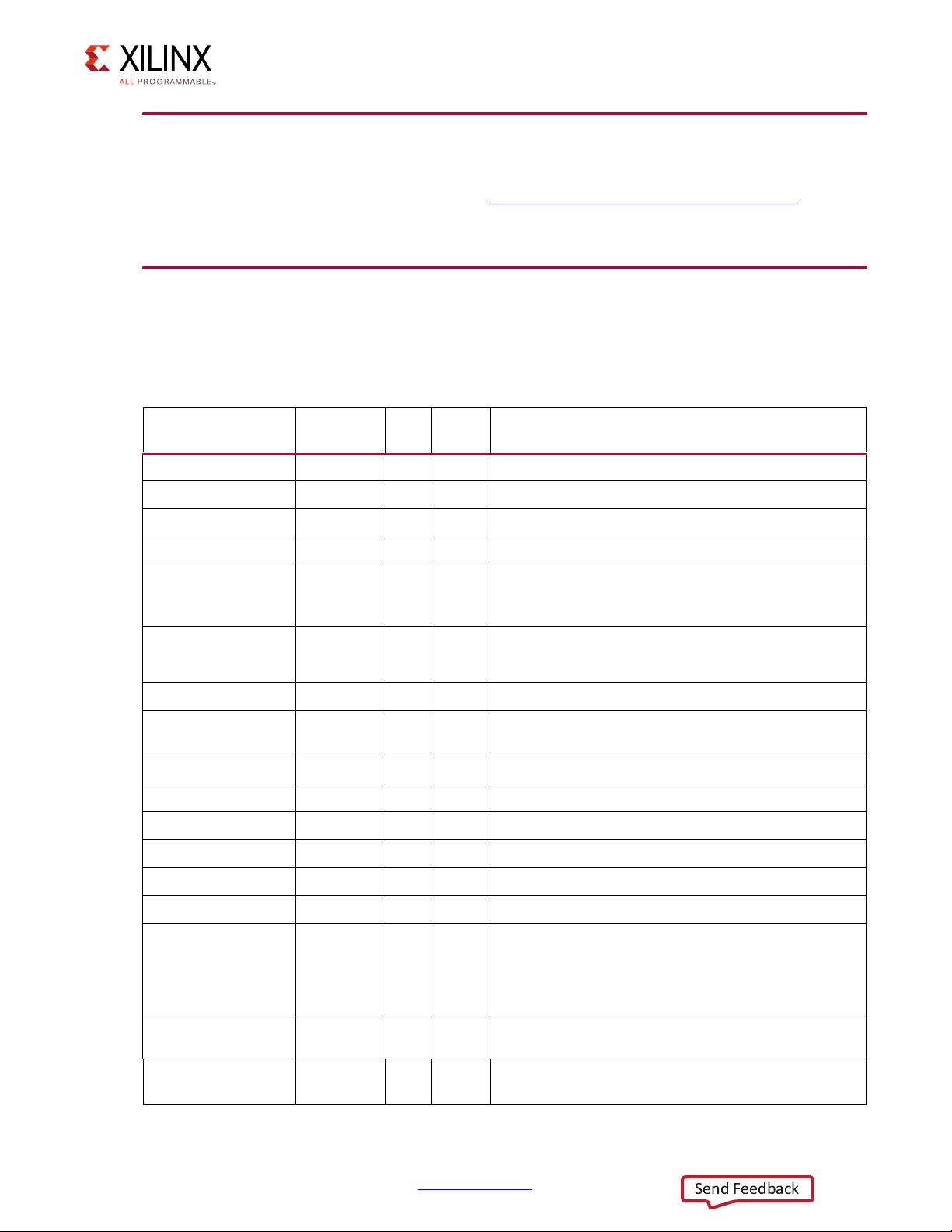

6. **时钟和复位管理**:章节介绍了IP如何处理时钟和复位信号,这是确保USB协议正确运行的关键。时钟管理涉及时钟域交叉和同步,而复位管理则涉及到初始化和恢复操作。

7. **编程序列**:IP的编程顺序包括了如何配置IP以达到正确工作状态的步骤,这对实现和调试至关重要。

8. **协议描述**:在低功耗模式(ULPI,Universal Serial Peripheral Interface)下,IP如何处理USB协议进行了详细说明,包括数据包的接收和发送,以及错误处理机制。

9. **设计流程步骤**:从自定义和生成IP到约束、仿真、综合和实现,本章详细描述了使用Vivado Design Suite开发基于此IP的设计的整个流程。

10. **示例设计**:为了帮助用户快速上手,IP提供了一个示例设计,包含了实现和仿真指南,使开发者能够验证IP的功能并进行测试。

11. **测试平台**:IP的测试平台用于验证其正确性,这对于确保设计满足性能和功能需求非常重要。

12. **迁移和升级**:指南提供了从旧版本工具迁移到Vivado Design Suite以及在该套件内升级IP的方法。

13. **调试**:附录B提供了在Xilinx.com上寻找帮助的途径,以及可用的调试工具,帮助用户解决设计中遇到的问题。

这个AXI USB 2.0 Device v5.0 IP是实现FPGA中高速USB通信的关键组件,它结合了AXI总线的高性能和USB 2.0的广泛应用,为开发者提供了强大的设计基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-10-26 上传

2022-09-19 上传

2018-10-30 上传

2009-11-17 上传

2016-11-30 上传

点击了解资源详情

2024-12-20 上传

hanshuizhizi

- 粉丝: 53

- 资源: 31

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境