Quartus II 实验:1位全加器的原理图设计与仿真

需积分: 17 14 浏览量

更新于2024-08-12

2

收藏 2.25MB DOCX 举报

"该文档是关于使用EDA工具Quartus 13.0进行1位全加器仿真的教程,适合数字电子技术初学者。实验旨在掌握Quartus II的原理图输入、编译、仿真和下载操作,设计并验证全加器功能,以及熟悉EDA实验箱的使用。实验主要包括设计全加器的真值表和逻辑图,使用Quartus II创建工程和图形输入文件,进行功能和时序仿真,并通过EDA实验箱进行硬件验证。在实验过程中,强调了未使用的引脚应设为三态输入以减少噪声干扰,并通过Tcl脚本进行引脚分配。实验结果通过时序和功能仿真进行分析,验证设计的正确性和延迟现象。"

在Quartus 13.0中设计1位全加器的过程包括以下步骤:

1. **创建工程项目**:首先需要在Quartus II中新建一个工程,为1位全加器设计指定一个文件夹和工程名称,并选择合适的芯片模型。

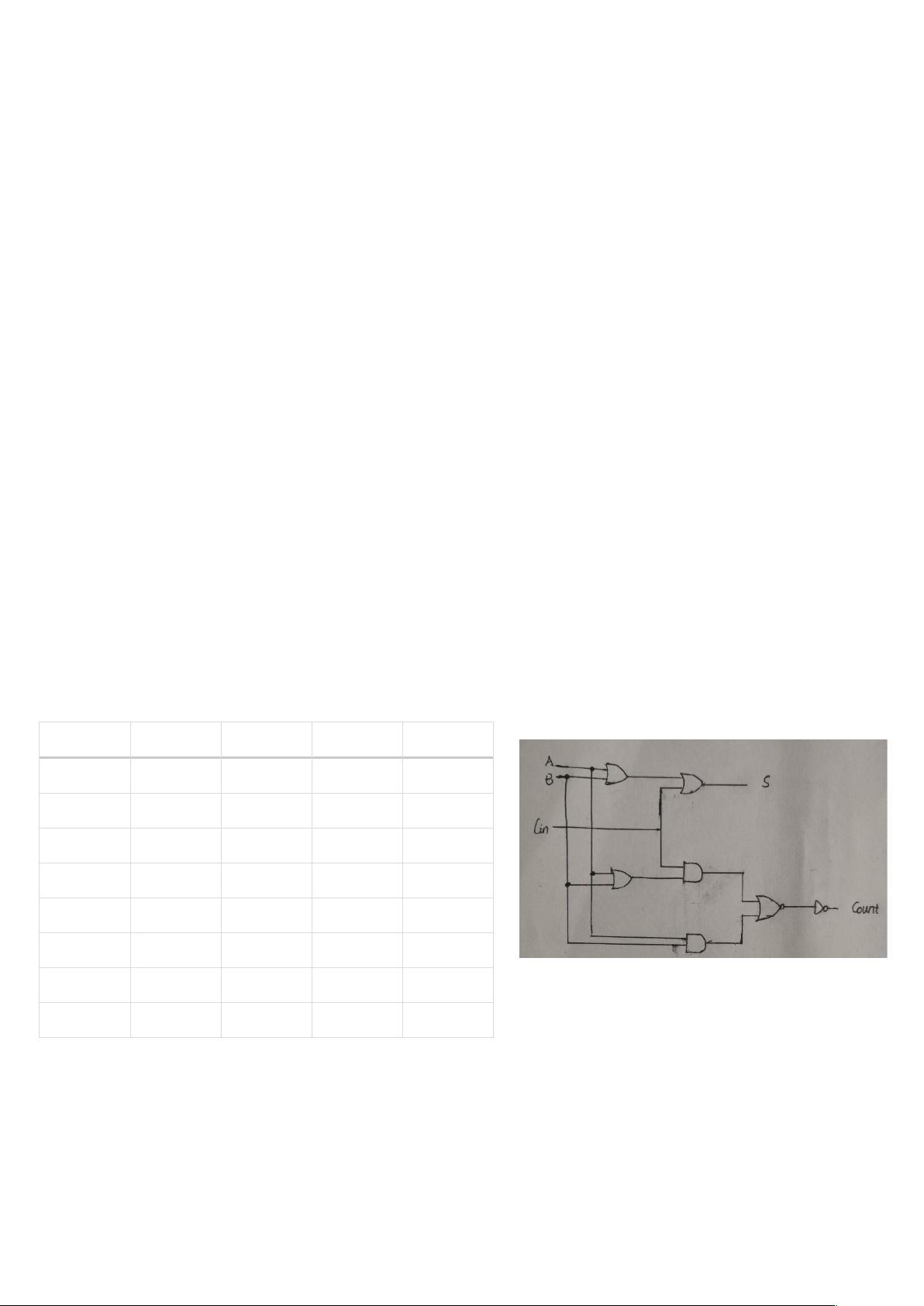

2. **编辑设计文件**:使用原理图输入法,添加必要的逻辑门组件,如与非门(AND-NOT)和或门(OR)来构建全加器电路。全加器有三个输入端A、B和进位输入CI,以及两个输出端S(和数)和Count(进位输出)。确保所有输入输出引脚正确连接。

3. **真值表**:列出全加器的真值表,显示所有可能的输入组合及其对应的输出。全加器的逻辑关系表达式是基于这个真值表得出的。

4. **编译**:对设计进行编译,Quartus II将自动进行综合,将逻辑表达式转化为硬件门级描述。

5. **功能仿真**:运行功能仿真,观察输出是否与真值表一致。这可以通过设置不同的输入组合,查看波形图来完成。

6. **时序仿真**:进行时序仿真,分析延迟时间和潜在的竞争冒险现象。如果发现不符合预期,需要调整设计。

7. **引脚分配**:通过Tcl脚本进行引脚分配,确保输入和输出引脚在实际硬件上的正确连接。

8. **硬件验证**:连接EDA实验箱,将编译后的设计下载到实验箱中,进行硬件级别的验证,确认电路在真实环境中的工作情况。

实验总结中提到,通过这次实验,学习了Quartus II的使用流程,加深了对全加器功能的理解。时序仿真揭示了输出的延迟以及可能出现的毛刺现象,这些都是数字电路设计中常见的问题。此外,实验也巩固了理论知识,为后续更复杂的数字系统设计打下了基础。

408 浏览量

297 浏览量

119 浏览量

150 浏览量

5075 浏览量

361 浏览量

2022-11-29 上传

321 浏览量

310 浏览量

有术无道

- 粉丝: 19

最新资源

- A7Demo.appstudio:探索JavaScript应用开发

- 百度地图范围内的标注点技术实现

- Foobar2000绿色汉化版:全面提升音频播放体验

- Rhythm Core .NET库:字符串与集合扩展方法详解

- 深入了解Tomcat源码及其依赖包结构

- 物流节约里程法的文档整理与实践分享

- NUnit3.vsix:快速安装NUnit三件套到VS2017及以上版本

- JQuery核心函数使用速查手册详解

- 多种风格的Select下拉框美化插件及其js代码下载

- Mac用户必备:SmartSVN版本控制工具介绍

- ELTE IK Web编程与Web开发课程内容详解

- QuartusII环境下的Verilog锁相环实现

- 横版过关游戏完整VC源码及资源包

- MVC后台管理框架2021版:源码与代码生成器详解

- 宗成庆主讲的自然语言理解课程PPT解析

- Memcached与Tomcat会话共享与Kryo序列化配置指南