EDA技术详解:ASIC与FPGA设计集成,VHDL特点与综合流程

在数字逻辑系统设计的EDA(电子设计自动化)中,EDA技术与ASIC(应用专用集成电路)设计和FPGA(现场可编程门阵列)开发密切相关。这些技术共同构成了现代电子设计的核心流程。首先,EDA技术旨在通过软硬件集成,实现从概念设计到实际硬件的无缝过渡,使得设计师可以灵活地在FPGA和ASIC之间选择,根据项目需求和成本效益进行权衡。

FPGA和CPLD(复杂可编程逻辑器件)作为可编程ASIC的代表,允许设计师在设计初期进行原型验证和快速迭代,而在后期阶段,当设计成熟后,可以选择将其转化为定制化的ASIC以提高性能和降低成本。VHDL(可综合硬件描述语言)在此过程中扮演关键角色,它作为一种高级描述语言,具有可移植性和独立性,与基于CPU的机器代码不同,VHDL可以直接映射到硬件,无需依赖特定硬件平台。

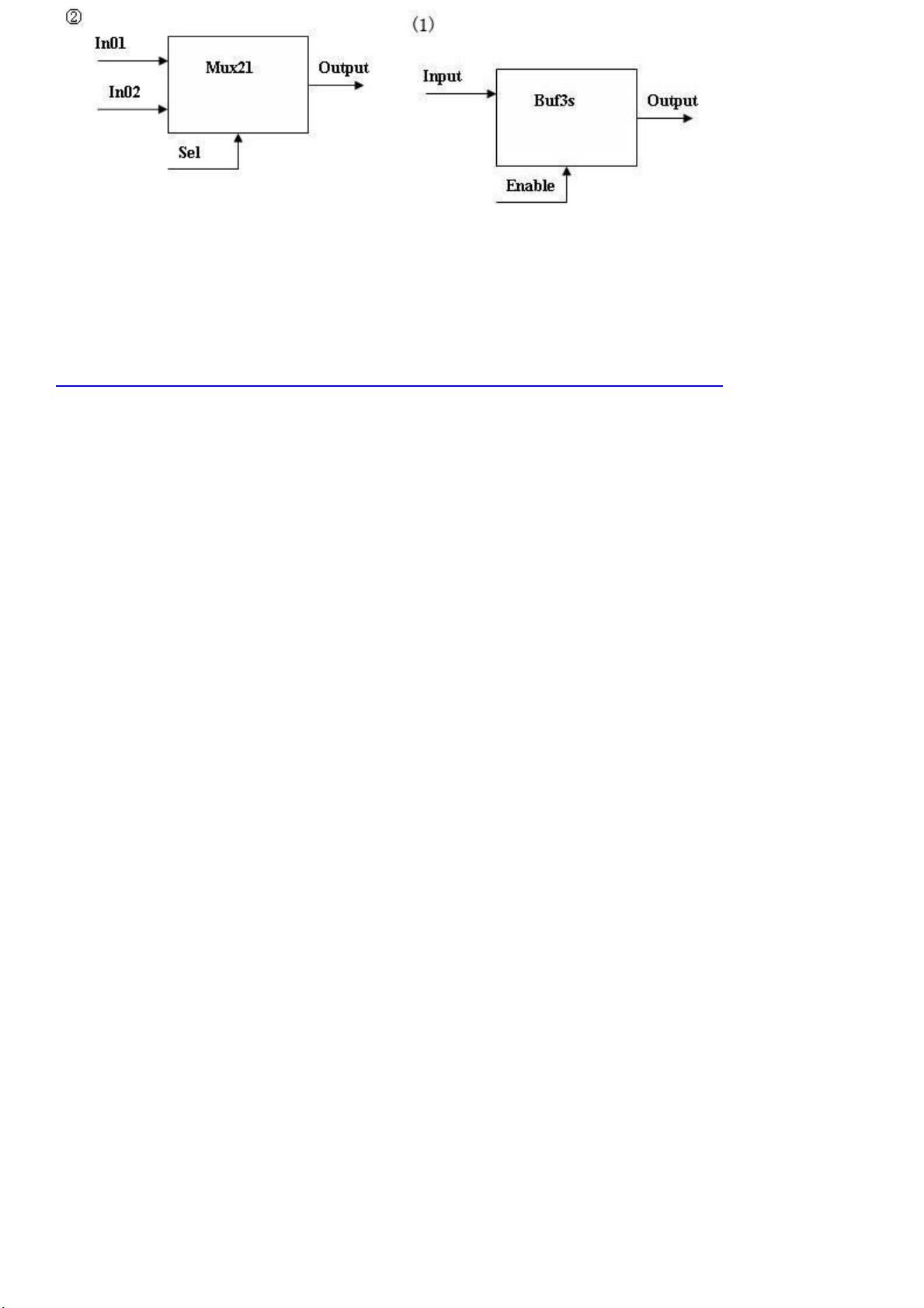

综合在EDA中占据核心地位,它是将高层次的设计描述逐步转化为具体电路实现的过程。综合可以分为多种类型,如自然语言综合、行为综合、逻辑综合以及版图综合。自然语言综合是从自然语言描述到VHDL的转换,行为综合是从算法描述到RTL(寄存器传输级)的转变,逻辑综合则是将RTL级转换为逻辑门级别,而版图综合则针对ASIC或FPGA的具体布局进行设计。

自顶向下的设计方法在EDA中尤为重要,它强调从系统级的设计思想开始,逐步细化至各个模块和子系统,然后逐级向下实现。这种方法的优势在于它能够保证设计的整体性和一致性,同时允许设计师在设计过程中灵活调整,适应不断变化的需求。通过自顶向下设计,设计师可以从抽象层次把握系统全局,确保各个部分的协同工作,提高设计效率和质量。

综合器在这一过程中起着至关重要的作用,它不仅负责将VHDL代码转化为硬件实现,还依赖于工艺库和约束条件信息,以优化设计过程并确保最终产品的性能和可靠性。综合器的智能性和灵活性是电子设计自动化不可或缺的一部分,它使得硬件设计更加高效和精确,推动了现代电子技术的发展。

2020-10-21 上传

点击了解资源详情

143 浏览量

点击了解资源详情

点击了解资源详情

120 浏览量

ping19910520

- 粉丝: 0

- 资源: 3

最新资源

- 《Linux服务器搭建实战详解》-pdf

- java爬虫的实例代码+java清除空文件夹的代码

- Project1:使用HTML,CSS和引导程序创建的响应式投资组合网页

- Catfish(鲶鱼) Blog v1.1.9

- ROG-Phone-2-Switch-WW-Stock-ROM

- 社交媒体演示

- gatsby-shopify-toy-store-test

- 使用MATLAB分析车队测试数据:在线讲座“使用MATLAB分析车队测试数据”中的文件-matlab开发

- 汽车销售管理系统-毕业设计

- 台达A2伺服说明说.rar

- 商品销售系统源码.rar

- c33

- 校无忧人事工资系统 v2.5

- react-contentful-nextjs-tutorial:使用适用于SSR或Jamstack的NextJS React x Contentful

- 视频编码器

- Rapla, resource scheduling-开源