Altera Cyclone IV DDR2 走线设计与优化策略

需积分: 9 158 浏览量

更新于2024-09-08

收藏 1.46MB DOC 举报

"本文档是关于 CycloneIV FPGA 中 DDRII 内存接口的走线设计笔记,主要讨论了如何优化 DDR2 的布线策略以确保信号完整性,并且这些规则也适用于更高速度的 DDR3 设计。"

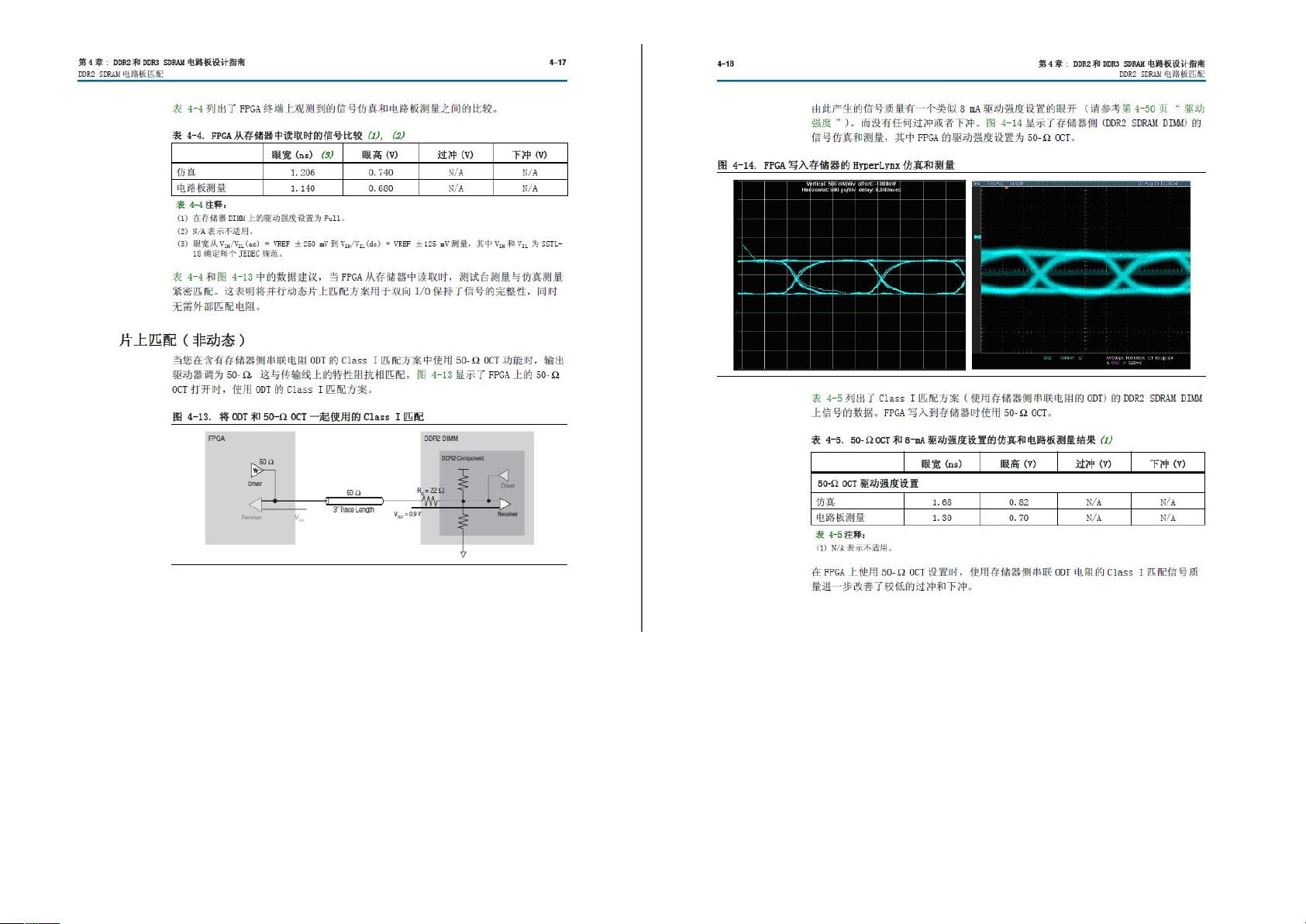

在 CycloneIV FPGA 中,DDRII 走线设计是一项关键任务,因为它直接影响到内存系统的性能和稳定性。首先,每个 FPGA 的边缘,如 BANK1 和 BANK2,都配备了一组 Rup 和 Rdn 支持串行阻抗匹配,这样可以省去外部的串行电阻。在设计过程中,应当将 RUP 和 RDN 引脚设置为保留状态,防止 Quartus 自动分配给 DDR2 控制器,而在 PCB 上连接 50 欧姆的电阻到 1.8V(pullup)和 GND(pulldown)。

根据 Altera 的推荐设计,结合 RsOCT(接收端串行输出钳位技术)和 DDR 内存上的 ODT(On-Die Termination)可以有效地提高信号质量。设计策略如下:

1. 使用 RsOCT 结合 ODT,适用于 DQ、DM 和 DQS 信号线。

2. 不需要额外的 VTT(电压跟踪终端)设计。

3. 采用 6 层 PCB 板进行布线,以实现严格的等长布线。

4. 信号线长度应尽可能短,最大不超过 2000mil(约 50.8mm)。

5. 相邻信号线之间的间距至少是线宽的 3 倍,理想情况下是 4 倍,以减少串扰。

6. 差分线的线宽和线间距均为 5mil。

7. 同一组内的相邻信号线间距为 12.8mil。

8. 应遵循 3W 规则(线中心间距不少于线宽的 3 倍),以减少电场干扰,降低串扰。

DDR2 接口包括 32 条数据线 (DATA0-DATA31),4 条 DATAMASK/SDQM (DQM0-DQM3) 以及 4 对数据 strobes (DQS0P/DQS0M-DQS3P/DQS3M)。这些信号线被分为四组(GROUPA-GROUPD),每组内的线长差异控制在特定范围内,以保证信号同步。此外,还有地址线 (ADDR0-ADDR15) 和其他控制信号线,它们也需要按照一定的规则进行布线。

在实际布板时,优先考虑差分对的走线,确保差分线对之间的线长误差小于 30mil,组内任意两条数据线长差异小于 50mil,所有组间任意两条线的差异不超过 100mil。这样的布局策略有助于保持信号同步,减少反射和串扰,从而提高系统性能。

总结来说,CycloneIV FPGA 的 DDRII 走线设计需要兼顾信号完整性、等长布线和串扰控制,通过合理的布局和布线策略,可以确保 DDR2 子系统在 400M 带宽下稳定运行,同时为更高速度的 DDR3 设计提供参考。

591 浏览量

457 浏览量

158 浏览量

2018-05-26 上传

2012-03-09 上传

271 浏览量

226 浏览量

2009-10-29 上传

326 浏览量

时空引力51151045

- 粉丝: 0

最新资源

- Matlab散斑形状变换技术介绍

- React Native原生导航解决方案:开源介绍及环境配置

- 使用HTML和CSS制作简历的实用指南

- Eclipse 3.6插件开发学习与API指南

- Android自定义弹出框的设计与实现

- POS机LCD12864液晶屏拆解与测试教程

- String_Finder:快速批量文件字符串替换解决方案

- MATLAB图形轴刻度标签偏移技术解析

- React应用入门教程:soar-financial-coaching

- EGEsort动态演示:计算机学院教学作业解析

- Q-Dir: 高效的文件管理与浏览工具

- 基于C++的NS2.35 VANET网络编程实践指南

- 洛达芯片协议检测工具:免拆机华强北AirPods芯片识别

- Python实现RSS媒体自动下载与更新工具

- TrueLaunchBar 7.4:功能全面的绿色任务栏增强工具

- 流片验证过的Verilog实现wishbone接口I2C总线