Modelsim 6.0 PLL仿真教程:20x40M倍频实战步骤

需积分: 25 153 浏览量

更新于2024-09-17

收藏 323KB PDF 举报

本文将详细介绍如何在Modelsim 6.0 SE版本下进行Altera公司的PLL (Phase-Locked Loop) 仿真,作者王晓斌基于实际操作步骤进行讲解,适用于Quartus II 4.2+SP1版本及Megacore技术。以下是一系列详细的仿真步骤:

1. **准备工作**:

- **PLL文件生成**:首先,在Quartus II中使用MegaWizard工具生成一个名为PLL.V的源代码文件,这是PLL设计的基本组成部分。

2. **Testbench编写**:

- 为了测试PLL的功能,需要编写一个名为Test_Pll.V的测试台(Testbench),用于与PLL模块交互并观察其行为。

3. **工程设置**:

- 在D盘上创建一个名为"Test"的文件夹,并通过File > New > Project命令创建一个新的Modelsim工程。工程设置包括项目名称(如"test")、位置(指向D:/test)以及库名("work")。

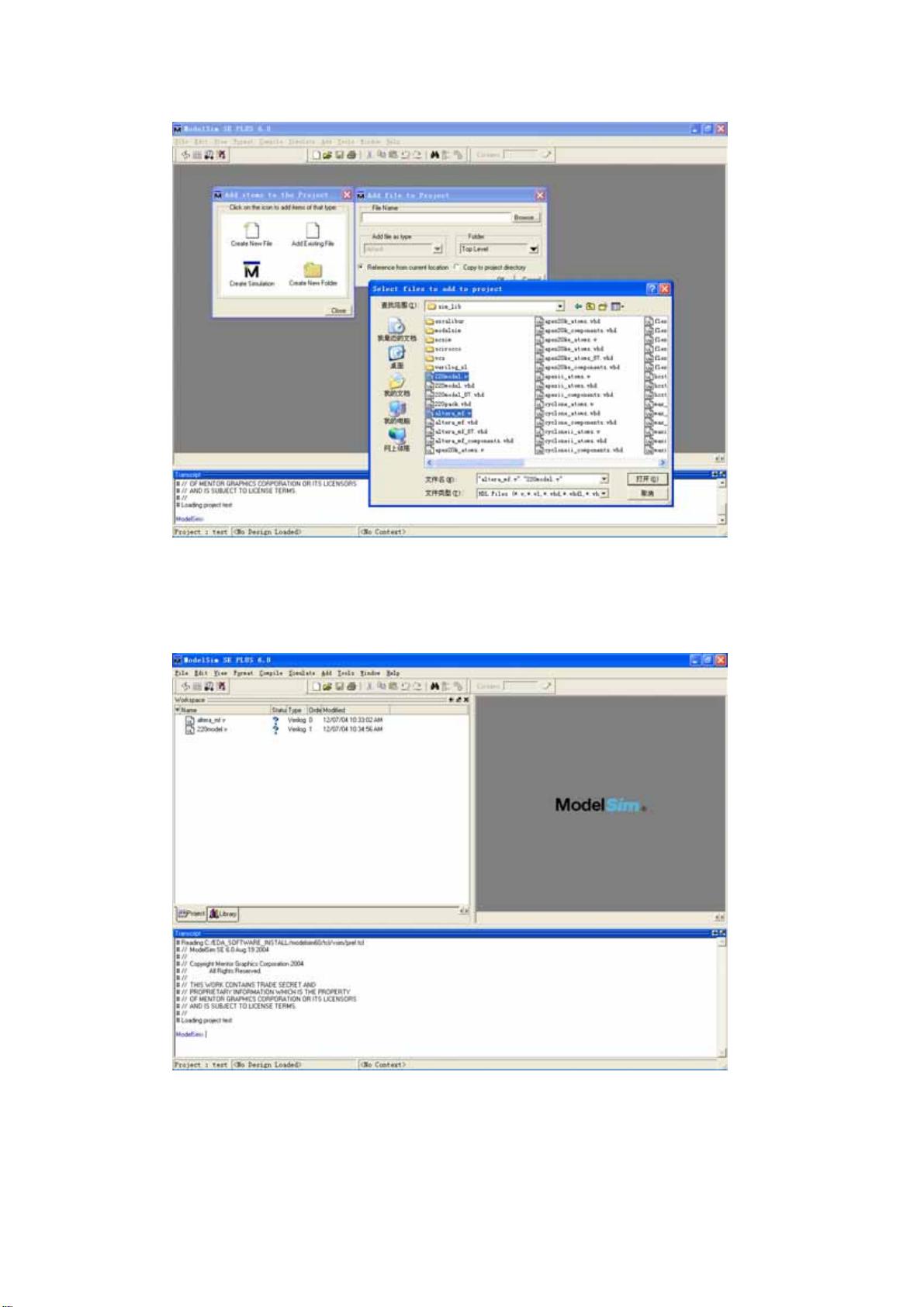

4. **添加文件**:

- 在项目管理器中,通过Add File to Project对话框导入PLL.V源码文件,以及altera_mf.v和220model.v这两个库文件,它们通常位于Quartus II安装目录下的eda\sim_lib子目录。

5. **编译与链接**:

- 执行Compile > compileAll命令来编译导入的源文件,确保没有语法错误或链接问题。

6. **设置仿真环境**:

- 需要在Testbench中配置合适的仿真信号和时钟,以便正确地模拟PLL的输入、反馈和锁定过程。

7. **运行仿真**:

- 启动仿真后,设置适当的时序参数,如时钟频率、模拟时间步长等,然后观察PLL是否能按照预期工作,如实现20x40M的倍频功能。

8. **分析结果**:

- 监视仿真波形,检查锁相环是否稳定锁定,输出信号是否满足设计要求,如频率准确度、抖动等指标。

9. **调试与优化**:

- 如发现异常,可能需要调整PLL的参数或者修改Testbench,进一步调试和优化。

10. **文档记录**:

- 记录整个仿真过程中的关键步骤和发现的问题,为以后的工作提供参考。

以上就是Modelsim 6.0 SE环境下进行Altera PLL仿真的完整流程,对于初学者或对PLL模块有深入研究的人来说,这是一个实用且详尽的指南。通过这些步骤,你可以更好地理解PLL的工作原理,并确保设计的正确性和性能。

135 浏览量

146 浏览量

191 浏览量

点击了解资源详情

250 浏览量

178 浏览量

135 浏览量

235 浏览量

xl46512c

- 粉丝: 2

- 资源: 68

最新资源

- 著名的GPS数据处理软件介绍.zip

- java笔试题算法-pulse:一个具有教学意义的Java/C++国际象棋引擎

- test-management-folder:测试文件夹

- 如何做精终端陈列

- 埃比尼泽即时现金

- testng:ng样圈ci

- PHP-Druid:具有PECL扩展名PHP的Druid驱动程序

- 便利店的商品陈列技巧

- 易语言源码易语言使用通用型源码.rar

- Công Cụ Đặt Hàng TopTaobao-crx插件

- deanyoung.github.io

- BTPollingTest:测试应用程序以确定 Bt 轮询作为在 android 上定位附近服务设备的方法

- AlexZortex.github.io

- 超市商品分类——卧具、家具类

- newrelic-vertica:在Vertica驱动程序的NewRelic RPM中启用SQL监视

- PriceReminder Plugin-crx插件