6.42

IDT70T3509M

High-Speed 2.5V 1024K x 36 Dual-Port Synchronous Static RAM Commercial Temperature Range

5

NOTES:

1. "H" = V

IH, "L" = VIL, "X" = Don't Care.

2. ADS, CNTEN, REPEAT = V

IH.

3. OE and ZZ are asynchronous input signals.

4. It is possible to read or write any combination of bytes during a given access. A few representative samples have been illustrated here.

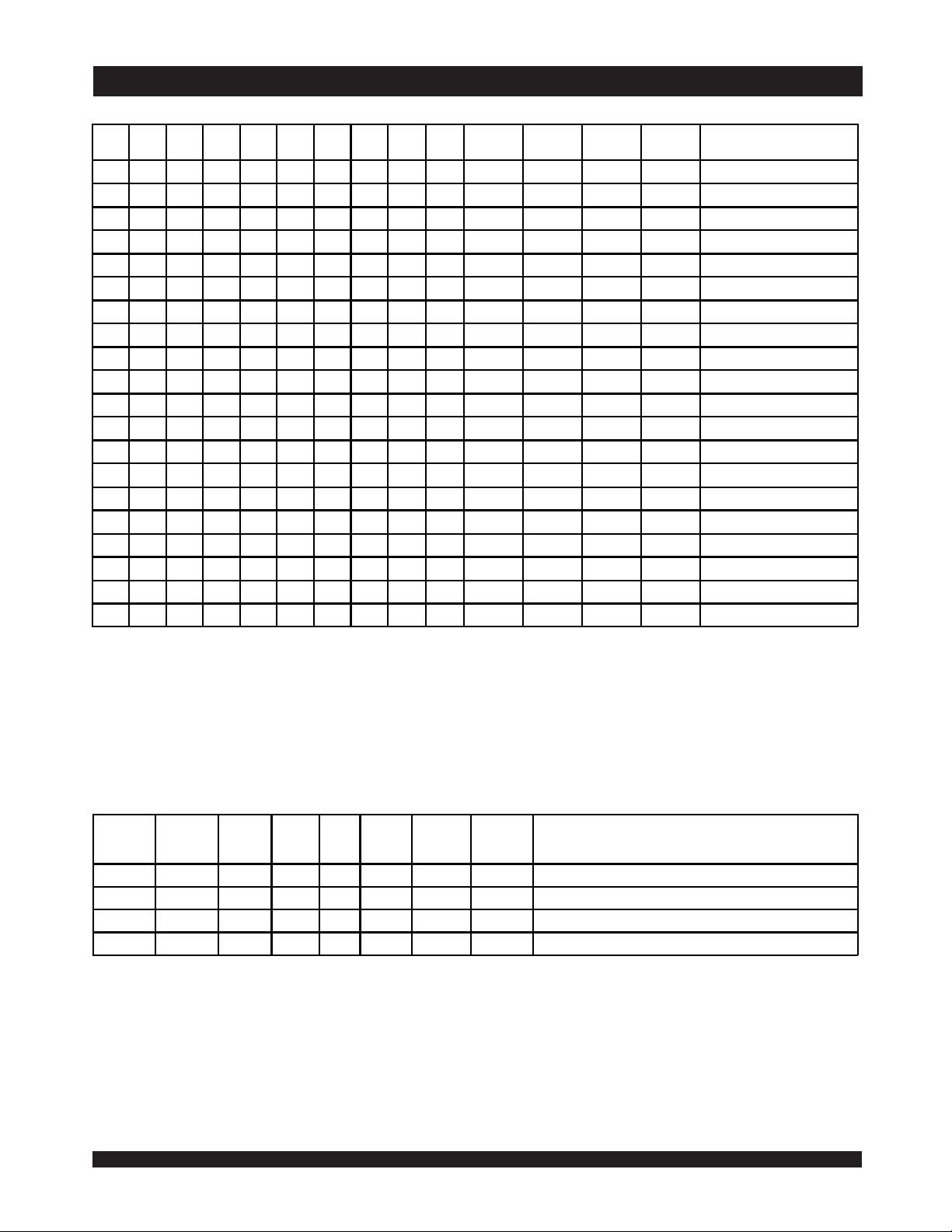

Truth Table I—Read/Write and Enable Control

(1,2,3,4)

OE

CLK

CE

0

CE

1

BE

3

BE

2

BE

1

BE

0

R/W ZZ

Byte 3

I/O

27-35

Byte 2

I/O

18-26

Byte 1

I/O

9-17

Byte 0

I/O

0-8

MODE

X

↑

HLXXXXXLHigh-ZHigh-ZHigh-ZHigh-ZDeselected–Power Down

X

↑

LLXXXXXXActiveActiveActiveActiveNot Allowed

X

↑

HHXXXXXXActiveActiveActiveActiveNot Allowed

X

↑

LHHHHHX LHigh-ZHigh-ZHigh-ZHigh-ZAll Bytes Deselected

X

↑

LHHHHL L LHigh-ZHigh-ZHigh-Z D

IN

Write to Byte 0 Only

X

↑

L H H H L H L L High-Z High-Z D

IN

High-Z Write to Byte 1 Only

X

↑

LHHLHHLLHigh-Z D

IN

High-Z High-Z Write to Byte 2 Only

X

↑

LHLHHHLL D

IN

High-Z High-Z High-Z Write to Byte 3 Only

X

↑

L H H H L L L L High-Z High-Z D

IN

D

IN

Write to Lower 2 Bytes Only

X

↑

LHLLHHLL D

IN

D

IN

High-Z High-Z Write to Upper 2 bytes Only

X

↑

LHLLLLLL D

IN

D

IN

D

IN

D

IN

Write to All Bytes

L

↑

LHHHHLHLHigh-ZHigh-ZHigh-Z D

OUT

Read Byte 0 Only

L

↑

L H H H L H H L High-Z High-Z D

OUT

High-Z Read Byte 1 Only

L

↑

LHHLHHHLHigh-Z D

OUT

High-Z High-Z Read Byte 2 Only

L

↑

LHLHHHHL D

OUT

High-Z High-Z High-Z Read Byte 3 Only

L

↑

L H H H L L H L High-Z High-Z D

OUT

D

OUT

Read Lower 2 Bytes Only

L

↑

LHLLHHHL D

OUT

D

OUT

High-Z High-Z Read Upper 2 Bytes Only

L

↑

LHLLLLHL D

OUT

D

OUT

D

OUT

D

OUT

Read All Bytes

H

↑

XXXXXXX LHigh-ZHigh-ZHigh-ZHigh-ZOutputs Disabled

XXXXXXXXXHHigh-ZHigh-ZHigh-ZHigh-ZSleep Mode

5682 tbl 02

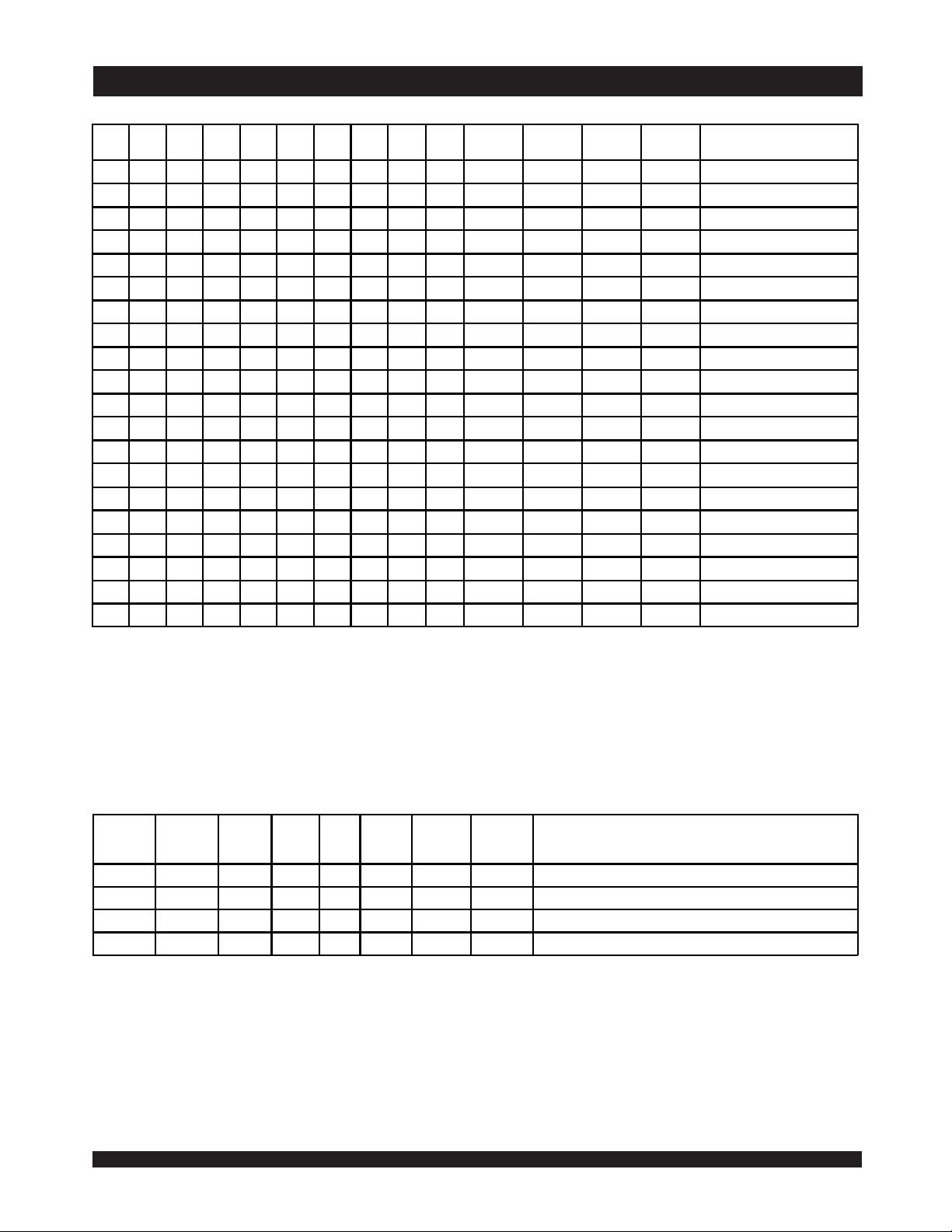

Truth Table II—Address Counter Control

(1,2)

NOTES:

1. "H" = V

IH, "L" = VIL, "X" = Don't Care.

2. Read and write operations are controlled by the appropriate setting of R/W, CE

0, CE1, BEn and OE.

3. Outputs configured in flow-through output mode: if outputs are in pipelined mode the data out will be delayed by one cycle.

4. ADS and REPEAT are independent of all other memory control signals including CE

0, CE1 and BEn

5. The address counter advances if CNTEN = V

IL on the rising edge of CLK, regardless of all other memory control signals including CE0, CE1, BEn.

6. When REPEAT is asserted, the counter will reset to the last valid address loaded via ADS. This value is not set at power-up: a known location should be loaded

via ADS during initialization if desired. Any subsequent ADS access during operations will update the REPEAT address location.

7. Address A

19 must be managed as part of a full depth counter implementation using the IDT70T3509M. For physical addresses 00000H through 7FFFFH the value

of a A

19 is 0, while for physical addresses 80000H through FFFFFH the value of A19 is 1. The user needs to keep track of the device counter and make sure that

A

19 is actively driven from 0-to-1 or 1-to-0 and held as needed at the appropriate address boundaries for full depth counter operation and that A19 is in the appropriate

state when using the REPEAT function.

Address

Previous

Internal

Address

Internal

Address

Used CLK

ADS CNTEN REPEAT

(6)

I/O

(3)

MODE

An X An

↑

L

(4)

XHD

I/O

(n) External Address Used

XAnAn + 1

↑

H L

(5)

HD

I/O

(n+1) Counter Enabled—Internal Address generation

(7)

XAn + 1An + 1

↑

HH HD

I/O

(n+1) External Address Blocked—Counter disabled (An + 1 reused)

XXAn

↑

XX L

(4)

D

I/O

(n) Counter Set to last valid ADS load

5682 tbl 03