Chipscope教程:使用CoreGenerator快速入门

需积分: 10 75 浏览量

更新于2024-07-24

收藏 437KB PDF 举报

"Chipscope_简明教程 - 一个介绍如何使用Chipscope的教程,适用于初学者,包括在Xilinx ISE环境下通过CoreGenerator和CoreInserter创建逻辑分析仪的方法。"

Chipscope是一种由Xilinx提供的内置逻辑分析工具,它允许工程师在FPGA(Field-Programmable Gate Array)设计中进行实时调试和验证。本教程是针对那些已经安装了仿真、综合、ISE和Chipscope软件的用户,特别提到了使用Modelsim5.8作为仿真工具,Synplifypro7.5.1进行综合,以及ISE6.2用于布局和布线。

教程首先展示了RTL(Register Transfer Level)设计及其仿真过程。一个名为`lfsr.v`的RTL源代码被用作示例,同时提供了测试平台`lfsr_tb.v`。通过这些代码,用户可以看到仿真波形,了解设计的行为。

接下来,教程详细讲解了两种生成Chipscope逻辑分析仪的方法:通过CoreGenerator和CoreInserter。CoreInserter方法直接在已综合的Netlist中插入逻辑分析仪,而CoreGenerator则需要在RTL设计中直接插入逻辑分析代码。由于CoreInserter需要在Netlist中搜索信号,相对更复杂,每次修改RTL后都需要重新插入,因此教程选择了使用CoreGenerator流程,因为它在修改RTL后只需要重新进行综合、布局和布线。

以下是使用CoreGenerator创建Chipscope ILA(Integrated Logic Analyzer)的步骤概述:

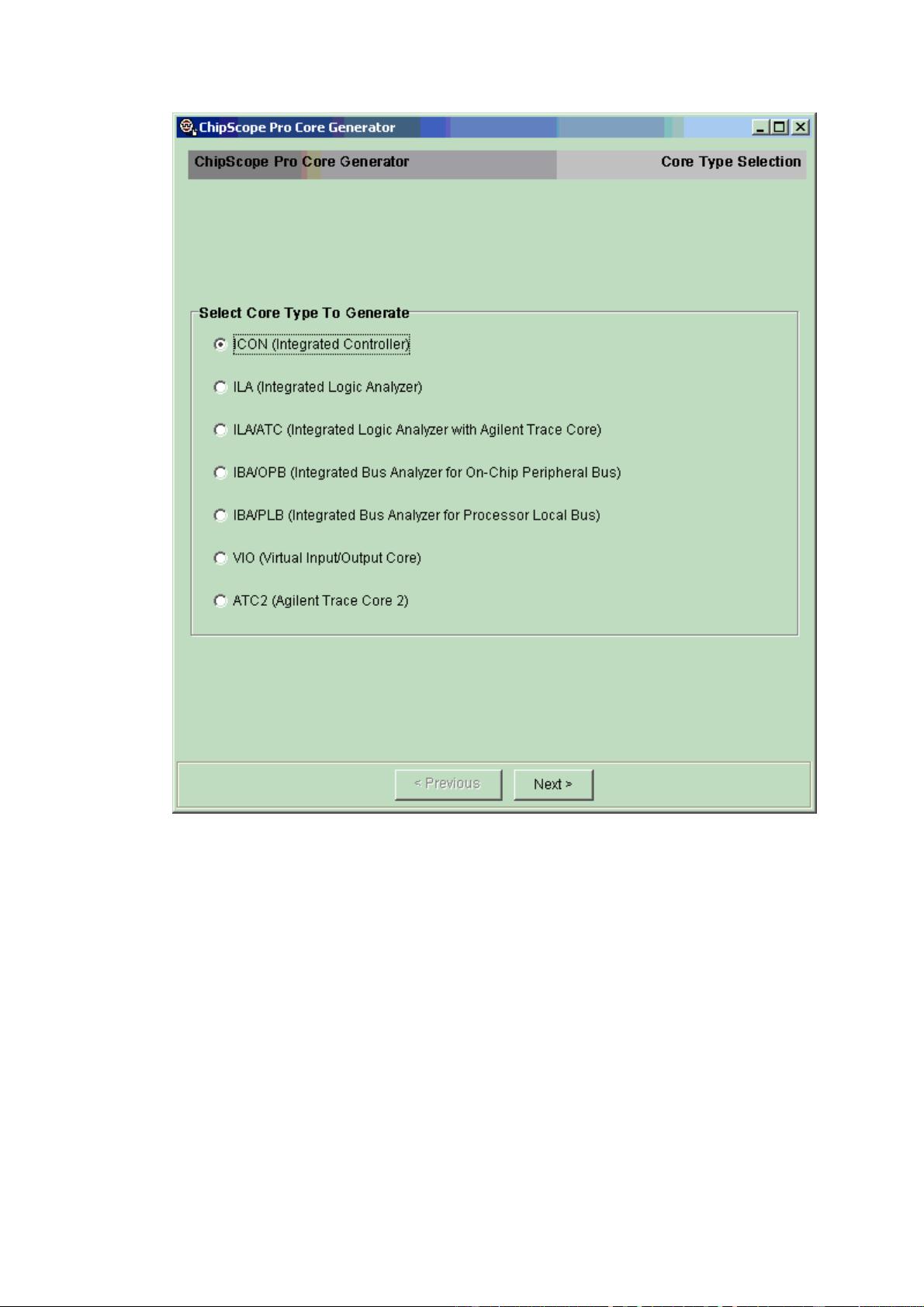

1. 启动ChipScope Pro CoreGenerator。

2. 选择图标以创建集成控制器。

3. 指定输出目录和目标设备家族。

4. 选择设计语言和综合工具。

5. 生成集成控制器的Core。

6. 回到主菜单,选择ILA来创建逻辑分析仪。

7. 设置输出目录、设备家族和采样时钟边沿。

8. 设置触发宽度为32。

9. 选择`DataSameAsTrigger`,使数据端口与触发端口相同。

10. 选择采样深度,并注意不要超过设备的BlockRAM限制。

11. 选择语言和综合工具。

12. 生成ILA的Core。

这个教程对每个步骤都有详细解释,帮助用户理解如何在Xilinx ISE环境中有效地使用Chipscope进行FPGA设计的调试,这对于提升设计效率和确保设计正确性至关重要。通过Chipscope,工程师可以观察FPGA内部信号,捕捉并分析潜在的问题,从而优化他们的硬件设计方案。

198 浏览量

2009-03-12 上传

2021-05-26 上传

2023-12-20 上传

2023-03-16 上传

2023-03-16 上传

2023-05-05 上传

2023-08-24 上传

2024-10-28 上传

zxfxz123

- 粉丝: 0

- 资源: 2

最新资源

- sweet_smoke_lp

- SPWM.rar_单片机开发_Windows_Unix_

- GMSMapView-Additions:自定义GMSMapView“我的位置”按钮

- Django_Network:Django社交网络

- ImageLab-Initial:ImageLab是一个独立工具,可让用户使用其GUI玩OpenCV

- Teste-oo1:用StackBlitz创建:high_voltage:

- Web应用程序和服务的集中式和分布式日志记录,扩展了System.Diagnostics和Essential.Diagnostics,提供了结构化的跟踪和日志记录,无需更改应用程序代码的1行-JavaScript开发

- torch_sparse-0.6.9-cp36-cp36m-macosx_10_9_x86_64whl.zip

- yukimryh.zip_matlab例程_matlab_

- TeTsuYa IRC Bot-开源

- qa_guru_4_10_owner_xt4k:草稿

- Assembla Mentions-crx插件

- 点击:简单的React useState钩子示例

- 参考资料-中国的书法艺术和技巧.蓝铁.zip

- 一个无主题的Web组件,用于根据表单字段值过滤可见的子元素。-JavaScript开发

- arduino-volume2:Arduino tone()-仅使用扬声器即可实现多种波形和8位音量控制!