没有合适的资源?快使用搜索试试~ 我知道了~

首页2020 RFIC Symposium特辑:毫米波技术与高精度雷达接收器研究

2020 RFIC Symposium特辑:毫米波技术与高精度雷达接收器研究

需积分: 8 1 下载量 124 浏览量

更新于2024-07-07

收藏 61.16MB PDF 举报

IEEE Journal of Solid-State Circuits (JSSC) 2021年5月号特刊聚焦于2020年无线集成电路研讨会的先进研究成果,展示了固体-state电路设计的最新进展。本期特别关注毫米波技术、汽车雷达系统、射频前端、集成接收器以及通信系统的创新。

1. **毫米波多输入多输出(MIMO)阵列设计**:

S.Ahasan等人提出了一种频率域复用(Frequency-Domain Multiplexing)的单线接口技术,结合了谐波拒绝特性,用于毫米波MIMO阵列中的信号解复用。这项工作旨在提高数据传输效率和抗干扰性能,对于未来的无线通信系统具有重要意义。

2. **高频率和高精度的雷达应用**:

M.Kohtani等人的研究展示了一个76至81 GHz的CMOS集成自测试方案,实现了72分贝信噪比(dBc/N)及小于1ppm的频率稳定性,适用于多通道雷达系统,确保了高度精确的测距和目标识别能力。

3. **汽车雷达收发器设计**:

T.Arai等人介绍了一款针对250米长距离的77 GHz 8路接收3路发射的车载雷达系统,采用40纳米CMOS工艺,这标志着在高频率和小型化方面的重要突破,有助于提升车辆的安全性和感知能力。

4. **集成数字接收器**:

R.Lu等人呈现了一款16元素的28 GHz全数字化接收器,具备数字RX波束形成功能,这在雷达和通信系统中是关键组件,能实现更精细的方位角和角度估计,从而提高系统性能。

5. **全双工通信技术**:

文章探讨了在300 GHz和4.2 K频段内实现宽带全双工操作的方法,通过双边单边带频率转换技术,实现了同时发送和接收的能力,这对于未来的无线通信网络具有重大潜力。

总体而言,JSSC 2021年5月号特刊展现了当前射频集成电路设计的前沿水平,反映了行业对高性能、低功耗和多功能集成的需求,为无线通信和雷达系统的进一步发展提供了强有力的理论和技术支持。这些成果将推动半导体技术的进步,并促进未来电子设备的智能化和高效能。

1344 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 56, NO. 5, MAY 2021

Yoshiyuki Utagawa received the B.E. and M.E.

degrees in electronic science and engineering from

Kyoto University, Kyoto, Japan, in 2002 and 2004,

respectively.

In 2004, he joined Hitachi, Ltd., Tokyo, Japan,

where he was engaged in the research and devel-

opment of circuit design and evaluation technol-

ogy for various analog circuits (ADC, DAC, DLL,

etc.). Since 2015, he has been with DENSO Cor-

poration, Aichi, Japan, and has been engaged in

millimeter-wave CMOS integrated circuits, espe-

cially baseband block development. His research interests focus on RF

integrated circuits for millimeter-wave automotive radar, and ADCs including

digital calibration techniques.

Masato Kohtani (Member, IEEE) received the B.S.

and M.S. degrees in electrical engineering from

Hokkaido University, Hokkaido, Japan, in 1999 and

2001, respectively.

In 2001, he joined Sharp Corporation, Osaka,

Japan, where he was engaged in the research

and development of RF LSIs. In 2012, he joined

Samsung Research and Development Institute

Japan, Kanagawa, where he was involved in the

development of high data-rate wireless mm-wave

communication ICs. In 2014, he joined DENSO

Corporation, Aichi, Japan, and is currently with MIRISE Technologies

Corporation, Tokyo, Japan. His current research interests include RF and

millimeter-wave circuits and built-in self-tests for radar applications.

Ikuma Ando (Member, IEEE) received the B.E. and

M.E. degrees in electrical and electronic engineering

from the Tokyo Institute of Technology, Tokyo,

Japan, in 2012 and 2014, respectively.

In 2014, he joined NEC Green Platform Laborato-

ries, Kanagawa, Japan, and was engaged in research

and development of fixed wireless systems. Since

2015, he has been with DENSO Corporation, Aichi,

Japan, and was engaged in millimeter-wave CMOS

integrated circuits from 2015 to 2019. Since 2019,

he has been engaged in the development of automo-

tive radar systems in the AD&ADAS Eng. Div. of DENSO Corporation.

Kazuhiro Matsunaga received the B.E. degree from

the Shibaura Institute of Technology, Tokyo, Japan,

in 2002.

In 2002, he joined Japan Radio Co., Ltd. Tokyo,

Japan, and was engaged in the research and devel-

opment of CMOS ICs for wireless communication.

Since 2017, he has been with DENSO Corporation,

Aichi, Japan, and has been developing millimeter-

wave automotive radar systems.

Chihiro Arai received the B.E. and M.E. degrees

in electrical engineering from the Tokyo University

of Science, Tokyo, Japan, in 2009 and 2011.

In 2011, he joined Renesas Electronics

Corporation, Tokyo, Japan, where he developed

CMOS RF-ICs for cellular communication and near

field communications. Since 2015, he has been

with DENSO Corporation in Aichi, Japan, and has

been developing millimeter-wave automotive radar

systems for autonomous vehicles.

Shinji Yamaura (Member, IEEE) received the

B.E. and M.E. degrees from the Tokyo Institute

of Technology, Tokyo, Japan, in 1989 and 1991,

respectively.

In 1991, he joined Fujitsu Laboratories Ltd.

Kanagawa, Japan, and was engaged in the research

and development of simulation modeling, circuit

design, and evaluation technology up to 100 GHz

for optical communication systems and wireless

communication systems, such as Mobile-WiMAX

and CMOS Power Amplifiers for WCDMA/LTE.

In 2014, he joined DENSO Corporation, Aichi, Japan, and was engaged in

millimeter-wave CMOS integrated circuits and mm-wave radar systems. He is

currently a Project Director in the Sensor Research and Development Division

of MIRISE Technologies Corporation.

Mr. Yamaura is a member of IEEE SSCS, MTT-S, CAS, APS, SPS, and

IEICE of Japan.

IEEE JOURNAL OF SOL ID-STATE CIRCUITS, VOL. 56, NO. 5, MAY 2021 1345

76- to 81-GHz CMOS Built-In Self-Test With

72-dB C/N and Less Than 1 ppm Frequency

Tolerance for Multi-Channel Radar Applications

Masato Kohtani , Member, IEEE, Tomotoshi Murakami, Member, IEEE, Yoshiyuki Utagawa ,

Tomoyuki Arai

, Member, IEEE, and Shinji Yamaura , Member, IEEE

Abstract— A built-in self-test (BIST) system with a 72-dB

carrier-to-noise ratio (C/N) and less than 1-ppm frequency

tolerance of down-conv erted BIST tone for a multi-channel radar

application is presented. The BIST consists of a frequency dou-

bler, an up-conversion mixer (UPMIX), a variable gain amplifier,

a phase shifter, an eight-way splitter, and an RF PAD coupler for

BIST signal distribution. The proposed BIST system can operate

from 76 to 81 GHz, mixing with arbitrary offset frequencies from

600 kHz to 42.7 MHz generated by a fully-synchronized phase

locked loop (PLL). The proposed UPMIX can generate zero or

non-zero offset frequencies by switching between two modes flex-

ibly implemented in the same layout area. The measured relative

phase among all eight channels was less than 2

◦

from −25

◦

C

to 150

◦

C through on-chip 12-bit analog-to-digital converters

(ADCs). The proposed BIST was fabricated using a 40-nm CMOS

process and assembled with a wafer-level chip-sized package

(WLCSP). Also, state-of-the-art BIST beamformer analyses were

demonstrated as one of the future methods for self-diagnosis with

a null-depth monitoring for a multi-channel radar application.

Index Terms— Automotive applications, built-in self-test

(BIST), CMOS integrated circuits, design for testability,

millimeter-wave (mm-Wave) radar.

I. INTRODUCTION

V

ARIOUS millimeter-wave (mm-Wave) radar ICs with

CMOS [1]–[4] or BiCMOS [5], [6] intended for auto-

motive driving safety and driver aids systems as well as

self-driving vehicles are actively being developed. Also,

in order to realize 360

◦

circumference sensing, multiple rad a r

sensors capable of short, medium, and long-range detections

will be required in vehicles [7], [8]. Recently, various multiple-

input multiple-output (MIMO) radars with multi-channels to

realize extended virtual receivers (RXs) for angular accu-

racy, such as 12 channels with 3 transmitters (TXs) and

Manuscript received October 2, 2020; revised December 11, 2020 and Feb-

ruary 7, 2021; accepted March 3, 2021. Date of publication March 30, 2021;

date of current version April 23, 2021. This article is an expanded version

from the 2020 IEEE RFIC Symposium, Los Angeles, CA, USA, August 4–6,

2020. This article was approved by Associate Editor Mohyee Mikhemar.

This work was supported by DENSO Corporation. (Corresponding author:

Masato Kohtani.)

Masato Kohtani and Shinji Yamaura are with the Sensor Research and

De velopment Division, MIRISE Technologies Corporation, Tokyo 108-0075,

Japan (e-mail: masato.kohtani.j3a@mirise-techs.com).

Tomotoshi Murakami, Yoshiyuki Utagawa, and Tomoyuki Arai are with the

ASIC Engineering Division, DENSO Corporation, Aichi 448-8661, Japan.

Color versions of one or more figures in this article are available at

https://doi.org/10.1109/JSSC.2021.3066214.

Digital Object Identifier 10.1109/JSSC.2021.3066214

Fig. 1. Block diagram of the proposed BIST with a PLL and an RX chain.

4 RXs [1], [4] or as many as 192 channels with 12 TXs

and 16 RXs [2] have been reported. Also, several mm-Wave

built-in self-test (BIST) features have been demonstrated for

multi-channel transceivers with high integration in the previous

works [1], [4]–[6] in order to achieve autonomous fault mon-

itoring of the RF chain and guarantee system-level functional

safety. For radar applications, the main sensing information

consists of range, angle, and velocity. The system goal with a

multi-channel rad ar in tandem with the BIST sy stem consists

of: 1) testability improvement; 2) regular self-diagnosis; and

3) test cost reduction in the future. In particular, to diagnose a

multi-channel radar regularly by mon itoring the frequency or

angle with the BIST signal even after shipment is desired for

an actual radar operation to detect the distance to an object

or direction of arrival (DoA). For example, these diagnoses

with the BIST system are considered to be performed as of ten

as possible soon after starting the engine or restarting from

stand-by mode. The simplified block diagram including the

proposed BIST system, a phase locked loop (PLL), and an

RX chain in a radar is shown in Fig. 1. A low-noise CMOS

RX with a noise figure (NF) of 9 dB for radar applications

has been presented in [9]. The proposed BIST system has been

implemented in the same multi-chann e l radar IC with 3 TXs

and 8 RXs [10]. Also, the basic performances such as gain,

NF, linearity, and phase noise have been described in [10]. The

RF gain including a low-noise amplifier (LNA) and a mixer

is about 22 dB at 77 GHz while the intermediate frequency

amplifier (IFAMP) gain is 33 dB in an RX chain.

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information.

1346 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 56, NO. 5, MAY 2021

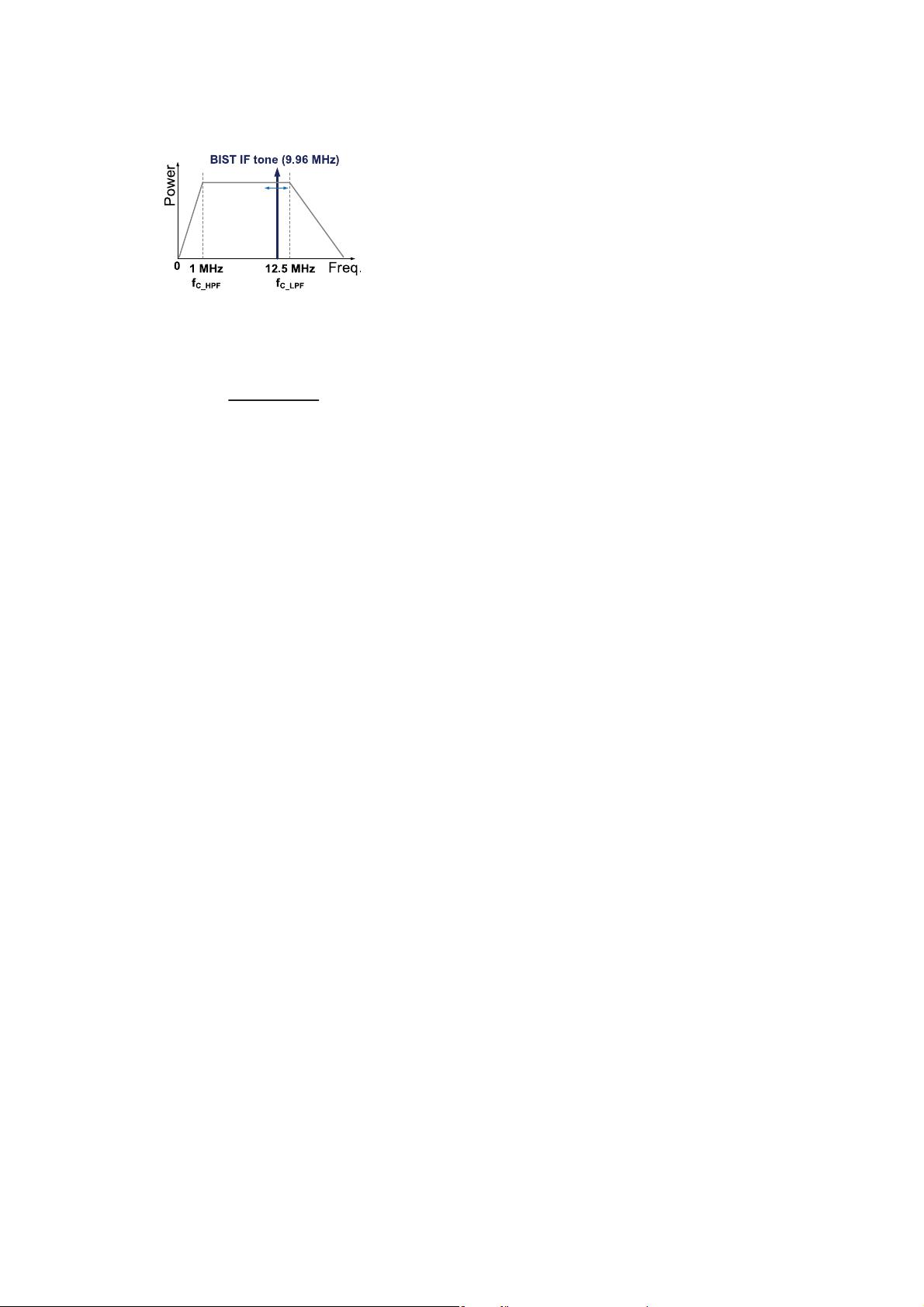

Fig. 2. Consideration of a diagnosis with BIST on IF characteristics.

In a linearly swept frequency modulated continuous

wave (FMCW) as shown in [7], the range (R) is calculated b y

R =

f

B

×c

0

× T

ramp

2 × BW

(1)

where c

0

is the speed of light in free space. From (1), it is

obvious that the range is proportional to the beat frequency

( f

B

). If the beat frequency ( f

B

) is set to 10 MHz by employing

a BIST under a chirp configuration with bandwidth (BW)

of 300 MHz and ramp time (T

ramp

) of around 41 μs as in [10],

the resultant range is around 204 m. The 10-MHz setting is one

possible candidate to allow the BIST signal to be distinguished

easily even under actual conditions since the reflected signal

power from a distant object at 204 m must be very weak.

Also, the maximum IF is now set to 12.5 MHz, which can

be extended to 25 MHz if necessary, which is limited by the

analog-to-digital converter (ADC’s) cap ability. Also, there are

bandpass filter (BPF) characteristics on the IF band with a

high pass filter (HPF) cutoff frequency ( f

c_HPF

) of 1 MHz

to suppress strong reflections such as a bumper reflection

noise after down-conversion and low pass filter (LPF) cutoff

frequency ( f

c_LPF

) of 12.5 MHz as shown in Fig. 2. Therefore,

the BIST frequency should cover from as small as a few

hundreds of kHz to as large as a few tens of MHz to d iagnose

BPF-like IF characteristics, which h as not been reported so far.

Frequency accuracy and stable test signal that are not affected

by outside conditions are two of the most essential key features

for robust evaluations. Besides, for non-zero frequency BIST

testing, a carrier [lo cal oscillator (LO)] leakage of the BIST

RF tone should be suppressed as much as possible to avoid

dc offset issues caused by self-mixing after down-conversion

in the RX.

The diagnosing angle is one of the most challenging topics

for mu lti-channel radars since it is extremely d ifficult to

measure the relative phases by probing all of the LNA’s input

PADs simultaneously to apply m m-Wave external signals with

equal phase alignments. Recently, a 76–81-GHz multi-channel

radar IC with 6 RXs and 2 TXs using a 0.13-μm SiGe process

including a quadrature BIST modulator has been reported

in [6], where the monitored relative phase variations were 2

◦

on average across temperatures up to 100

◦

C among the limited

combinations of CH1–CH4 and CH5–CH6. No other details

on phase results are given when monitoring the overall RX

status from a system diagnosis standpoint. On the other hand,

a unique beamformer analysis with a BIST signal has been

reported in [5], where the peak always occurs when the relative

phase between channels () is equal to θ ,whereθ = 150

◦

at 76 GHz since there is a phase shift (θ) between sampling

nodes in the straight BIST signal distribution network, which

corresponds to the LNA’s input PAD pitch between adjacent

channels.

A high carrier-to-noise ratio (C/N) with enough amplitude in

the BIST signal as well as a good frequency tolerance of BIST

signals should also be taken into account in order to achieve a

good phase accuracy of less than 2

◦

. Using an external signal

generator asynchronous to a PLL in a radar IC causes poor

frequency and phase accuracies in RX tests since only the IC,

being exposed to testing temperatures, tends to be affected

by frequency d rift. In the published article, C/N of 62 dB of

the BIST tone has been presented in [5]. As for the RF of

radars, the first band of 76–77 GHz prevails worldwide, and

the second band of 77–81 GHz has also been expected to

aim at an improved angular resolution intended for medium

or short-range detections [7]. So, in this article, the measured

frequencies are extended to cover not only 76–77 GHz but

also 77–81 GHz to investigate BIST capabilities at high

frequencies, which is regarded as an extension of what has

been reported in our previous works [10], [11]. Also, in this

article, th e quality of a fully-synchronized BIST signal is

described in detail with an external test signal for comparison.

A diagnosis by fully monitoring the BPF-like IF characteristics

by employing the proposed BIST covering a wide frequency

range has first been reported. The RF PAD pitch between adja-

cent channels is designed with a half-lambda on the straight

BIST distribution network differently from [5], which leads to

testability improvements in terms of phase measurements. All

possible relative phase results measured up to 150

◦

C from

a system diagnosis standpoint have been analyzed in detail.

Test cost reduction with BIST should be taken into account

especially for multi-channel radar ICs. An efficient dc test

with the proposed BIST has also been proposed for testability

improvements covering mm-Wave blocks such as an RX and

PLL and so on intended fo r a multi-channel radar application

even under a dc test environment. Furthermore, to the best of

our knowledge, the world’s first beamformer analyses using

down-converted BIST signals have been proposed aiming at

future diagnoses, which is a remarkable extension of what was

reported in [11].

This article is organized as follows. The d etailed concept

of the proposed BIST architecture and implementation is

described in Section II. The representative BIST method-

ologies with key features are shown in Section III, and the

measured diagnosis results with BIST are shown in Section IV,

while the conclusion and the references are given in Section V

and the final section, respectively.

II. BIST A

RCHITECTURE AND IMPLEMENTATION

A. Synchronized BIST System

The proposed on-chip BIST is shown in the dashed box

in Fig. 1. The BIST can mix a 76.5-GHz signal with a BIST

CLK 10-MHz signal and generate 76.5 GHz ± 10 MHz,

followed by a phase shifter (PS2), transmission line type

splitter, and 20-dB RF PAD couplers to distribute the BIST

signals to the LNA inputs. The BIST CLK frequency generated

KOHTANI et al.: CMOS BIST WITH 72-dB C/N AND LESS THAN 1 ppm FREQUENCY TOLERANCE 1347

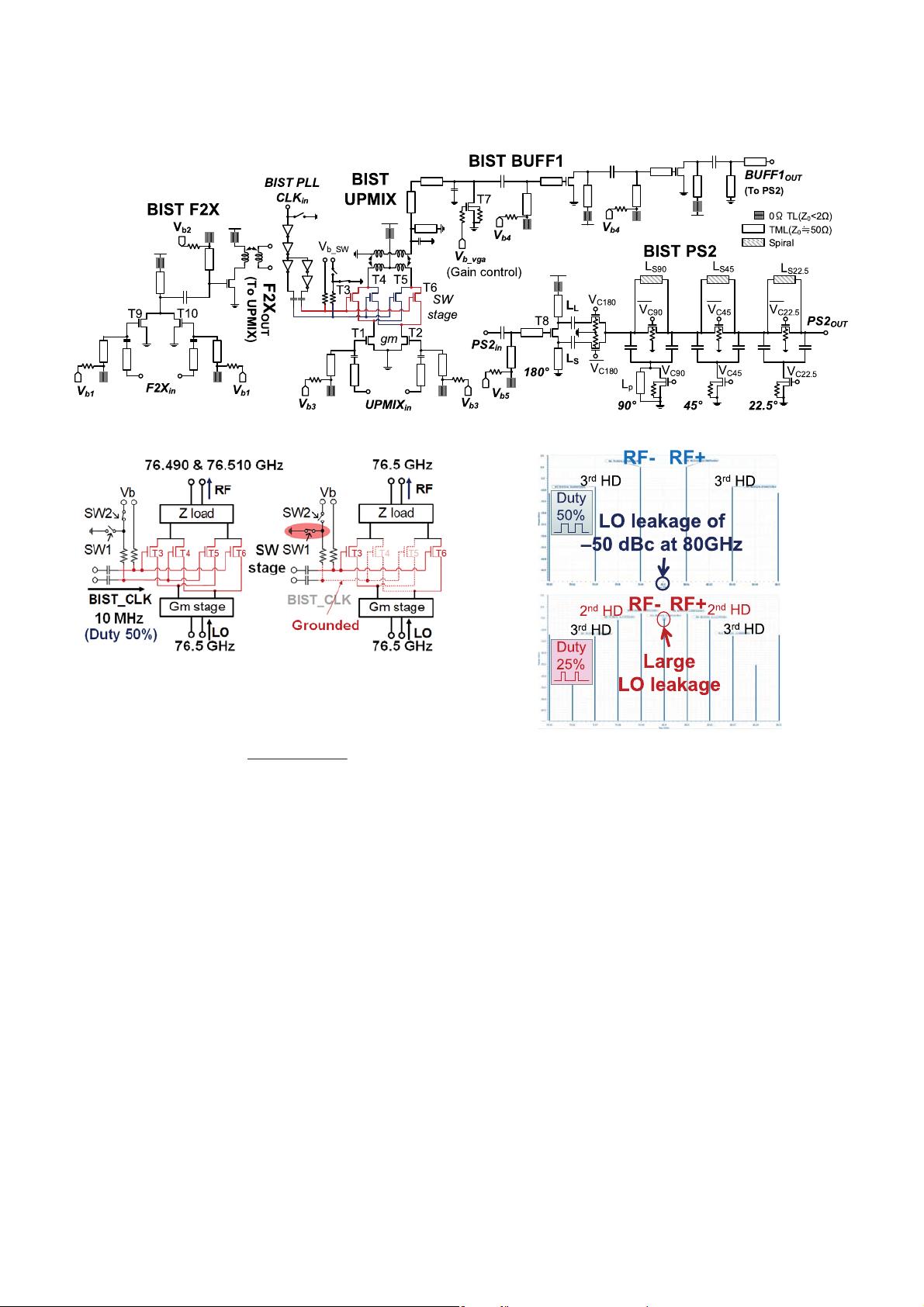

Fig. 3. Schematic of the proposed BIST UPMIX, phase shifter, and F2X.

Fig. 4. Schematic comparison for the proposed UPMIX with switchable

two-tone mode (left) and one-tone mode (right).

by the PLL is expressed as

f

BIST_CLK

=

f

LO

2

7

×P × N × D

(2)

where P means selectable division ratio of 1, 2, 4, ..., 16,

N performs the PLL counter values of 0, 1, ..., 31 and

D performs a fixed division ratio of 2 used for a divide-

by-two after counter to guarantee a duty ratio of 50% ± 5%.

If f

LO

= 76.5 GHz, P = 1, N = 30, D = 2, the BIST

CLK frequency observed from IFAMP’s differential out-

puts intermediate frequency signal output (IFOUT) becomes

f

BIST_CLK

= 9.9609375 MHz. Since the up-converted BIST

RF is expressed as f

RF

= f

LO

± f

BIST_CLK

, the down-converted

BIST signal always becomes exactly f

BIST_CLK

even under

chirp modulation. In the BIST system, the original BIST CLK

signal before an up-conversion can also be monitored directly

from the external test pin as an absolute phase reference

as shown in Fig. 1. All of the BIST related signals are

generated from the same PLL synchronously, which leads to

good frequency accuracy in the BIST signals.

B. BIST Up-Conversion Mixer

The proposed up-conversion mixer (UPMIX) is one of the

most key building blocks in the BIST system. In order to

enhance testability and layout efficiency, a combined design

approach capable of not only a mixing-mode but also a

through-mode was taken into account for the proposed BIST

Fig. 5. Simulated LO leakage performance comparison with BIST CLK’ s

duty ratios of 50% versus 25% for the proposed BIST UPMIX.

UPMIX. The dedicated UPMIX with a Gilbert cell topology

can generate not only two-tone signals in a mixing-mode

but also a one-tone signal in a through-mode by employing

bias switches in the switch stage as shown in Fig. 3 . In the

case of an up-conversion, the BIST CLK signal is applied

to the mixer switching (SW) stage through inverter chains.

The LO signal is applied to the transconductance (gm) stage

instead of the SW stage in order to avoid an LO feedthrough.

The BIST CLK buff ers were designed to operate with rail-

to-rail swings up to around 100 MHz after parasitic extraction.

In the case of a one-tone mode (through-mode), the gate bias

nodes of the two transistors (T4 and T5) in the SW stage

become shorted to ground via SW1 as shown in Fig. 4 so that

the LO signal can be bypassed to the output nodes without

mixing, where the UPMIX behaves like a cascode amplifier.

The current consumption is around 34.9 mA at a 1.1-V supply

regardless of BIST one-tone mode or two-tone mode. Also,

the BIST CLK signal can be terminated to the ground with

an extra switch (not shown) to produce a clean continuous

signal without any spur. The BIST gain can be controlled

with 4-bit fine gain tuning with less than 1-dB resolution

and attenuation o f over 6 dB with a short-to-ground switch

1348 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 56, NO. 5, MAY 2021

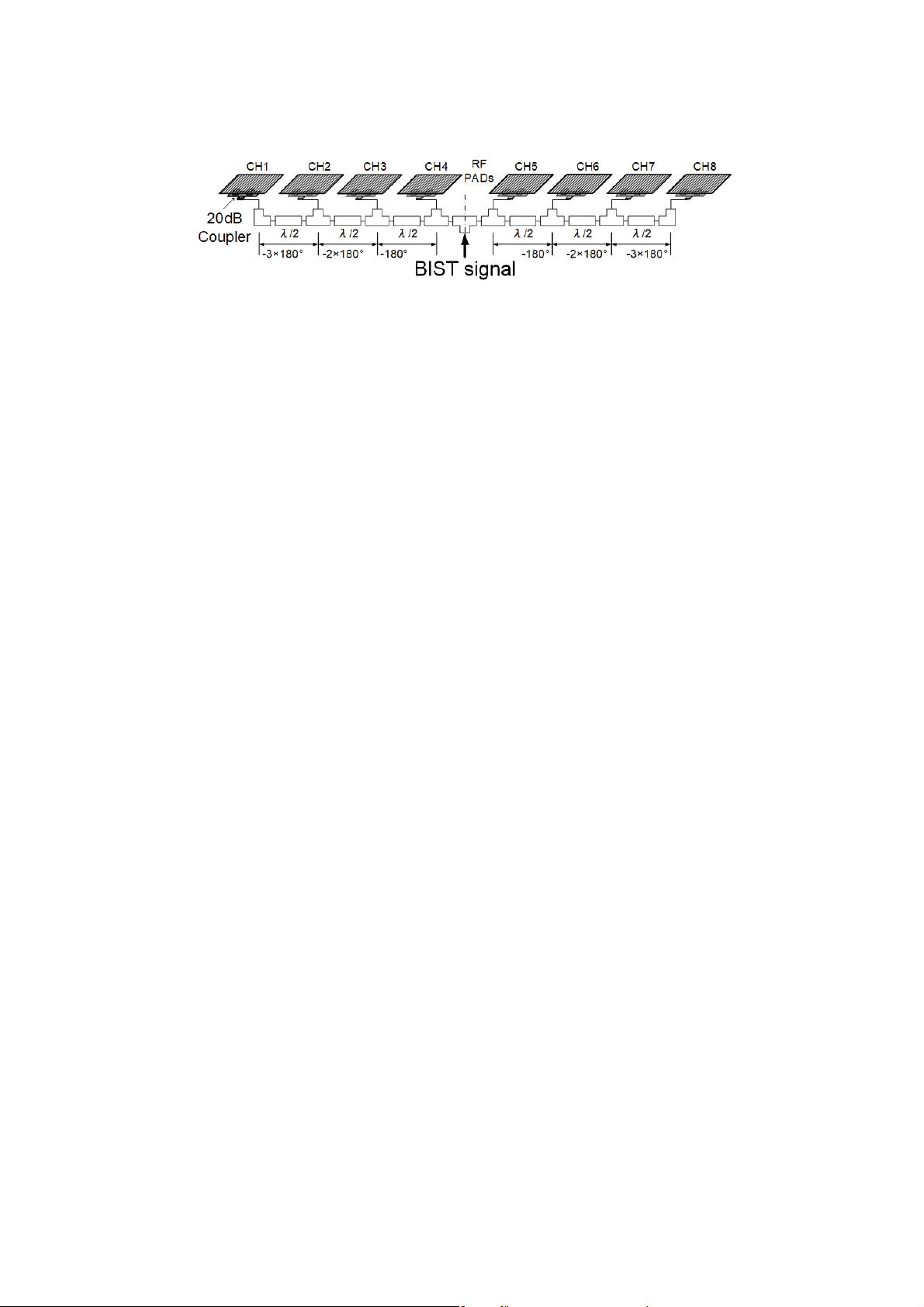

Fig. 6. BIST signal distribution network and 20-dB PAD couplers designed with a half-lambda pitch.

by the transistor T7 in Fig. 3 which is co-designed in the

inter-stage matching network. The three-section LC BPF topol-

ogy is employed in the inter-stage matching network to obtain

flat gain performance which consists of area-effective 50-

meander-type transmission lines and mm-Wave ac ground

parts with the measured characteristic impedance of less than

2 at 80 GHz by employing metal–oxide–metal (MOM)

capacitors. Fig. 5 shows the simulated LO leakage for the

proposed BIST UPMIX depending on CLK duty ratios. In the

case of a 50% CLK duty ratio, a good LO leakage performance

of −50 dBc is achieved. On the other hand, in the case of a

25% CLK duty ratio, deteriorated LO leakage performance of

as poor as −5 dBc and signal degradation by −3dBwere

observed. The simulation indicates that the signal loss is less

than 0.5 dB as long as the duty ratio is guaranteed to be within

50% ± 5%. So, an accurate duty ratio within 50% ± 5% as

a PLL BIST CLK is very crucial to suppress LO leakage.

If the BIST loop back signal were modulated with

ON–OFF

keying (OOK) in [1] and [4] although it is introduced as a

TX signal monitoring method not an RX in these articles,

the residual LO leakage would remain strong, which could

cause self-m ixing dc offsets after down-conversion.

C. BIST Phase Shifter

The proposed phase shifter (PS2) plays an important role

in the BIST system in order to control image interference

phenomena after a down-conversion in such a simple RX

architecture as shown in Fig. 1. The proposed 4-bit coarse

tuning phase shifter in the BIST makes it possible to change

the phase shift from 0 to 337.5

◦

with 22.5

◦

steps with a

well-known single-ended topology of switched LC type phase

shifters [12] as shown in Fig. 3. Note that the proposed 180

◦

phase shifter has a unique topology. The gain obtained from

the drain output node of transistor T8 can be approximately

expressed as L

L

/L

S

which is designed to become ideally unity

with signals shifted by 180

◦

. On the other hand, non-shifted

signals (0

◦

) can be obtained from the source node of T8 as a

source follower.

Also, the back gates of the switch transistors are grounded

by way o f the resistor for an accuracy improvement in the

phase control. The BIST phase shifter is considered to be

indispensable for image suppression control which is shown

in Section III-A. Common source amplifiers with four stages

similar to BUFF1 in Fig. 3 are used as output bu ffers (not

shown) for the compensation of gain losses. The total current

consumption including the output buffers is around 45.3 mA

at a 1.1-V supply.

D. BIST Frequency Doubler

A frequency doubler (F2X) with a matching network is

partially shown in Fig. 3. The drain terminals of the input tran-

sistors (T9 and T10) are connected together for the purpose of

frequency doubling with a gate bias voltage of around 0.45 V

applied to V

b1

in order to strengthen second-order distortion.

The total current consumption including input buffers (not

shown) is around 35 mA at a 1.1-V supply.

E. BIST Signal Distribution Network and PAD Coupler

Fig. 6 shows a passive eight-way splitter and PAD cou-

plers design placed with a half-lambda pitch (900 μmat

77 GHz) for a BIST signal distribution without any active

devices. The phase at 77 GHz of the BIST signal changes as

−180 ×n(n = 1, 2, 3) away from center-located BIST

channels of CH4 and CH5. The structure of the dedicated

PAD layout for the 77-GHz BIST 20-dB PAD coupler

co-designed with wafer-level-chip-sized package (WLCSP)

layers is depicted in Fig. 7. Also Fig. 7(b) and (c) shows

layouts for an electromagnetic simulation with some merged

VIAs for efficient simulation s. Also, the center of the bump

is located 110 μm away from the center of the signal PAD on

silicon for the purpose of reliability with a redistribution layer

(RDL, copper, thickness = 4.3 μm), which is 7.5 μm higher

than the surface of the top metal named as LB (aluminum,

t = 2.8 μm). Additionally, the small PAD opening size of

51 μm × 46 μm was laid out to comply with the low-density

design rules on metal dummy fills to minimize parasitic

components. Also, the metal-to-metal parasitic capacitance

area of 12 μm × 5 μm with less than 5 fF for the 20-dB BIST

coupler was laid out between the 2nd top thick metal named

as 3A (Cu, t = 3.3 μm) and the 3rd top thick metal named

as FA (Cu, t = 0.85 μm) with 0.68-μm spacing as shown

in Fig. 7(a) and (c). The BIST metal routing of FA in Fig. 7(b)

was laid out to detour the very large bump to minimize

parasitic capacitance. Also, no metal routin gs were laid out

under the very large bump to reduce parasitic components.

In the silicon design, channel-to-channel coupling of over

40 dB is guaranteed due to two 20-dB PAD couplers employed

from one channel to the other. An electromagnetic simulation

indicates that the coupling turns out to be less than 30 dB

caused by the very large bumps after WLCSP assem bly. Fig. 8

shows a chip micrograph focusing on the proposed BIST

system fabricated in a 40-nm CMOS process with a WLCSP

assembly. The mm-Wave BIST core circuits are located on the

limited narrow space between RX CH4 and CH5. Fig. 9 shows

the magnified p icture of the inter-stage matching network for

剩余321页未读,继续阅读

2014-09-15 上传

2012-12-21 上传

2021-12-26 上传

2021-12-26 上传

2020-11-15 上传

2021-12-26 上传

2021-12-26 上传

2021-12-26 上传

2021-12-26 上传

netshell

- 粉丝: 11

- 资源: 185

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功