PCIe调试详解:拓扑、资源分配与配置空间解析

需积分: 11 111 浏览量

更新于2024-07-15

收藏 4.06MB DOCX 举报

"这份文档是对PCI Express (PCIe)技术的详细总结,主要涵盖了PCIe的基础概念、拓扑架构、协议结构、枚举原理以及资源分配。文档特别强调了XILINX PCIe IP核的配置,包括设备类型、中断类型和资源申请的设置,以及信号质量的调整。此外,还介绍了PCI配置空间,包括Bridge和Agent两种类型的配置空间结构和关键寄存器的作用。"

PCIe基本概念是理解整个PCIe系统的关键。PCIe是一种高速接口标准,用于连接计算机系统中的外部设备,如显卡、网卡和硬盘。PCIe拓扑由根复合体(Root Complex)、端点设备(Endpoint)和可能的交换机(Switch)组成。在拓扑架构中,每个设备通过一个物理端口(Port)连接,Port可以视为一种桥接设备,即PCI Bridge。

PCIe协议结构图展示了事务层、数据链接层和物理层的层次结构,每个层都有特定的任务,确保数据的高效、可靠传输。枚举原理是PCIe系统初始化的重要步骤,它涉及设备的发现、配置和资源分配。枚举过程中,系统会识别出连接的设备类型,如Type0或Type1配置头空间,并根据设备需求分配相应的Bus、Device和Function号。

资源分配是PCIe系统中不可或缺的部分。对于非桥设备(如端点设备),系统会为其分配I/O端口和内存资源。例如,Device0可能被分配64KB的I/O Memory和256Byte的I/O Port。而桥设备(如PCI Bridge)则负责管理其下游设备的资源,通过配置空间中的寄存器来设定IO和Memory Routing。

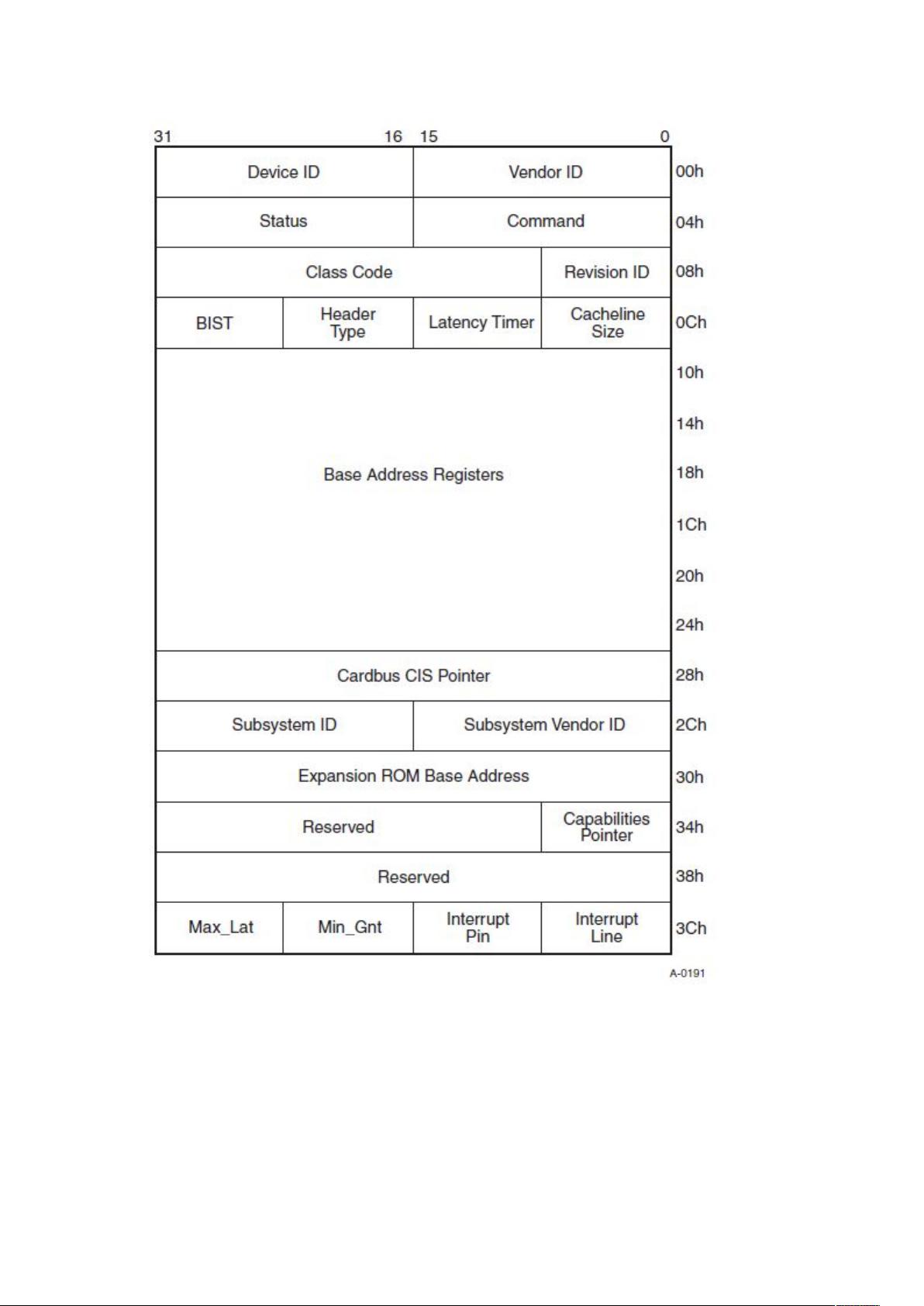

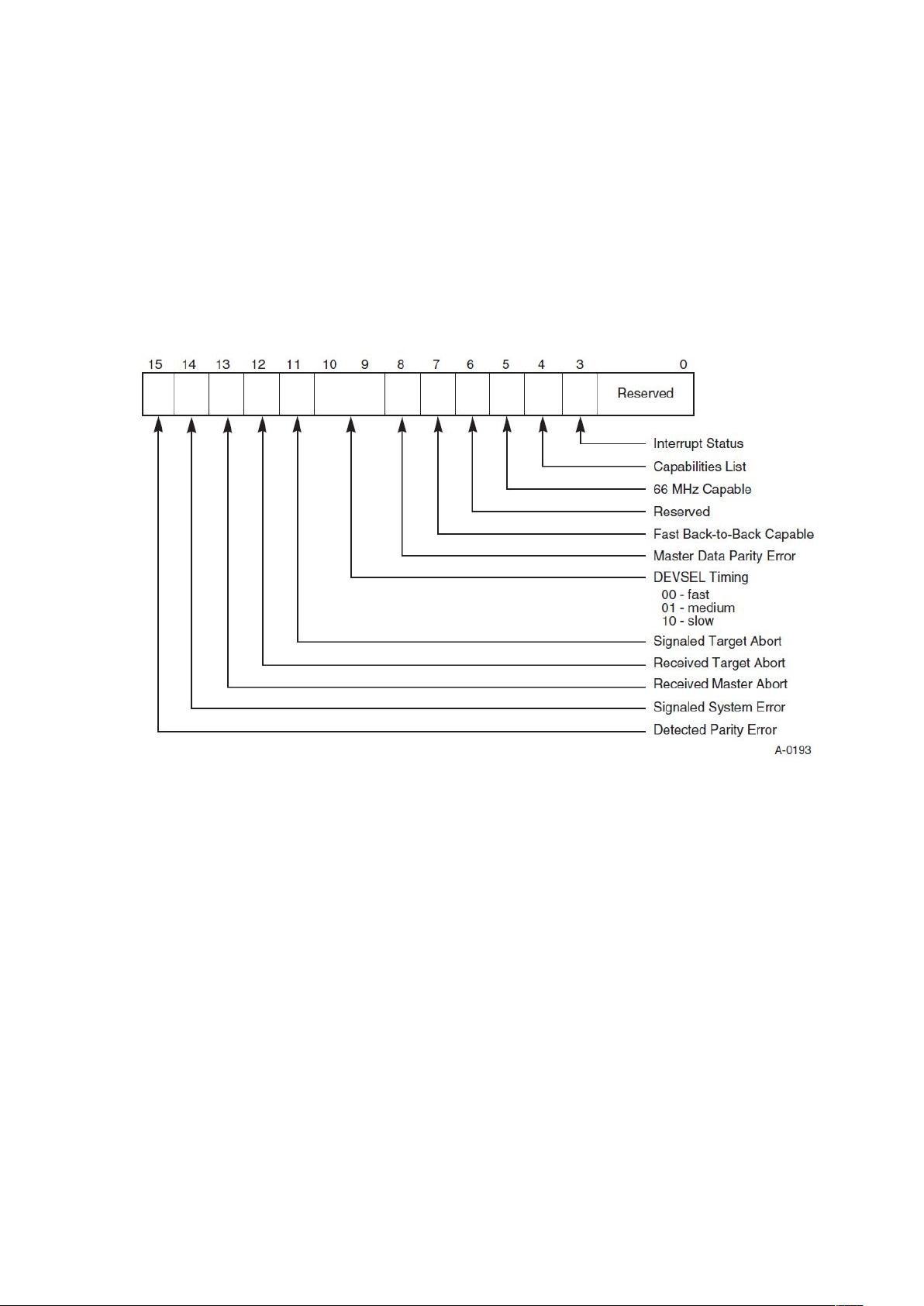

PCI配置空间包含两种类型:Type00h(适用于Agent设备)和Type01h(适用于Bridge设备)。Type00h中的VendorID和DeviceID标识设备制造商和型号,Status和Command寄存器控制设备的状态和功能。BaseAddressRegisters(BAR)定义了设备在系统内存或I/O空间的映射。Type01h配置空间除了与Type00h类似的寄存器外,还包括SubordinateBusNumber、SecondaryBusNumber和PrimaryBusNumber,这些用于确定桥连接的总Bus范围。Base和Limit寄存器则定义了桥所管理的地址空间范围。

总结来说,这份文档提供了深入的PCIe技术知识,包括其硬件架构、软件配置和资源管理,对进行PCIe调试和IP核配置具有很高的参考价值。特别是对于XILINX PCIe IP核的使用者,这份资料将有助于理解和优化PCIe系统的性能。

2020-05-28 上传

2021-05-22 上传

2022-10-30 上传

2022-07-02 上传

2023-10-07 上传

2021-12-02 上传

2021-10-24 上传

2019-12-09 上传

2020-07-22 上传

zairenjian1234

- 粉丝: 15

- 资源: 26

最新资源

- 掌握压缩文件管理:2工作.zip文件使用指南

- 易语言动态版置入代码技术解析

- C语言编程实现电脑系统测试工具开发

- Wireshark 64位:全面网络协议分析器,支持Unix和Windows

- QtSingleApplication: 确保单一实例运行的高效库

- 深入了解Go语言的解析器组合器PARC

- Apycula包安装与使用指南

- AkerAutoSetup安装包使用指南

- Arduino Due实现VR耳机的设计与编程

- DependencySwizzler: Xamarin iOS 库实现故事板 UIViewControllers 依赖注入

- Apycula包发布说明与下载指南

- 创建可拖动交互式图表界面的ampersand-touch-charts

- CMake项目入门:创建简单的C++项目

- AksharaJaana-*.*.*.*安装包说明与下载

- Arduino天气时钟项目:源代码及DHT22库文件解析

- MediaPlayer_server:控制媒体播放器的高级服务器