VLSI自动布局布线设计:基于库单元的方法

"本资源主要介绍了VLSI物理设计的基础,特别是关于基于库单元的自动布局布线设计。内容涵盖自动布局布线的概述、使用的工具、输入输出信息格式以及不同类型的布局布线流程。此外,还提到了设计目标、 Cadence 的Silicon Ensemble (SE)工具以及输入文件如setup文件、库单元信息文件等的重要作用。"

在VLSI设计领域,自动布局布线是关键步骤,特别是在处理大规模集成电路(VLSI)时,涉及数百万门电路的物理设计。设计过程通常从逻辑综合后的门级网表开始,结合特定工艺的库单元信息,通过布局布线工具进行布图规划、电源规划、IO单元布局、标准单元布局和布线,最终完成版图设计。设计目标不仅包括确保电路能正常工作(布通),还要满足严格的时序要求和功耗限制。

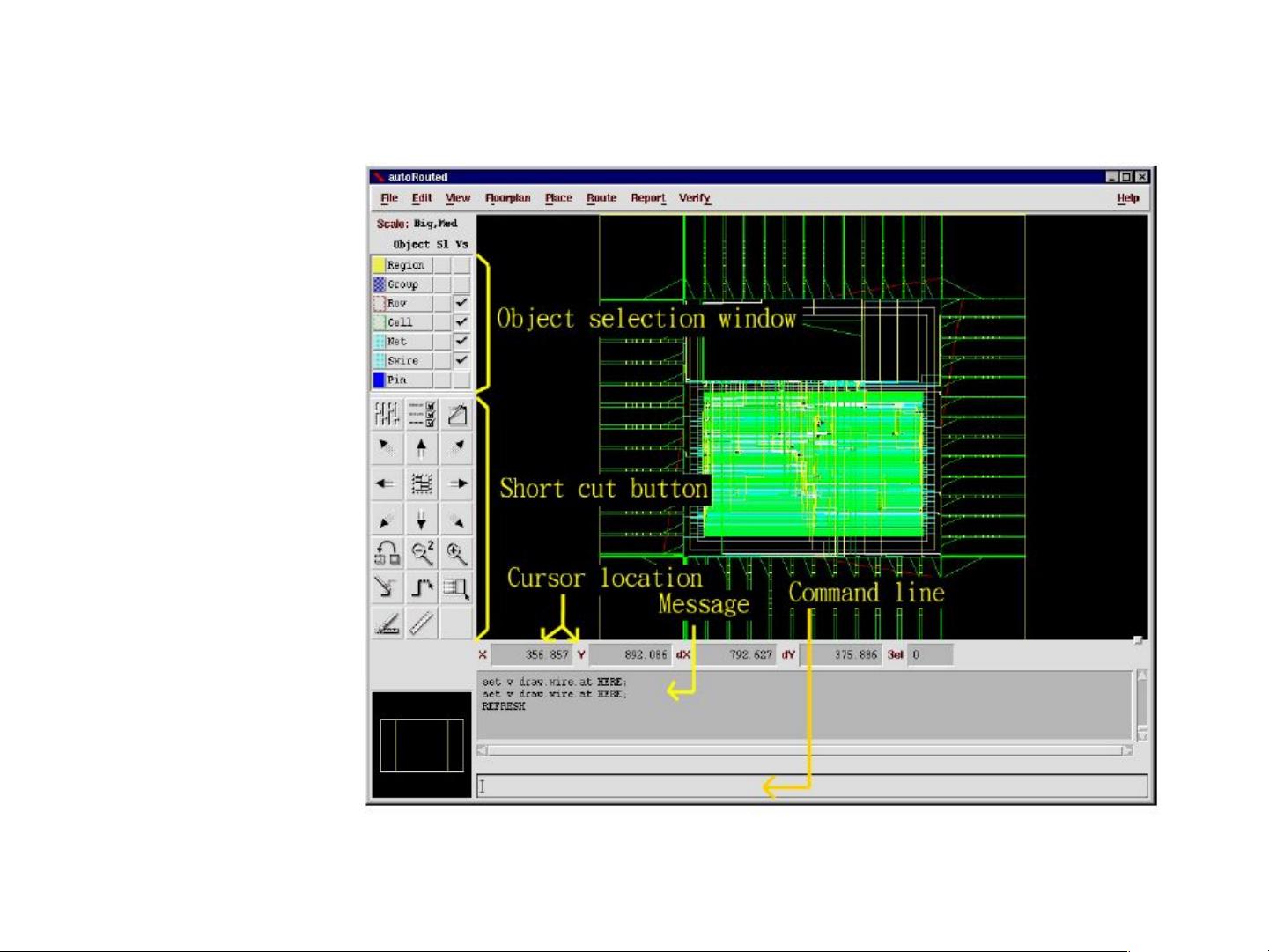

常用的VLSI布局布线工具有Cadence的Silicon Ensemble (SE),例如其中的Qplace布局器和UltraRouter布线器,以及Synopsys的Astro等。这些工具接收多种格式的输入文件,如LEF(Library Exchange Format)用于描述库单元,CTLF(Compiled Timing Library Format)提供时序信息,还有用户的设计数据如.V文件和DEF文件等。同时,SE工具提供了图形化操作界面,便于用户进行交互式设计。

布局布线可以基于不同的策略进行,如基于连线的布局布线强调连接的优化,而基于时序驱动的布局布线则更注重满足电路的时序约束。此外,还有考虑功耗的布局布线,旨在降低芯片的功耗。

在开始设计前,设置好setup文件至关重要,它包含环境变量设置,可以作为自动执行的脚本。se.env文件用于设定系统运行环境,而se.fin则用于保存软件关闭前的状态。DLC.init文件则是Central Delay Calculator初始化所需的。

库单元信息文件,如LEF和CTLF,提供了库单元的几何形状和时序特性,而GCF(General Constraints Format)文件则用于定义设计约束。理解并正确使用这些格式文件是成功进行自动布局布线设计的关键。

自动布局布线设计是VLSI物理设计的核心,涉及到复杂的工具使用、格式文件处理和优化策略。通过掌握这些基础知识,设计者能够有效地应对复杂的VLSI设计挑战,实现高效、高质量的集成电路设计。

相关推荐

1423 浏览量

2757 浏览量

115 浏览量

u011338897

- 粉丝: 0

- 资源: 5

最新资源

- 初级java笔试题-jas497_476:EECS476的最终项目

- 完整版调用外部命令.rar

- 玫瑰花图标下载

- DO_AN_LOD

- Library:生成一个图书馆区,玩家可以在那里轻松获取书籍,并受制于

- MACS:MACS-ChIP-Seq的基于模型的分析

- scrapy_climatempo:Objetivo

- 完整版调整窗口大小.rar

- 抄送缓存

- 可爱大象图标下载

- goit-js-hw-08-gallery:https

- Công Cụ Đặt Hàng Của Long Châu Express-crx插件

- 完整版调整控件大小2.rar

- semiotic-standard:适用于所有商用跨星公用事业升降机和重型运输航天器。 — 2078年4月16日

- 可爱动物头像小图标下载

- guowen.xu.github.io