AD7705/AD7706

–7–REV. A

Pin No. Mnemonic Function

10 REF IN(–) Reference Input. Negative input of the differential reference input to the AD7705/AD7706.

The REF␣ IN(–) can lie anywhere between V

DD

and GND provided REF␣ IN(+) is greater

than REF␣ IN(–).

11 AIN2(–)[AIN3] AD7705: Negative input of the differential analog Input Channel 2. AD7706: Analog Input

Channel 3.

12 DRDY Logic Output. A logic low on this output indicates that a new output word is available from

the AD7705/AD7706 data register. The DRDY pin will return high upon completion of a

read operation of a full output word. If no data read has taken place between output updates,

the DRDY line will return high for 500 × t

CLK␣ IN

cycles prior to the next output update.

While DRDY is high, a read operation should neither be attempted nor in progress to avoid

reading from the data register as it is being updated. The DRDY line will return low again

when the update has taken place. DRDY is also used to indicate when the AD7705/AD7706

has completed its on-chip calibration sequence.

13 DOUT Serial Data Output with serial data being read from the output shift register on the part. This

output shift register can contain information from the setup register, communications regis-

ter, clock register or data register, depending on the register selection bits of the Communica-

tions Register.

14 DIN Serial Data Input with serial data being written to the input shift register on the part. Data

from this input shift register is transferred to the setup register, clock register or communica-

tions register, depending, on the register selection bits of the Communications Register.

15 V

DD

Supply Voltage, +2.7 V to +5.25 V operation.

16 GND Ground reference point for the AD7705/AD7706’s internal circuitry.

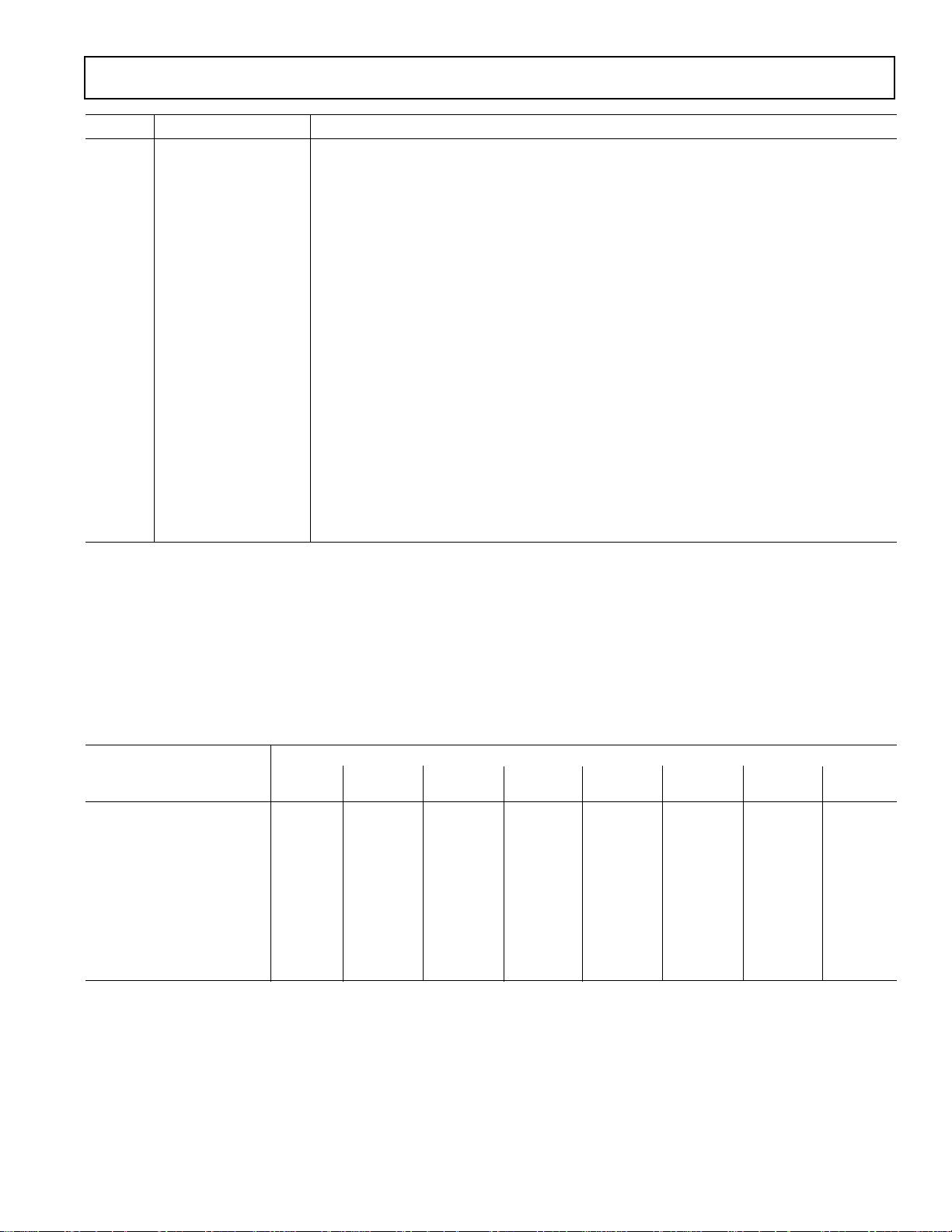

OUTPUT NOISE (5 V OPERATION)

Table I shows the AD7705/AD7706 output rms noise for the selectable notch and –3␣ dB frequencies for the part, as selected by FS0

and FS1 of the Clock Register. The numbers given are for the bipolar input ranges with a V

REF

of +2.5␣ V and V

DD

= 5 V. These

numbers are typical and are generated at an analog input voltage of 0␣ V with the part used in either buffered or unbuffered mode. Table II

meanwhile shows the output peak-to-peak noise for the selectable notch and –3 dB frequencies for the part. It is important to note that

these numbers represent the resolution for which there will be no code flicker. They are not calculated based on rms noise but on peak-to-peak

noise. The numbers given are for bipolar input ranges with a V

REF

of +2.5 V and for either buffered or unbuffered mode. These num-

bers are typical and are rounded to the nearest LSB. The numbers apply for the CLK DIV bit of the Clock Register set to 0.

Table I. Output RMS Noise vs. Gain and Output Update Rate @ 5 V

Filter First Typical Output RMS Noise in V

Notch and O/P –3␣ dB Gain of Gain of Gain of Gain of Gain of Gain of Gain of Gain of

Data Rate Frequency 1248163264128

MCLK IN = 2.4576 MHz

50␣ Hz 13.1␣ Hz 4.1 2.1 1.2 0.75 0.7 0.66 0.63 0.6

60␣ Hz 15.72␣ Hz 5.1 2.5 1.4 0.8 0.75 0.7 0.67 0.62

250␣ Hz 65.5␣ Hz 110 49 31 17 8 3.6 2.3 1.7

500␣ Hz 131␣ Hz 550 285 145 70 41 22 9.1 4.7

MCLK IN = 1 MHz

20␣ Hz 5.24␣ Hz 4.1 2.1 1.2 0.75 0.7 0.66 0.63 0.6

25␣ Hz 6.55␣ Hz 5.1 2.5 1.4 0.8 0.75 0.7 0.67 0.62

100␣ Hz 26.2␣ Hz 110 49 31 17 8 3.6 2.3 1.7

200␣ Hz 52.4␣ Hz 550 285 145 70 41 22 9.1 4.7