High-performance flip chip packages with copper pillar bumping

Global SMT & Packaging

May 2006 www.globalsmt.net

High-performance flip

chip packages with

copper pillar bumping

High-performance flip

chip packages with

copper pillar bumping

28

Copper pillar

bumping (CPB)

Flip chip technology is keeping

pace with the increasing

connection density of the ICs

and is capable of transferring

semiconductor performance

to the printed circuit board.

The pitch is growing smaller,

which means flip chip

technology with solder bumps

will unavoidably run up against

its technical limitations. The

reason for this is the spherical

geometry of the bumps. The

solution to this problem is

copper pillars. In this contact

technology for flip chip

assembly, special cylindrical

copper connections function

with a solder deposit instead of

the usual solder ball bumps to

form the connecting element

between semiconductor and

substrate. The CPBs are

manufactured in a two-stage

electroplating process.

The result: improved

reliability and enhanced

electrical and thermal

connection characteristics,

greater connection density

with narrow pitching and

RoHS conformity. Production

is then comparable to standard

wafer level bumping and is

cost-effective.

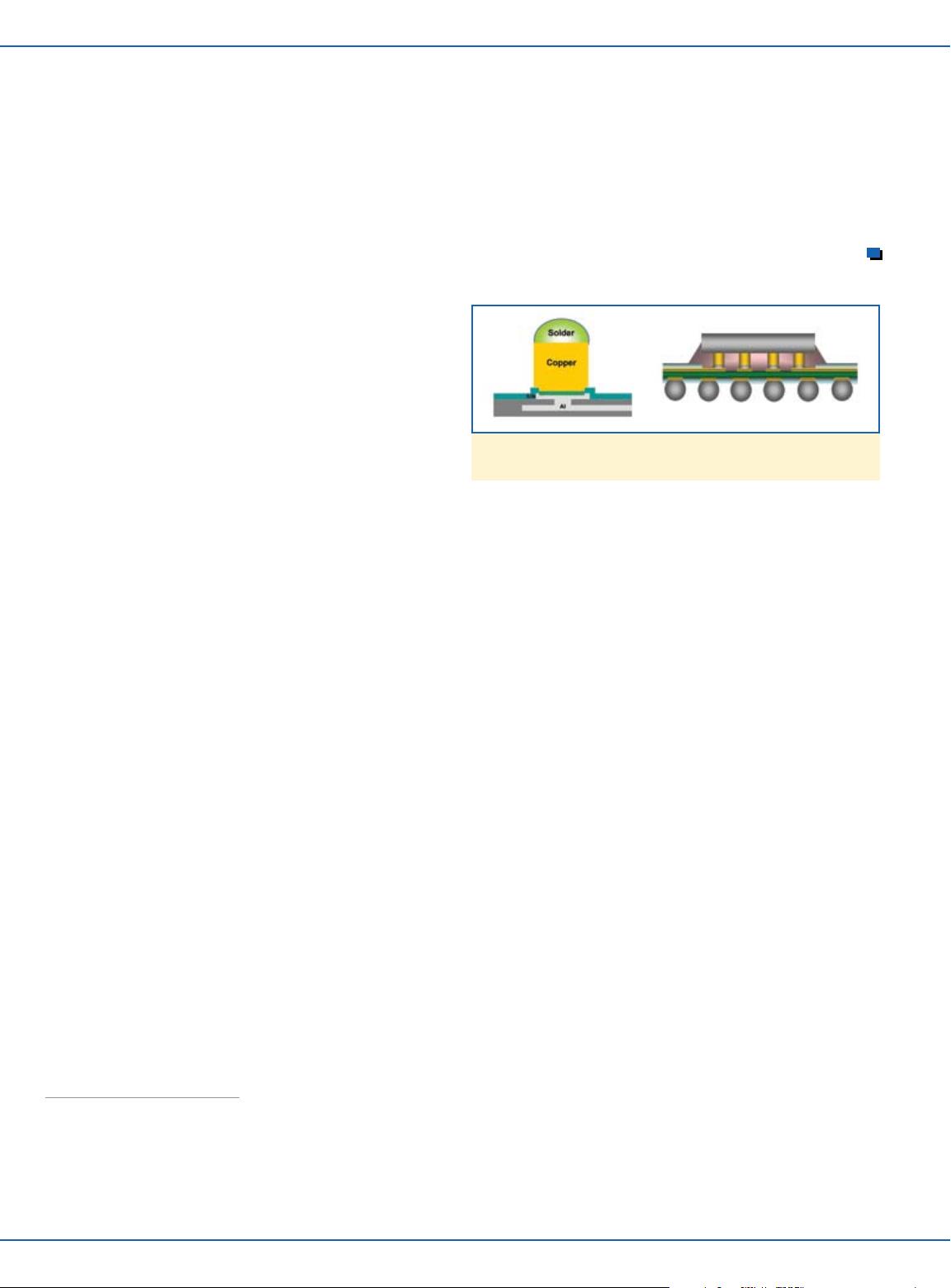

The copper pillar bump

comprises two elements: the

approx. 60 to 70 µm high

copper cylinder and a solder

cap, for which latter eutectic

tin-lead solder or a lead-free

alloy with a high tin content

can be used. Whereas the

solder cap provides only

the mechanical connection

between IC and wiring or PCB,

the copper pillar provides the

electrical contact.

Development of an innovative

chip technology is not all

that is needed to achieve

successful market positioning

of new products. A further

important factor is advanced

housing and processing

technology that does not

hamper IC performance. In

this regard, the announcement

by Intel (Electronics Weekly

27.01.2006: ‘Copper Posts

Replace Solder Balls at Intel’)

is highly significant in relation

to future developments. To

package its latest 65 nm Dual

Core Processors (Presler and

Yonah) Intel is using copper

pillar bumps on the chip side,

which are then soldered to

the PCB substrate using flip

chip technology. Prismark

draws similar conclusions in

his latest study from 2005 on

the development of “Bumped

Wafer Production for Flip

Chip Technology.” In this

study, the author predicts that

electroplating will be established

worldwide over the next 3 years

as the most important bumping

method. On the other hand,

the proportion of copper pillar

bumped chips to solder ball

bumps will rise at an increasing

rate and will successively

replace wire bonding in

processor packaging.

The design and realization

of extremely thin µQFN (quad

flat no lead) packages is also

facilitated by use of copper

pillar bumps (CPB). The CPBs

can be mounted directly onto

the leadframe connections. The

advantage lies in the fact that

on-site designing companies

and medium-sized companies

in particular have increased

their flexibility to the point

where they are capable of

designing and manufacturing

customer-specific, ultraflat SMT

packages. In the final analysis,

this means packaging can be

brought back home to Europe

from the Far East for selected

applications.

Figure 1. Structure and cross-section of copper pillar bumps

subsequent to separation and assembly.

Keywords:

Copper Pillar Bump,

Flip Chip,

Electroplating,

IC Interconnection.

Joachim Kloeser

AEMtec GmbH, Berlin, Germany

Ernst-A. Weißbach

HTC Consulting, Baldham, Germany

www.aemtec.com

In comparison: the

conventional solder ball

bump functions as both the

mechanical and electrical

connection. The copper pillar

has yet another advantage

over the solder ball: the pillar

bump, which is the same

height as the spherical solder

ball bump, is also narrower.

Copper pillar bump geometry

thus not only facilitates a finer

connection grid, the narrow

connections also enhance the

electrical characteristics of the

connection, with improved

thermal behaviour due to the

high proportion of copper

(greater conductivity). The

pillar bump can also take

on different forms by way of

solutions to the problems of

increasing voltage and heat

production within certain

semiconductors.

In the conventional solder

bump process, the solder ball

bumps undergo deformation

in the process of remelting

and reflow soldering to the

substrate or printed circuit

board. This results in unequal

distances between the bumps,

a factor that is difficult to

monitor and control. During

chip assembly, the underfill

between IC and substrate tends

to flow mainly into the larger

gaps between the solder

balls and leave smaller gaps

unfilled. The resulting hollow

spaces have a negative effect

on component reliability.

With the copper pillar bump,

connection deformation is

greatly reduced due to the

much smaller amount of solder

used. The cylindrical copper

element also retains its form in

the remelt and reflow process.

The uniform distances between

the bumps mean fewer hollows

are left after the underfill

process as well as higher levels

of processing quality and

component reliability. The

copper pillar technology is

equally suitable for flip chip

packaging in the established

standard housings CSP, QFN,

SOT, TO-220, etc. and in

on-board flip chip applications.

The innovative chip

contacting in this technology

enhances the electrical and

thermal characteristics of the

IC, thus improving reliability.

Pillar bump positioning

on the die is also a flexible

procedure. Advantage: this

contributes to solutions of

design problems and opens up

new potential in IC design.

One approach involves

strategic positioning of the

pillar bumps at hotspots to

carry off the heat dissipating

from the chip.