多路ADC系统:DSP与CPLD协同设计与硬件详解

PDF格式 | 171KB |

更新于2024-08-28

| 91 浏览量 | 举报

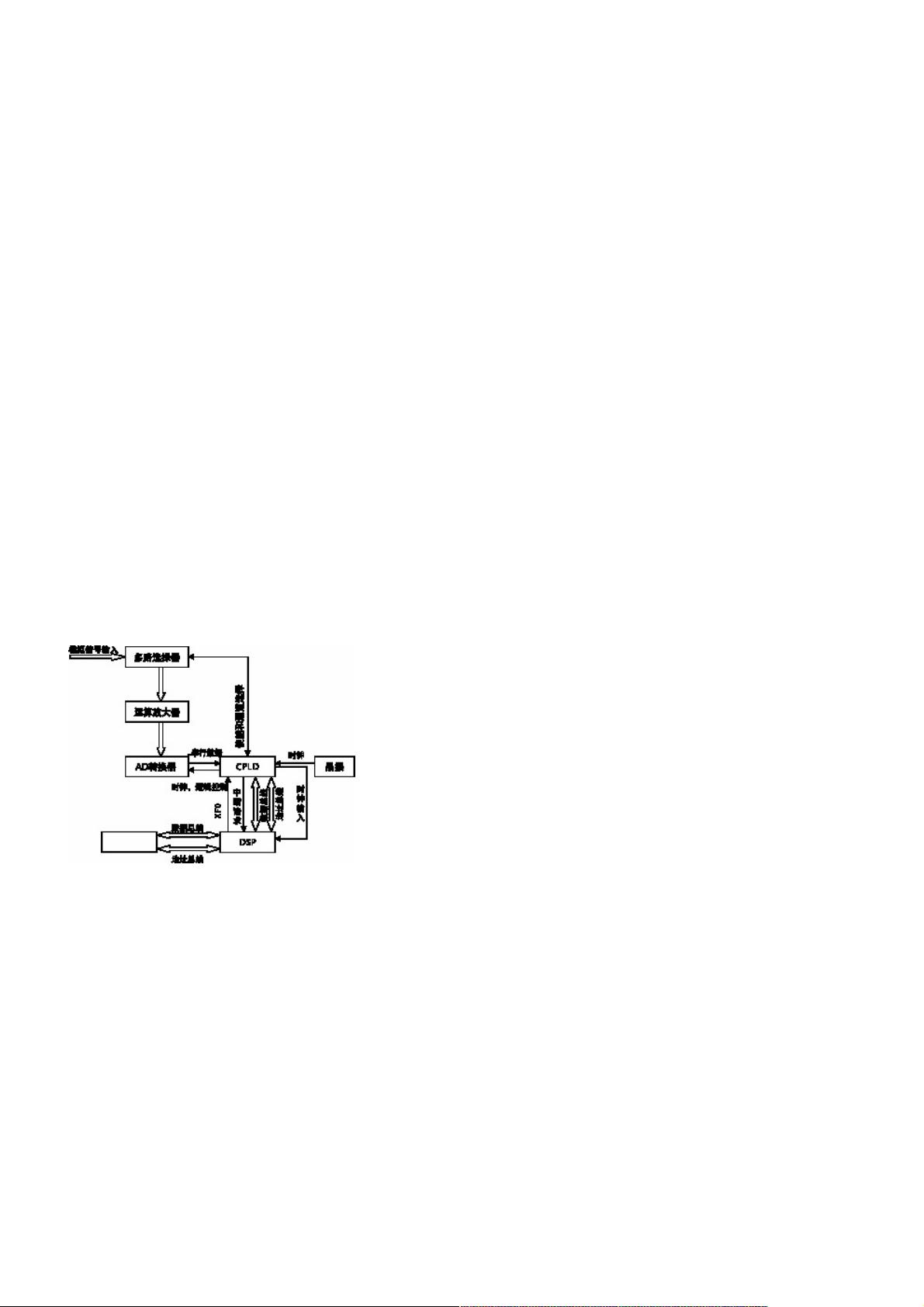

本文主要探讨了基于数字信号处理器(DSP)和可编程逻辑器件(CPLD)技术的多路ADC系统的设计。在引言部分,作者强调了随着电子技术的进步,数字信号处理任务的复杂性提升,ADC在模拟信号数字化过程中的关键作用。多路ADC系统的设计旨在通过集成DSP和CPLD,简化电路设计,提高系统的灵活性和可移植性。

系统的核心硬件部分采用了MAXIM公司的低功耗16位逐次逼近型ADC MAX1162。这款ADC器件的特点包括自动关断功能,能够快速唤醒至工作状态,且支持高速SPI/QSPI/MICROWIRE接口,方便与数字逻辑设备通信。它使用单一的+5V模拟电源,同时配备独立的数字电源引脚,确保了与不同电压环境的兼容性。模拟信号通过REF引脚连接外部参考电压,通过AVDD和AGND分别供给模拟和数字地,以稳定工作。ADC的工作模式控制由CS引脚负责,SCLK作为串行时钟驱动转换过程,而DOUT则输出串行数据。

系统的关键控制器是来自TI的TMS320VC33-150浮点数字信号处理器,其24位地址总线提供了强大的计算能力。TMS320VC33负责协调ADC的采样、数据处理和系统控制,实现了对多路模拟输入信号的高效处理。这一体系结构的优势在于,通过将数据处理任务交给DSP,可以专注于优化算法和实时性能,同时利用CPLD进行灵活的配置和扩展。

本文设计的多路ADC系统结合了高性能的数字信号处理技术和可编程逻辑的灵活性,实现了模拟信号的高效数字化,适用于各种需要处理大量模拟输入的电子应用领域,如信号采集、工业自动化或音频处理等。这种设计方法不仅降低了硬件复杂度,还提高了系统的性能和适应性。

相关推荐

weixin_38701312

- 粉丝: 8

最新资源

- 久度免费文件代存系统 v1.0:全技术领域源码分享

- 深入解析caseyjpaul.github.io的HTML结构

- HTML5视频播放器的实现与应用

- SSD7练习9完整答案解析

- 迅捷PDF完美转PPT技术:深度识别PDF内容

- 批量截取子网页工具:Python源码分享与使用指南

- Kotlin4You: 探索设计模式与架构概念

- 古典风格茶园茶叶酿制企业网站模板

- 多功能轻量级jquery tab选项卡插件使用教程

- 实现快速增量更新的jar包解决方案

- RabbitMQ消息队列安装及应用实战教程

- 简化操作:一键脚本调用截图工具使用指南

- XSJ流量积算仪控制与数显功能介绍

- Android平台下的AES加密与解密技术应用研究

- Место-响应式单页网站的项目实践

- Android完整聊天客户端演示与实践