74LS161与74LS00实现计数器应用实验报告

需积分: 10 45 浏览量

更新于2024-09-11

收藏 1.12MB DOC 举报

"西工大短学时数字电路实验课实验报告,主要涉及计数器的应用,使用了74LS90和74LS161集成电路,实现了十进制和24进制计数,以及100分频的50%占空比信号。"

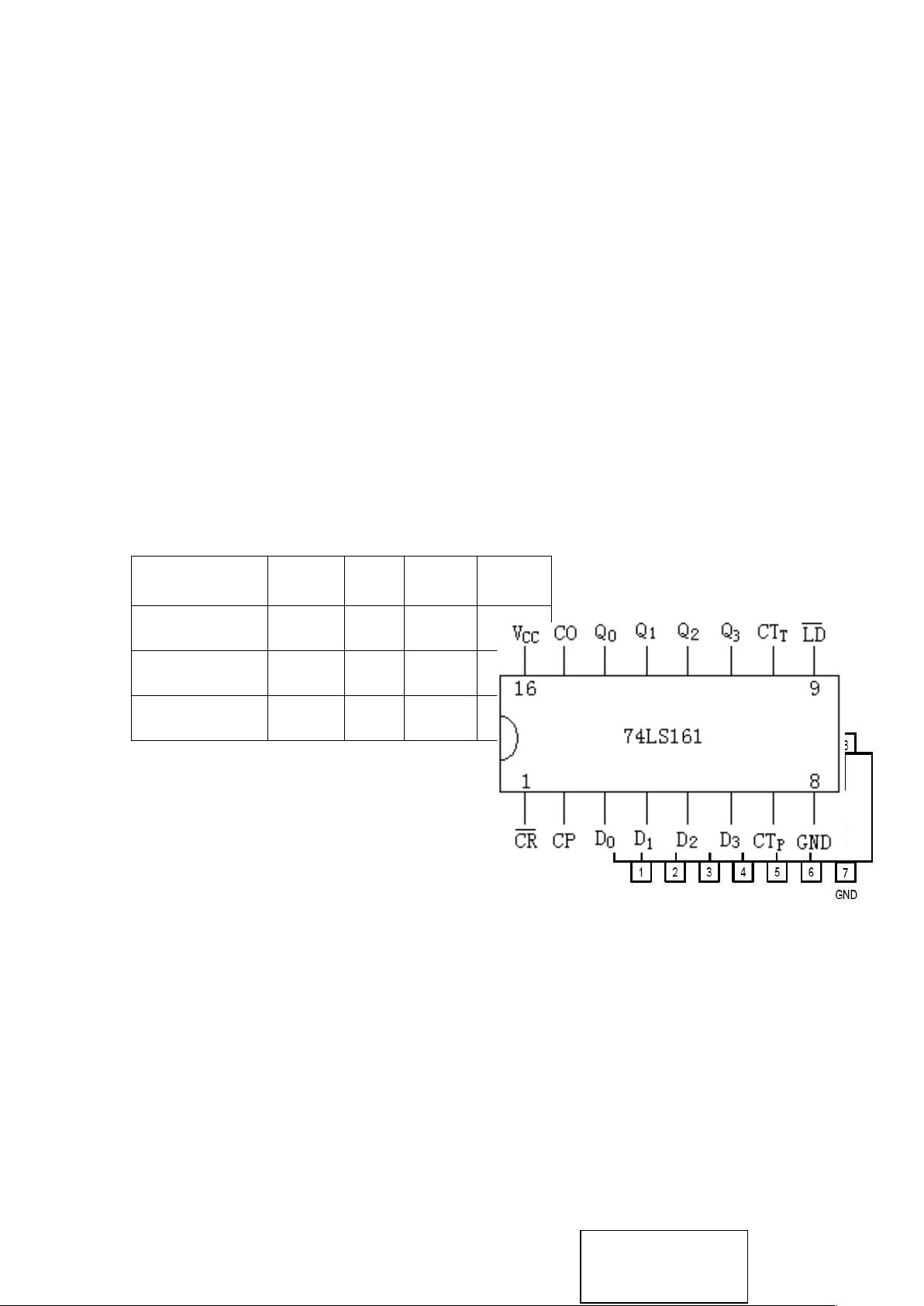

本次实验的主要目的是学习计数器的基本结构,并熟悉中规模计数器74LS90和74LS161的逻辑功能和应用。74LS90是一个双四进制计数器,常用于实现二进制或十进制计数。而74LS161则是一个四位二进制计数器,具备异步清零和同步置数功能,可用来构建更复杂的计数序列。

实验中,学生使用74LS161通过同步置数和异步清零的方式实现了计数器从0到9的十进制计数。同步置数是通过在时钟脉冲上升沿的同时改变计数器的初始状态来设定计数值,而异步清零则是在不受时钟脉冲控制的情况下,使计数器回到零状态。

此外,实验还利用74LS161和74LS00集成电路实现了24进制计数。24进制计数器通常需要两个或更多独立的计数器级联,这里可能是通过设置74LS161的不同输入条件,使得两个计数器在特定的计数模式下协同工作,形成0到23的计数序列。级联计数器允许扩展计数范围,以满足更复杂的计数需求。

为了实现100分频,也就是将输入时钟频率降低100倍,同时保持50%的占空比,学生设计了一个由10进制、5进制和2进制计数器组成的级联系统。这种级联计数方法确保了每个阶段在特定时刻翻转,最终输出的信号周期是输入时钟周期的100倍。占空比为50%意味着高电平和低电平的时间相等,这对于很多数字系统来说是非常重要的。

实验结果显示,学生成功地完成了上述所有任务,包括同步置数和异步清零的十进制计数、24进制计数以及100分频的50%占空比信号生成。然而,在第一个实验中,接数字显示器时出现了错误,这可能是因为未正确理解74LS161的输出引脚定义或者接线时的疏忽。

这次实验提供了实践数字逻辑电路和计数器应用的宝贵经验,不仅加深了对计数器内部工作原理的理解,还锻炼了使用集成电路设计和调试数字系统的能力。

2010-05-03 上传

2019-04-29 上传

2020-05-20 上传

2023-05-10 上传

2024-11-11 上传

2023-12-04 上传

2023-05-21 上传

2023-05-19 上传

2023-06-06 上传

zhuzhuzhu11111

- 粉丝: 0

- 资源: 8