"EDA技术实用教程第3章:VHDL设计初步及多路选择器的VHDL描述"

版权申诉

86 浏览量

更新于2024-03-01

收藏 1009KB PPT 举报

本文主要介绍了可编程逻辑器件(EDA)中的VHDL设计初步内容。它包括了组合电路的VHDL描述以及2选1多路选择器及其VHDL描述,以及实体表达、实体名、端口语句和端口信号名、端口模式、数据类型和结构体表达等方面的内容。

在第3章 VHDL设计初步中,首先介绍了组合电路的VHDL描述。组合电路是指各种逻辑门的组合,根据输入信号的不同组合产生不同的输出信号。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种用于描述数字电路和系统的硬件描述语言。VHDL描述可以精确描述电路的结构、行为和功能,可以有效地进行数字电路的设计和验证。

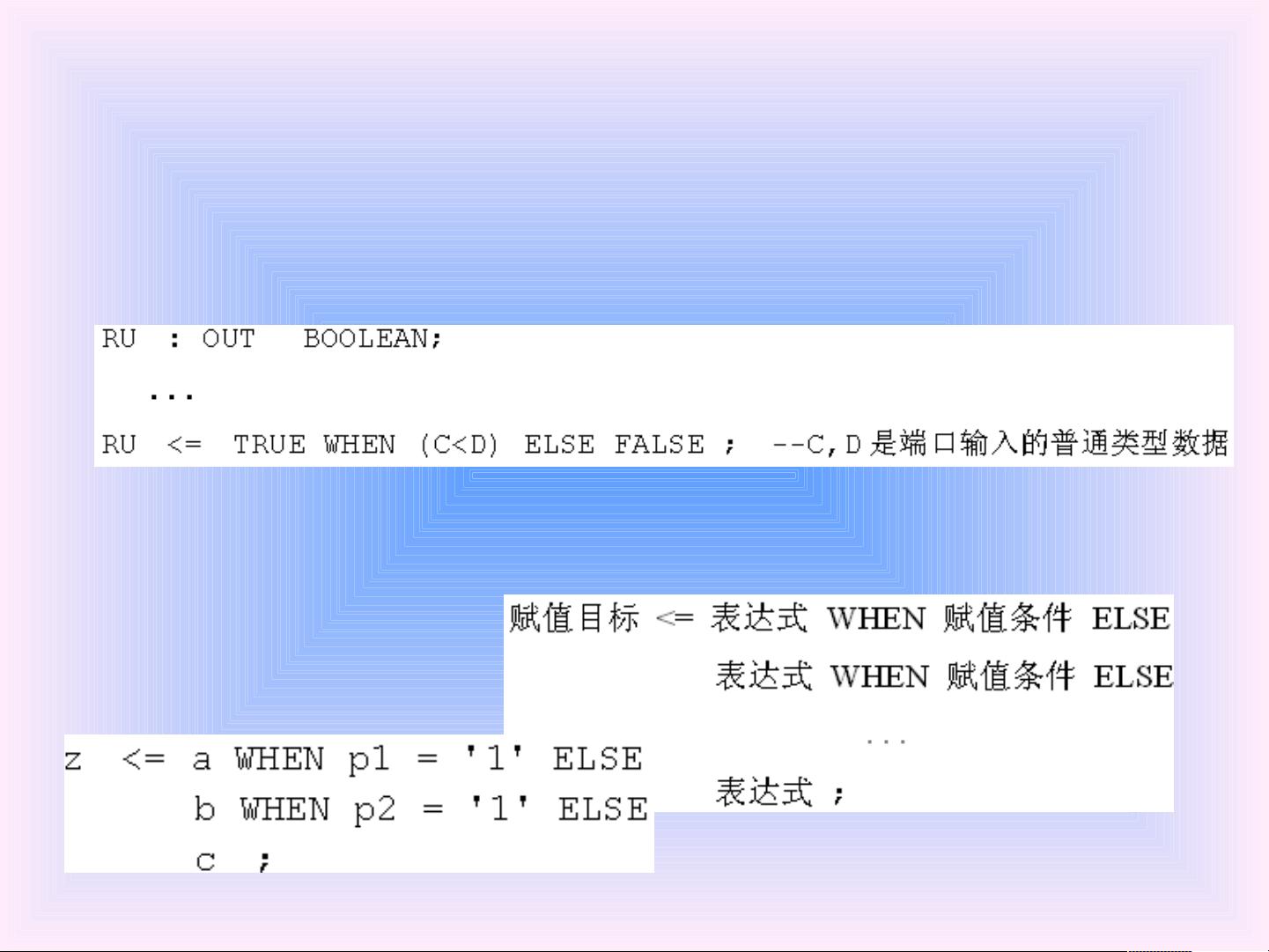

3.1.1中介绍了2选1多路选择器及其VHDL描述。多路选择器是一种常用的组合电路,具有多个输入信号,通过控制信号选择其中一个输入信号作为输出。VHDL描述可以清晰地描述多路选择器的输入输出关系,以及控制信号对选择器的作用。

在介绍组合电路的VHDL描述时,需要关注几个方面。首先是实体表达,实体名和端口语句以及端口信号名。实体是描述电路元件的一个概念,它包括了电路元件的功能以及输入输出的端口。端口语句和端口信号名则具体描述了电路元件的输入输出端口。端口模式包括了IN、OUT、INOUT和BUFFER四种类型,分别表示输入端口、输出端口、双向端口和缓冲端口。这些端口模式在VHDL描述中扮演了重要的角色,可以明确电路元件的输入输出关系。

另外,数据类型和结构体表达也是VHDL描述中需要关注的内容。在VHDL语言中,包括了多种数据类型,如BIT等,可以根据电路元件的需要选择不同的数据类型进行描述。结构体表达则可以描述电路元件的结构和组成,有利于对电路元件进行组合和分析。

总之,VHDL设计初步是EDA技术中非常重要的一部分,它可以帮助工程师们有效地进行数字电路的设计和验证。通过对组合电路的VHDL描述的学习,可以更好地理解数字电路的工作原理,为进一步的数字电路设计奠定基础。希望本文能够对相关领域的学习和研究有所帮助。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-06-11 上传

2022-06-29 上传

2022-06-11 上传

2022-06-11 上传

2022-06-11 上传

2022-06-11 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- XML文档对象模型(XML DOM)研究与应用

- DWR中文教程适合初学开发人员的最佳文档

- 新版设计模式手册[C#].pdf

- Professional JavaScript For Web Developers 2nd edition

- ibatis开发指南(含基础、高级部分)

- Beginning ASP.NET E Commerce In C Sharp From Novice To Professional

- Learning the vi and Vim Editors 7th Edition Jul 2008

- 网络工程的验收与鉴定.doc

- CSS.Mastery.Advanced.Web.Standards.Solutions.pdf

- AD与DA转换的pdf详细文档

- extjs详细教程-中文版

- 電腦做什麼事 0 序章 關於電腦

- 英语学习英语的资料,不是图片,视频

- Web_Service开发指南

- c#的习题,绝对实用,不下后悔

- MCTS70-640SelfPacedTrainingKit.pdf