EDA数字钟设计与仿真:分频电路与数据选择器实现

需积分: 16 80 浏览量

更新于2024-09-16

2

收藏 351KB DOCX 举报

"EDA课设-数字钟及其相关组件的VHDL代码实现"

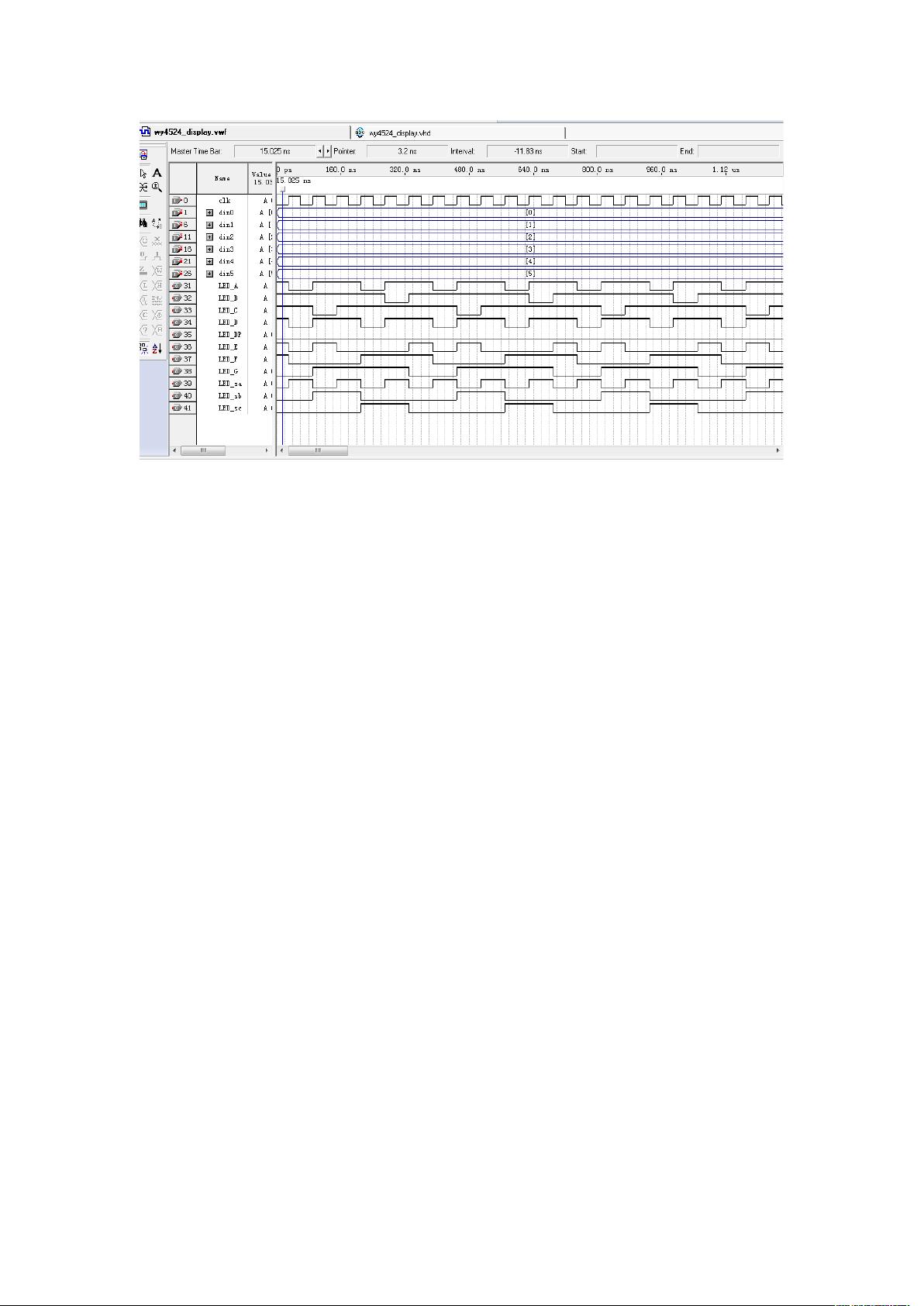

在这个EDA课程设计项目中,学生被要求创建一个数字钟,这通常涉及到硬件描述语言(HDL)如VHDL来设计和仿真数字逻辑系统。下面将详细讨论两个关键组件:二选一数据选择器(MUX)和5分频电路。

1. **二选一数据选择器(MUX)**

在数字系统中,数据选择器是一种多路复用器,它可以根据输入的控制信号从多个输入中选择一个输出。在给定的`edaks_mux2.vhd`文件中,定义了一个二选一数据选择器,其工作原理如下:

- **实体声明**:`entity edaks_mux2`定义了该模块的接口,包括输入`sel`(选择信号),两个输入数据`a`和`b`,以及输出`q`。

- **结构化描述**:`architecture bhv of edaks_mux2`是模块的行为描述,使用了一个进程`process(sel)`来根据`sel`信号的值('0'或'1')选择`a`或`b`作为输出`q`。

2. **5分频电路(Divider)**

分频器是一种电路,可以将输入时钟频率除以一个特定的数值。在这个案例中,`edaks_div5.vhd`文件中的5分频电路用于生成所需时钟频率的信号`q`,其工作方式如下:

- **实体声明**:与MUX类似,`entity edaks_div5`声明了输入时钟`clk`和输出时钟信号`q`。

- **内部信号**:两个额外的信号`clk_up`和`clk_down`以及两个计数器变量`count_up`和`count_down`用于跟踪时钟边沿。

- **行为描述**:两个独立的进程分别处理上升沿和下降沿,通过计数器的递增和重置实现分频。当`count_up`或`count_down`达到4时,它们重置为0,同时`clk_up`和`clk_down`的值也会相应更新,从而在`q`输出上产生5分频的时钟。

数字钟的完整设计通常会包含更多组件,例如七段显示驱动器、计数器和存储器,以实现时间的显示和更新。上述的二选一数据选择器可能用于在小时、分钟和秒钟之间切换显示,而5分频电路则可能用于生成合适的时钟脉冲,这些脉冲驱动计数器以增加时间值。此外,音乐播放器和电梯的源程序可能涉及更复杂的控制逻辑,例如状态机和信号处理,但具体实现不在这个数字钟设计的讨论范围内。

在实际的EDA课设中,学生需要综合这些组件,创建一个完整的VHDL设计,并在软件仿真工具(如ModelSim、Vivado等)中进行验证,确保数字钟的正确运行。完成仿真后,设计可以被下载到FPGA(现场可编程门阵列)或ASIC(应用专用集成电路)硬件上进行实际操作。这样的课程设计有助于学生理解数字逻辑系统的设计和实现,以及如何使用HDL语言进行描述。

578 浏览量

413 浏览量

121 浏览量

105 浏览量

102 浏览量

249 浏览量

m20104600

- 粉丝: 0

- 资源: 1

最新资源

- Proyecto_Mascotas

- 韩国古典风格餐厅网页模板

- 非常好用的截屏.zip

- java源码查看-hx-impulse-engine:用于非视图(服务器端)的简单,开源,基于2D脉冲的物理引擎的HAXE端口

- 1990年第四次人口普查数据(Excel).zip

- Telekomunikacja:电信和信号处理

- C#(VS2010环境) GDI 高效绘曲线图dll

- 上海交通大学应届生论文答辩通用ppt模板.zip

- sreekaransrinath

- RTL8189FS_linux_v5.3.12_28613.20180703.zip

- 计算CPU速度 单位MHz 源代码

- credit-card-validator:简单的Clojure信用卡验证程序

- 室内家居装饰设计网页模板

- 每日计划

- 三种配色清新干净商务风工作汇报ppt模板.rar

- 精美生日贺卡背景图片PPT模板