Verilog HDL深度解析:夏宇闻经典教程

"夏宇闻的《Verilog经典教程》是一本深入讲解Verilog HDL语言的书籍,涵盖了基本语法、不同抽象级别的模型、运算和控制结构、状态机设计以及综合考虑的代码风格。书中通过丰富的实例和思考题帮助读者理解和应用Verilog进行数字系统设计。"

在这本教程中,作者首先引入了数字信号处理的基础概念,这是理解Verilog HDL在现代电子系统中作用的关键。数字信号处理涉及滤波、变换、加密解密、编码解码、纠错等众多数学运算,这些通常可以在通用计算机上用软件实现,如C语言或Pascal。然而,对于实时性要求高的应用,例如军用通信和雷达系统,需要快速、高效的硬件解决方案,这就催生了对Verilog HDL的需求。

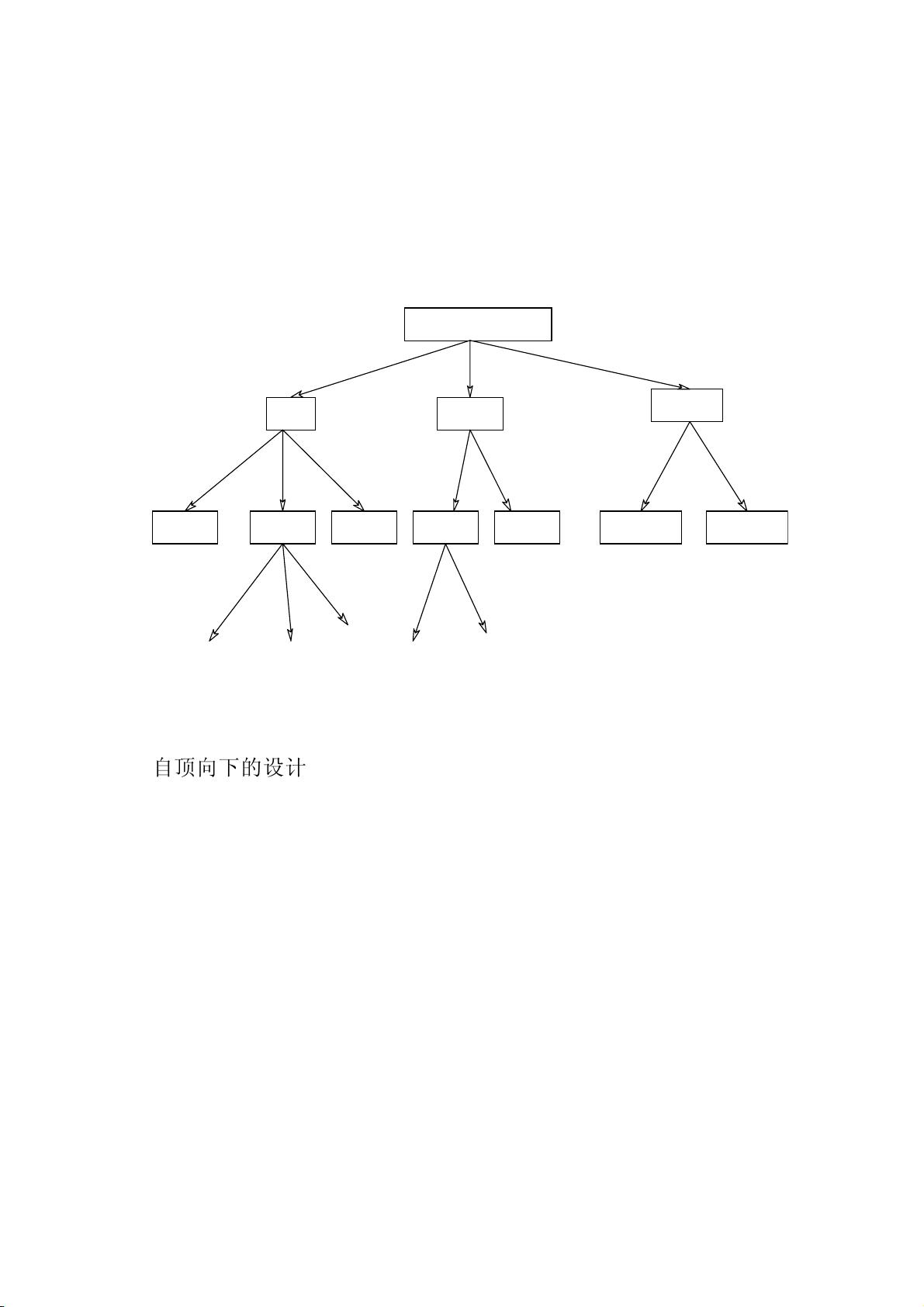

Verilog HDL是一种硬件描述语言,它允许设计者以不同的抽象级别(门级、寄存器传输级、行为级)来描述数字系统。在教程的第一部分,读者将学习如何使用Verilog的基本语法构建电路模型。这包括定义模块、变量、赋值语句以及逻辑操作符。通过这些基础,设计者可以描述复杂的数字逻辑,如加法器、比较器等。

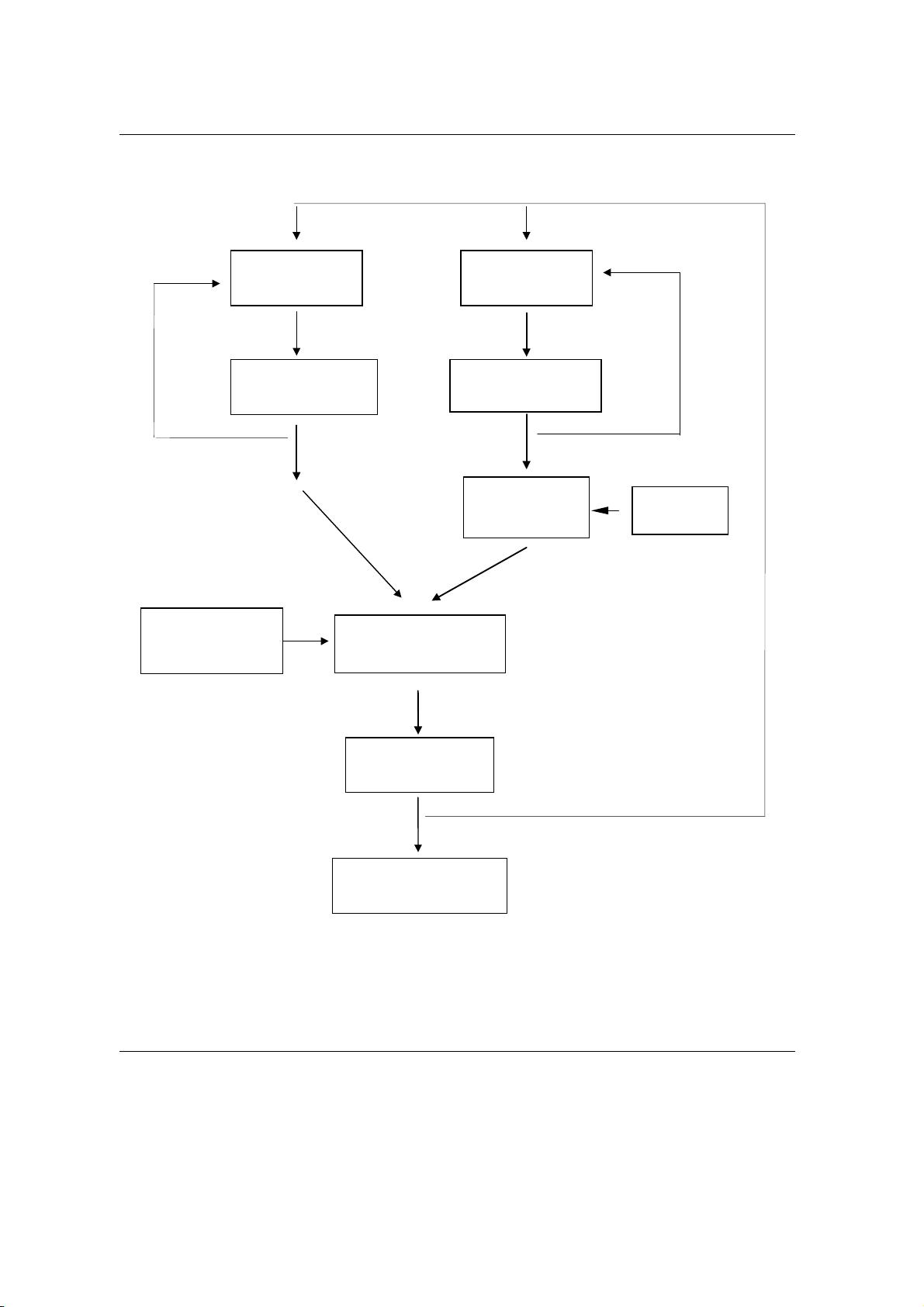

接下来,教程会探讨运算和数据流动控制模型。这部分内容涉及进程同步、条件语句、循环和事件驱动的编程模型,这些都是构建复杂系统,尤其是状态机不可或缺的部分。状态机在数字系统中广泛应用,如控制器、接口协议和序列检测器等。

书中的一个重要部分是关于可综合的Verilog HDL代码风格。可综合代码意味着可以被工具转换为实际的硬件电路。设计者需要了解如何编写能够被FPGA或ASIC制造流程接受的代码,这涉及到避免使用非综合特性,如过程赋值(blocking and non-blocking assignments)的正确使用,以及优化代码以提高效率。

此外,教程还包括了大量的实践例子,这些例子不仅帮助巩固理论知识,还能让读者亲手实践,增强设计技能。每章后的思考题则进一步挑战读者的理解,促进深度学习。

《Verilog经典教程-夏宇闻》是一本全面的指南,旨在帮助读者掌握Verilog HDL语言,理解其在数字信号处理和硬件设计中的应用,以及如何编写高效、可综合的代码。无论你是初学者还是有经验的设计者,这本书都能提供宝贵的学习资源。

2343 浏览量

247 浏览量

点击了解资源详情

2009-07-27 上传

401 浏览量

495 浏览量

笑着刻印在那一张泛黄

- 粉丝: 5

- 资源: 9

最新资源

- 2016“华山杯”CTF php250.rar

- 基于matlab的杂草优化算法IWO仿真+仿真操作录像

- HTML5五角星探照灯文字效果特效代码

- LZW-Compression:第一次提交

- 2018--D--

- 女巫 高清壁纸 新标签页 热门传说 主题-crx插件

- lollor.github.io

- StackStuff:各种测试的源代码

- 辛格洛

- CSS3鼠标经过文字分裂特效特效代码

- win7摄像头软件 计算机自带摄像头

- github_stats_report:与机器共存GitHub Stats报告

- 注册:由ReactJ和nodeJ组成的注册平台

- yamlw_vststask:yamlw的VSTS任务

- RankPook.AdmireTop.gaKlJNg

- Girly 新标签页 热门彩色 高清壁纸 主题-crx插件