基于格雷码计数器的移位时序控制器设计

需积分: 15 45 浏览量

更新于2024-09-17

收藏 308KB DOC 举报

"移位时序控制器研究与设计"

在现代电子系统中,移位时序控制器扮演着至关重要的角色,特别是在高级在轨系统(AOS)帧同步发送器的设计中。这种控制器负责协调数据的传输顺序,确保信息的准确无误地发送。移位时序控制器的主要任务是按照特定的时间序列移动数据,以满足系统的同步需求。

本研究针对移位时序控制器的特点进行了深入分析,揭示了在数据传输过程中可能遇到的问题,如时钟同步误差、数据竞争以及输出毛刺等。这些问题可能导致数据的丢失或错误,从而影响整个系统的性能和稳定性。为了解决这些问题,研究人员提出了一种基于格雷码计数器的新型移位时序控制器设计。

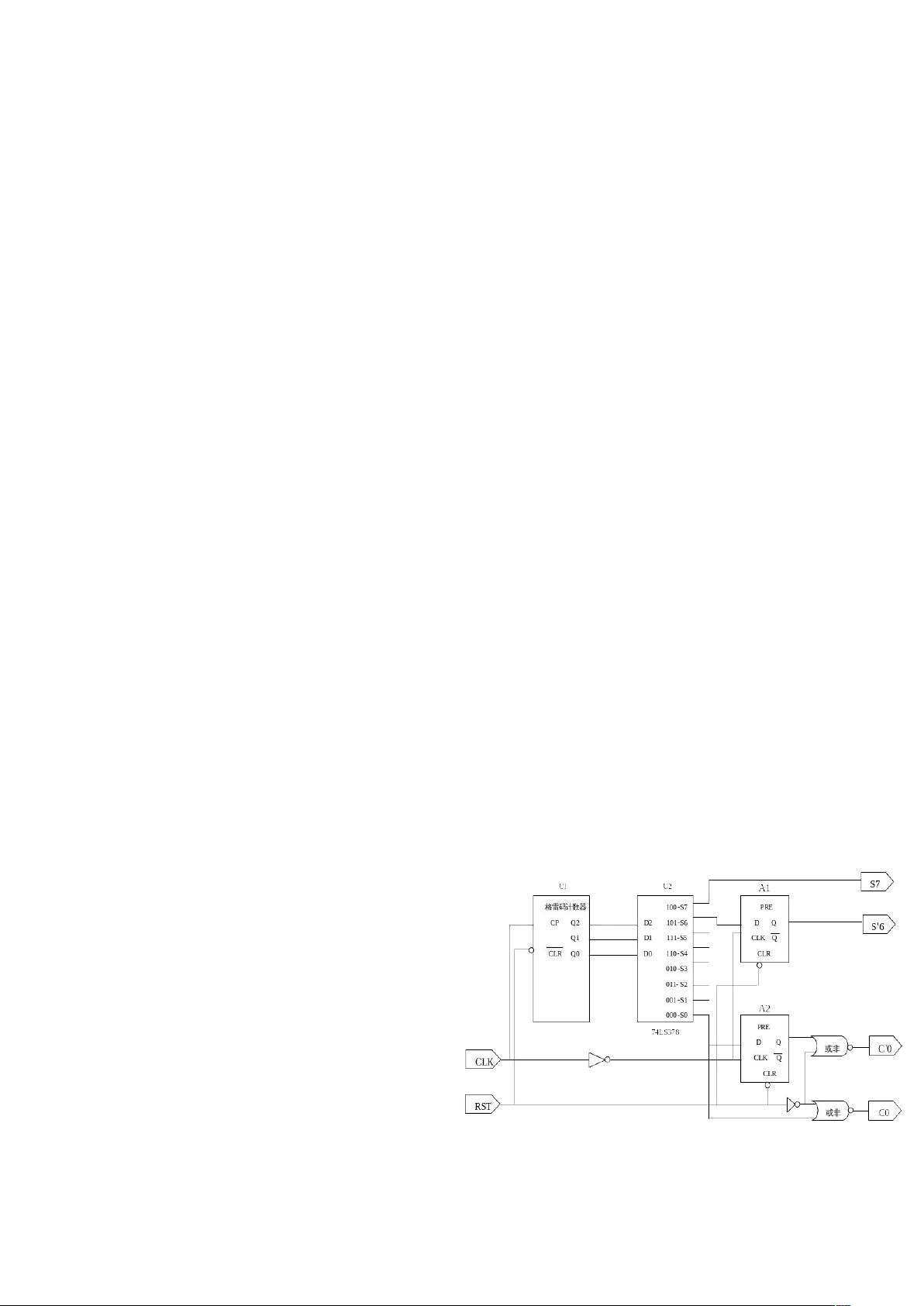

格雷码计数器是一种特殊类型的计数器,它的相邻计数值之间仅有一位不同,这大大减少了在计数转换中可能出现的毛刺。相较于传统的二进制计数器,格雷码计数器在切换状态时减少了错误的可能性,提高了系统的可靠性。在本文的设计中,格雷码计数器作为核心组件,与3-8译码器和D触发器共同构建了硬件电路。

3-8译码器的功能是将输入的三位二进制代码转换为八路不同的输出信号,这使得移位时序控制器能够驱动多个设备或信号线。D触发器则用于保持和传递稳定的数据,在时钟脉冲的上升沿,D触发器接收并锁定输入数据,确保在时序控制中的数据一致性。

软件设计部分,研究者采用了Verilog HDL(硬件描述语言)来描述控制器的行为和逻辑。Verilog HDL是一种强大的工具,允许设计者以接近于自然语言的方式来描述数字系统的功能。通过Altera Quartus II综合开发平台,设计被转化为可编程逻辑器件(如FPGA)的门级网表,并进行功能仿真。在该平台上进行的仿真结果显示,基于格雷码计数器的移位时序控制器有效地避免了传统二进制计数器可能出现的错误和毛刺,提供了更加稳定的输出。

关键词:移位时序控制器 - 格雷码计数器 - D触发器 - 毛刺现象

总结起来,本文的研究工作着重于提高移位时序控制器的性能和可靠性,采用格雷码计数器解决了传统方案中常见的问题,如数据错误和毛刺现象。通过硬件电路和Verilog HDL软件设计的结合,成功实现了这一目标,为高级在轨系统和其他需要高精度时序控制的应用提供了有价值的参考。

2018-03-24 上传

2010-10-16 上传

2020-08-05 上传

2021-09-15 上传

2012-09-15 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

ertao2008

- 粉丝: 0

- 资源: 1

最新资源

- AlanMvvm快速开发框架,基于MVVM模式组件化开发集成谷歌官方推荐的JetPack组件库:LiveData、V.zip

- 孢粉测定法:可靠地估计授粉昆虫的体型和同变性状

- 湖光秋月两相和—2020年5G 云VR研究报告.rar

- js-callgraph:为JavaScript和Typescript构造近似的静态调用图

- lock:锁库提供PHP代码的序列化执行

- homebridgeStatusWidget

- 读文件的几个字节加密再写回去.zip

- Excel模板大学普通高等学校专接本招生计划及参考教材.zip

- 煤炭开采Ⅱ行业-榆林煤矿复产进度较慢,产地供给偏紧支撑港口煤价.rar

- doing-cli:简化了针对天蓝色devops的开发工作流程

- 侧边栏:NavigationView 网络请求用的Retrofit 图片加载用的Fresco 数据库使用xutils.zip

- MoviesandSeries

- C-22-Fairy-and-Star-2

- apostrophe-address-widgets:ApostropheCMS地址小部件

- Excel模板大学校部机关处室学生勤工助学酬金公示.zip

- ListChecker