定点原码一位除法器设计:加减交替法实现

该资源是一份关于计算机组成原理课程设计的报告,主要涉及定点原码一位除法器的设计。报告详细介绍了设计原理、方案、功能模块的实现、仿真调试、编程下载以及硬件测试,旨在通过加减交替法实现四位二进制数的定点原码一位除法。

### 1. 定点原码与除法概念

定点原码是指在二进制数表示中,数值的最高位用于表示符号,正数为0,负数为1。在定点数运算中,数值的范围是固定的,通常用于简单的计算和数据处理。除法是算术运算之一,将一个数(被除数)分成若干部分,每部分的大小等于另一个数(除数)。

### 2. 加减交替法

定点原码一位除法的加减交替法是一种简化恢复余数法的算法。在恢复余数法中,每次计算后需要恢复余数到正数,而加减交替法则是在余数为负时,不再恢复,而是通过加上除数来替代减去除数的操作。这种方法减少了恢复余数的步骤,但可能需要在最后一步恢复余数以获取正确的结果。

### 3. 设计流程

- **设计原理**: 报告中指出设计采用了加减交替法,对四位二进制数进行除法运算。

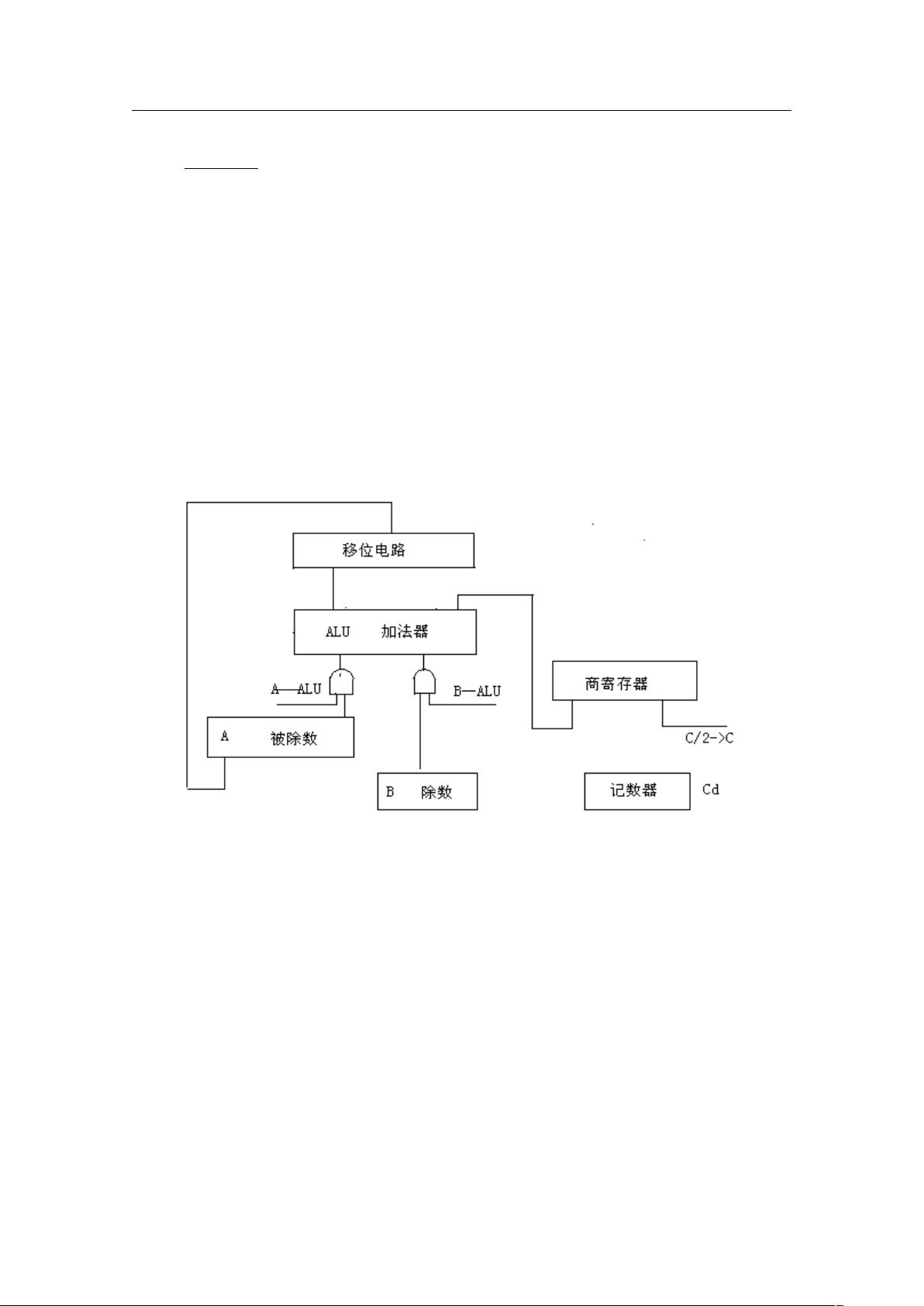

- **总体方案**: 设计包括除数与被除数寄存模块、加法/减法模块(根据余数的正负)、移位模块和控制模块。

- **详细设计**:

- **顶层方案**: 创建顶层图形设计文件,选择并锁定器件引脚。

- **功能模块**:

- **选择模块**: 负责选择正确的操作(加或减)。

- **移位模块**: 实现余数的左移操作。

- **控制器模块**: 控制整个除法过程,决定何时加减、何时左移和更新商。

- **除法选择器模块**: 决定是执行加法还是减法。

- **仿真调试**: 对设计进行仿真,检查其正确性。

### 4. 编程下载与硬件测试

- **编程下载**: 将设计的逻辑转换为可执行的代码,并下载到硬件平台上。

- **硬件测试**: 在实际硬件上运行设计,分析测试结果,确保除法器功能的正确性。

### 5. 示例

报告中给出了一个具体的除法规则示例,展示了从被除数开始,通过加减交替法进行除法运算的过程,直至得出最终的商和余数。

### 6. 结构组成

除法器由以下几个主要部分构成:

- **除数选择模块**: 根据算法需要选择适当的除数。

- **移位模块**: 用于左移余数,是除法运算的关键步骤。

- **加法/减法模块**: 执行加法或减法操作,取决于余数的符号。

- **控制模块**: 根据当前状态和运算规则,生成相应的控制信号。

### 7. 应用场景

这种定点原码一位除法器的设计对理解计算机内部的算术逻辑单元(ALU)运作机制至关重要,常用于CPU设计和数字逻辑课程的教学实践。通过这样的设计,学生能够深入理解二进制运算的底层原理,为后续的计算机系统设计打下基础。

这份报告详细阐述了定点原码一位除法器的设计和实现过程,通过加减交替法简化了除法操作,有助于读者深入理解计算机硬件中的数值处理。

2023-06-07 上传

2011-01-03 上传

2020-07-11 上传

2012-04-27 上传

baoduo123456

- 粉丝: 0

- 资源: 1

最新资源

- Timepiece:台式机闹钟-开源

- celaju:达托斯基地

- dbt-learn-myang

- HT-Microservices:人类谈微服务

- Paddle2.0-API:高层API助你快速上手深度学习

- Salat-App:使用React Native创建的Salat Time应用

- esp_effects:ESP32的老派演示效果

- filecon9

- Activity_selection_prblm.c

- 针对Web开发人员HTML-CSS和Javascript:Coursera测试3

- Zobrollo:2D简约顶视图赛车游戏

- touchcreator.github.io

- Android-Activity:Activity之间传输数据

- stage-2assignments

- sReminder - Event and Birthday Reminder-开源

- 数据可视化平台-大屏.rar