集成电路中的Latchup现象:原理与防治策略

"这篇文章主要探讨了集成电路中的Latch up现象,这是一种由于寄生PNP和NPN双极性晶体管交互作用导致的低阻抗通路,可能对芯片造成严重损害。文章通过分析Latch up的原理,揭示了其产生的原因,并提出了防止Latch up的方法,包括优化基体掺杂、避免源漏正向偏压、增设轻掺杂层以及使用Guardring技术等。"

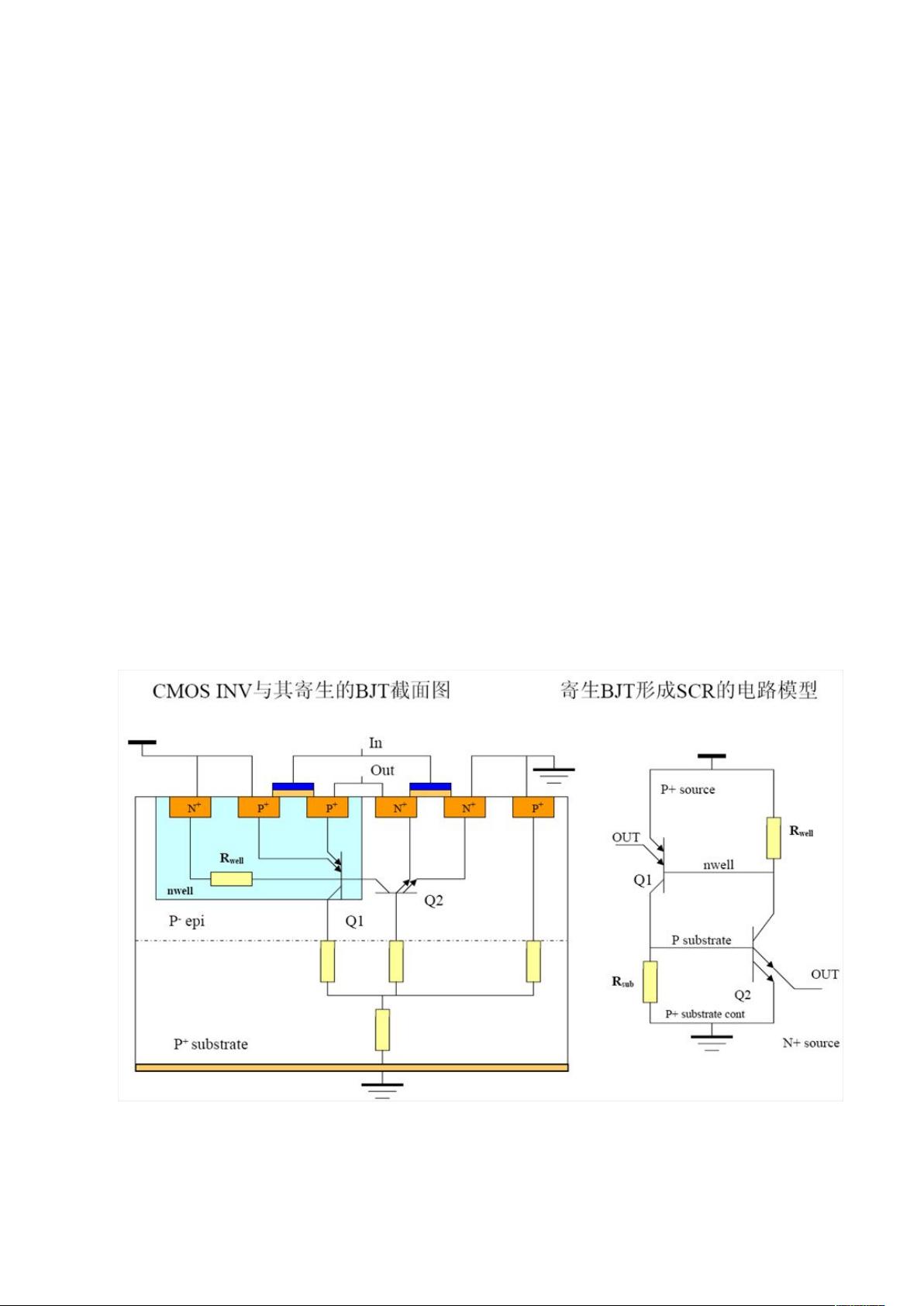

Latch up现象是集成电路设计中必须面对的重要问题,特别是在高集成度和封装密度的现代芯片中。它发生在CMOS芯片中,尤其是易受外部干扰的I/O电路,有时也会出现在内部电路。Latch up的根源在于芯片内部的寄生PNP和NPN晶体管结构,它们在特定条件下会形成类似可控硅(SCR)的电路,导致电源VDD与地线GND之间形成低阻抗通道,进而产生大量电流,这可能导致芯片的永久性损坏。

Latch up的触发通常由以下几个因素引起:电源电压VDD的快速变化、I/O信号超出正常范围、ESD静电放电事件、多个驱动器同时动作引起的电源和地线瞬态变化,以及well侧面漏电流过大。这些因素都可能导致足够的电流流过寄生的BJT,触发Latch up状态。

为了防止Latch up的发生,设计者采取了一系列措施。首先,可以通过调整基体(substrate)的掺杂浓度来降低晶体管的增益,减少触发的可能性。其次,确保source和drain不处于正向偏压状态,避免激发寄生晶体管的导通。再者,加入轻掺杂的layer,隔断侧面电流,防止电流从垂直BJT流到低阻基体上。最后,Guardring技术的应用也是关键,P+ ring环绕nmos并与GND连接,N+ ring环绕pmos并与VDD连接,这种结构有助于降低Rwell,增强保护,减少Latch up的风险。

理解Latch up的原理并采取有效的预防策略对于集成电路的设计和可靠性至关重要。随着技术的进步,设计师需要不断优化设计,以应对更高级别的集成带来的挑战,确保芯片能够在各种条件下稳定工作。

2020-10-16 上传

2020-12-09 上传

2019-09-10 上传

2019-10-18 上传

2013-10-15 上传

2009-08-05 上传

2021-09-19 上传

2023-07-27 上传

lglgliangg

- 粉丝: 2

- 资源: 5

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载