VHDL实现的数字频率计设计与仿真

版权申诉

175 浏览量

更新于2024-06-25

收藏 19.51MB DOC 举报

"基于VHDL的数字频率计设计与仿真是电子工程中的一项实践,利用硬件描述语言VHDL实现数字测量仪器的现代化设计。VHDL在电子设计自动化(EDA)中扮演核心角色,尤其在复杂数字系统设计中。数字频率计是一种基本的电子测量工具,用于测量信号频率、周期和占空比,广泛应用于科研和工业生产领域。随着CPLD的普及,VHDL使得设计更加简洁,提高了性能和可靠性。多功能数字频率计具有小巧、高效和低功耗的优势,适用于各种电子设备,如计算机、通信设备和家用电器。随着技术的发展,数字频率计正朝着智能化和高精度的方向迈进,在高科技领域如数字卫星和数字通讯中有着广泛应用。"

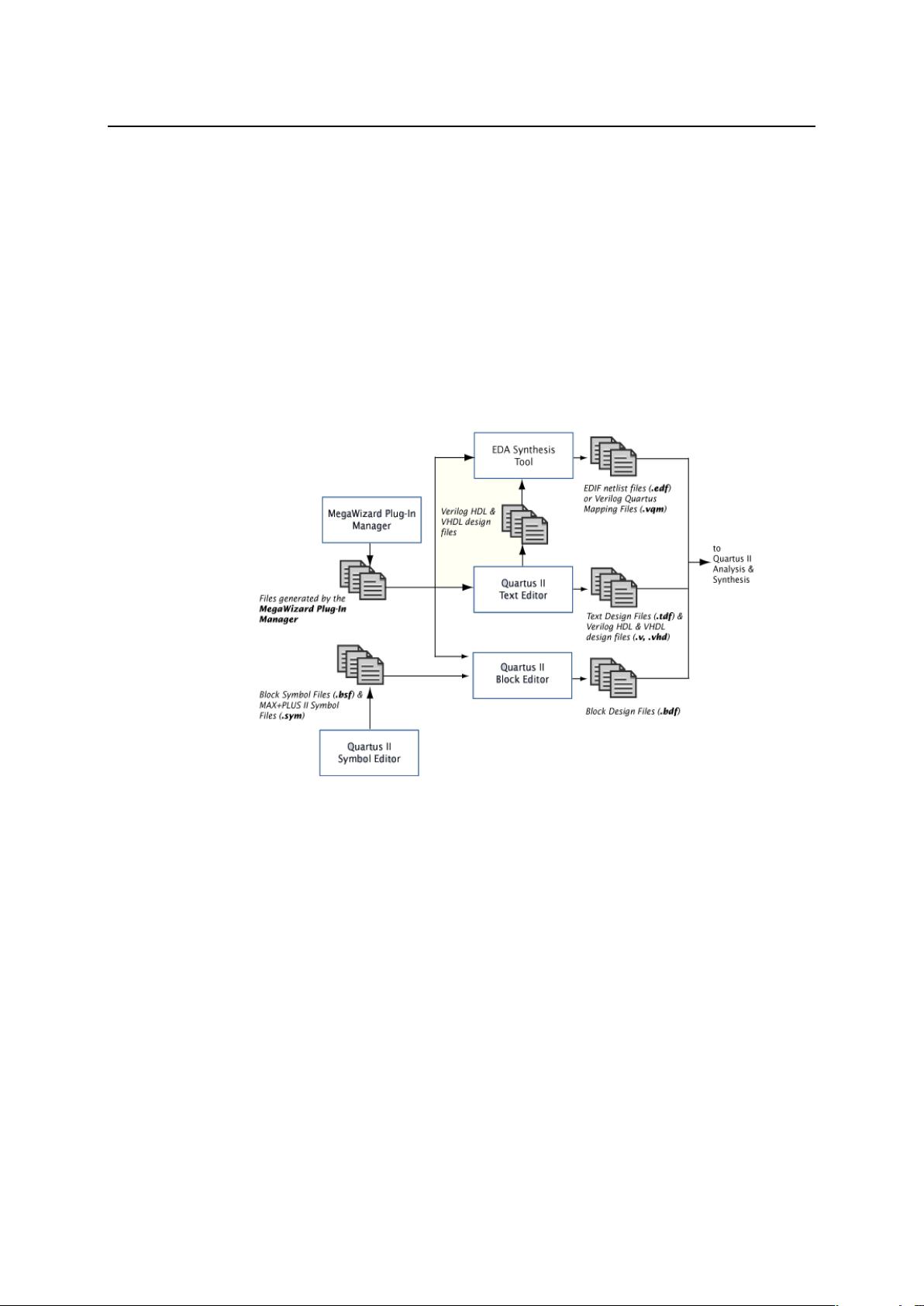

本文档详细介绍了基于VHDL的数字频率计设计。首先,设计背景部分阐述了VHDL作为硬件描述语言在现代电子设计中的重要地位,指出VHDL和Verilog HDL已成为国际标准,并在ASIC和FPGA设计中占据主导。数字频率计作为基础电子测量工具,其设计和实现方式也从传统的硬件电路转向了VHDL编程。

接着,文档讨论了数字频率计的特点和优势。多功能数字频率计利用CPLD和VHDL实现,降低了硬件复杂度,提升了系统性能。这种设计减少了延迟,提高了测量精度和系统可靠性。此外,VHDL编程允许现场更改,增加了设计的灵活性。

然后,文中强调了数字频率计在各个领域的广泛应用,包括计算机、通信、音频视频设备,以及家用电器等。集成数字频率计因其体积小、功耗低和高可靠性,成为经济高效的选择。随着技术的进步,数字频率计正向数字化和智能化发展,能够提供更精确的测量和更广泛的测量范围。

最后,文档可能继续探讨了数字频率计的具体设计过程,包括VHDL代码的编写、仿真验证以及实际硬件实现步骤。通过VHDL的逻辑设计,实现频率计的计数、转换和显示功能,并通过EDA工具进行综合和布局布线,最终在CPLD或FPGA上实现硬件原型。

这篇毕业设计文档全面涵盖了基于VHDL的数字频率计设计原理、实现方法及其在现代电子系统中的应用价值,为读者提供了深入理解VHDL在数字系统设计中的应用实例。

2008-11-08 上传

2023-12-19 上传

2023-05-24 上传

2023-06-02 上传

2023-06-09 上传

2023-05-03 上传

2023-12-19 上传

2023-05-11 上传

老帽爬新坡

- 粉丝: 92

- 资源: 2万+

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南