Xilinx Kintex7kc705 DDR3 MIG实战教程:Vivado入门指南

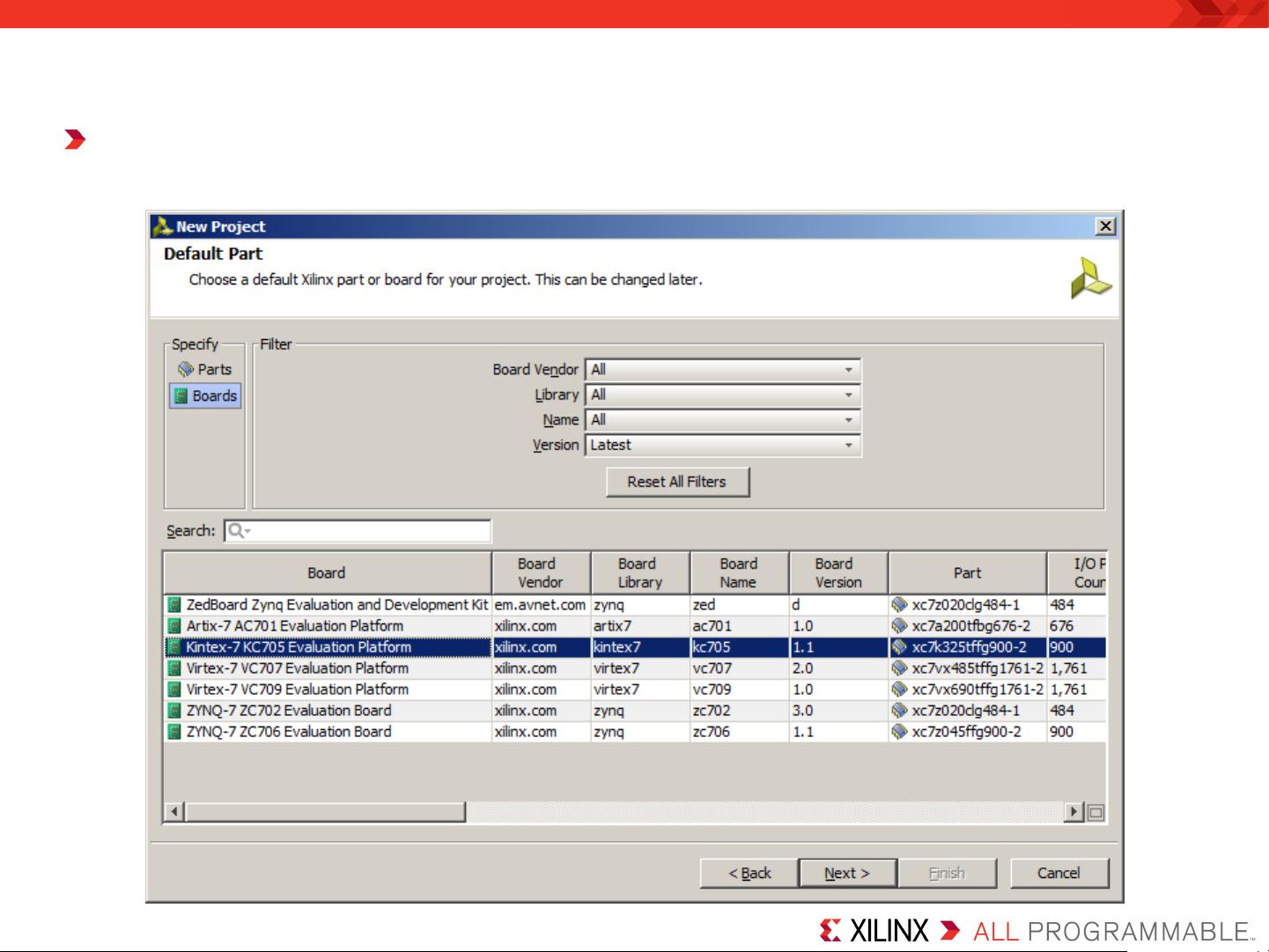

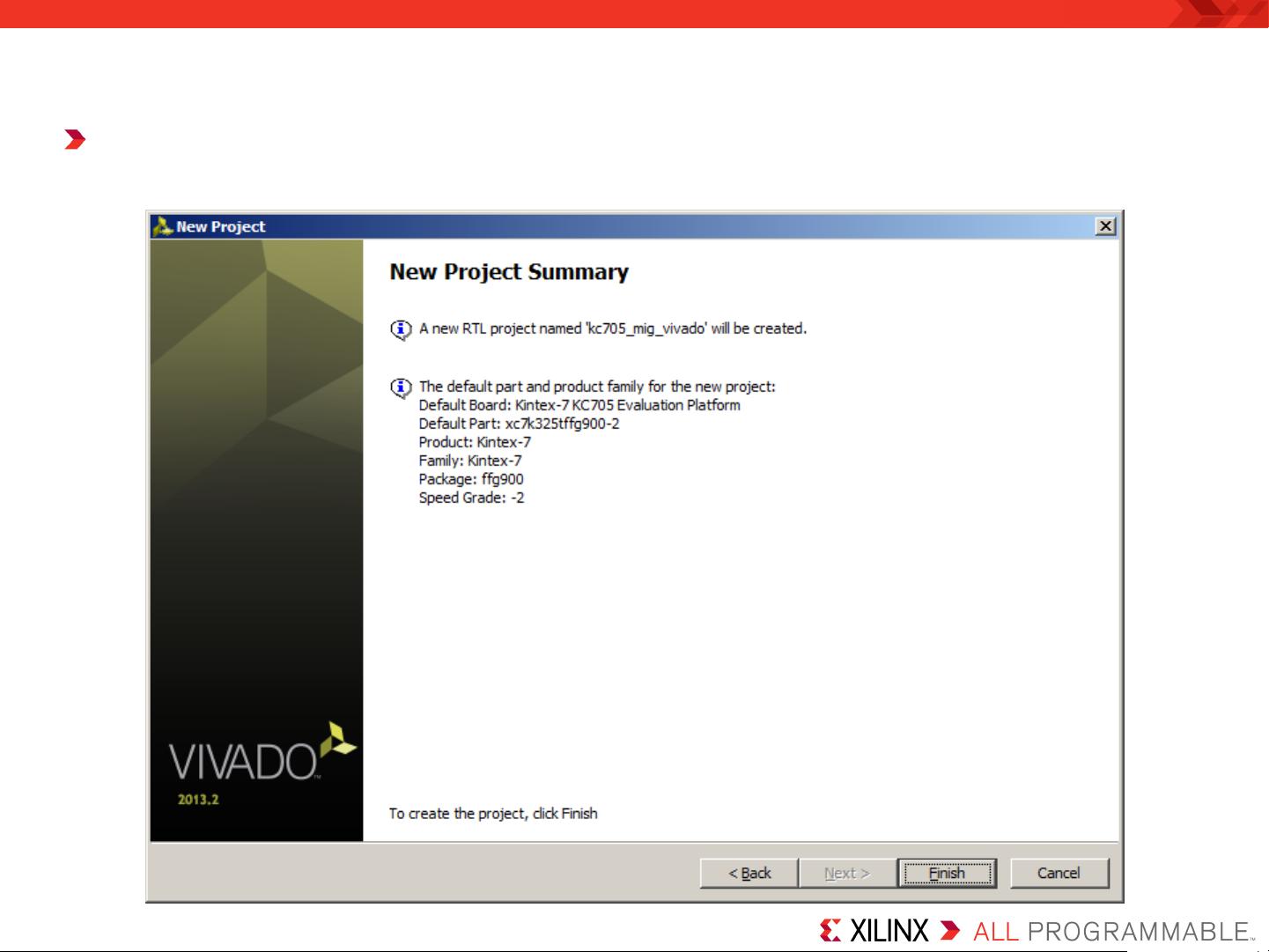

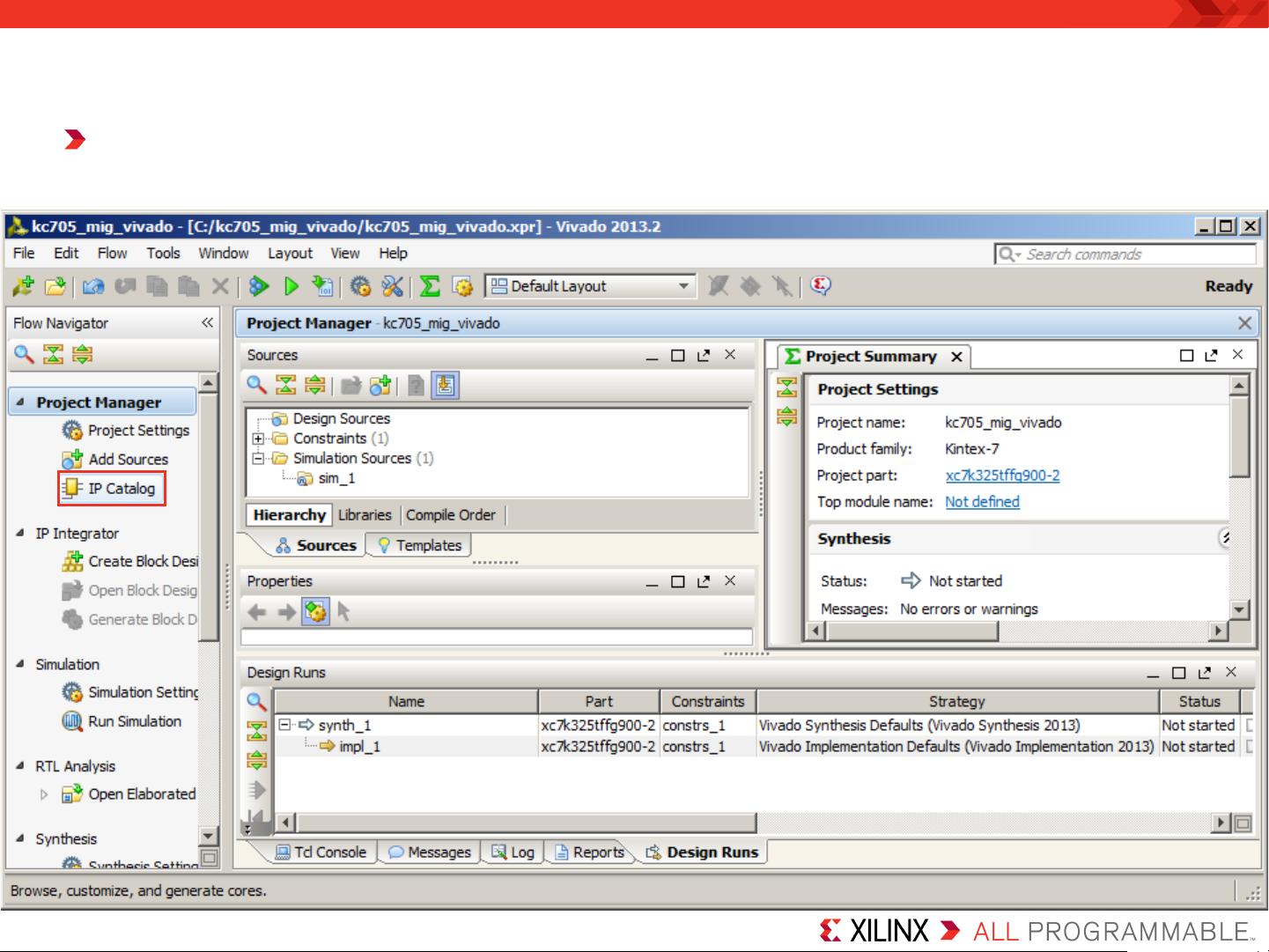

本资源是一份针对Xilinx Kintex7 kc705开发板的详细DDR3设计指南,主要利用了Xilinx的MIG(MicroBlaze Interconnect Generator)工具和Vivado设计环境。MIG是一种高度集成的硬件设计方法,它简化了在Xilinx FPGA中实现高性能内存接口的过程,特别适合于处理DDR3这类高速内存技术。

在"July2013"的版本中,这份教程旨在帮助新接触Xilinx平台的用户快速理解和上手使用KC705开发板进行DDR3设计。KC705是一个功能强大的FPGA开发平台,集成了多种外设接口,包括高速的DDR3支持,对于学习FPGA设计和嵌入式系统开发的学生和工程师来说,是一个理想的起点。

Vivado是Xilinx官方推荐的设计工具,它提供了一整套的IP核、设计流程和调试手段,使设计师能够更有效地进行硬件设计。在本教程中,开发者将学习如何配置MIG IP以创建符合DDR3规范的控制器,并将其集成到kc705的系统架构中,包括时序分析、信号完整性设置以及可能的配置设置。

值得注意的是,由于该资源属于版权作品,Xilinx保留所有权利并声明了免责声明。用户在使用信息时必须自行获取所需的许可,并承认信息可能存在的错误或更新,Xilinx不对技术支持或与之相关的协助承担任何责任。此外,虽然Xilinx提供的信息没有明示或暗示任何关于适销性或特定用途适用性的保证,但其提供了广泛的技术指导,涵盖了产品性能、兼容性和一般用途的描述。

这是一份实用的教程,对想要深入理解Xilinx Kintex7和DDR3内存设计的开发者而言,无论是从理论学习还是实践操作层面,都能从中受益匪浅。通过跟随这份指南,新手可以迅速掌握使用MIG工具以及Vivado进行高效、稳定的设计流程,从而提升自己的技能水平。

点击了解资源详情

815 浏览量

2018-08-15 上传

点击了解资源详情

点击了解资源详情

blueyk

- 粉丝: 0

- 资源: 1

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用