使用Cadence Allegro创建原理图设计工程

"这篇教程介绍了如何在Cadence Allegro中进行原理图设计,包括创建新工程、设置工程文件结构、管理库文件以及将共享库添加到个人工程库中的步骤。"

在Cadence Allegro中进行原理图设计是电子设计自动化(EDA)流程的关键步骤之一,它允许设计者以图形方式表示电路的连接和组件。以下是对教程内容的详细解释:

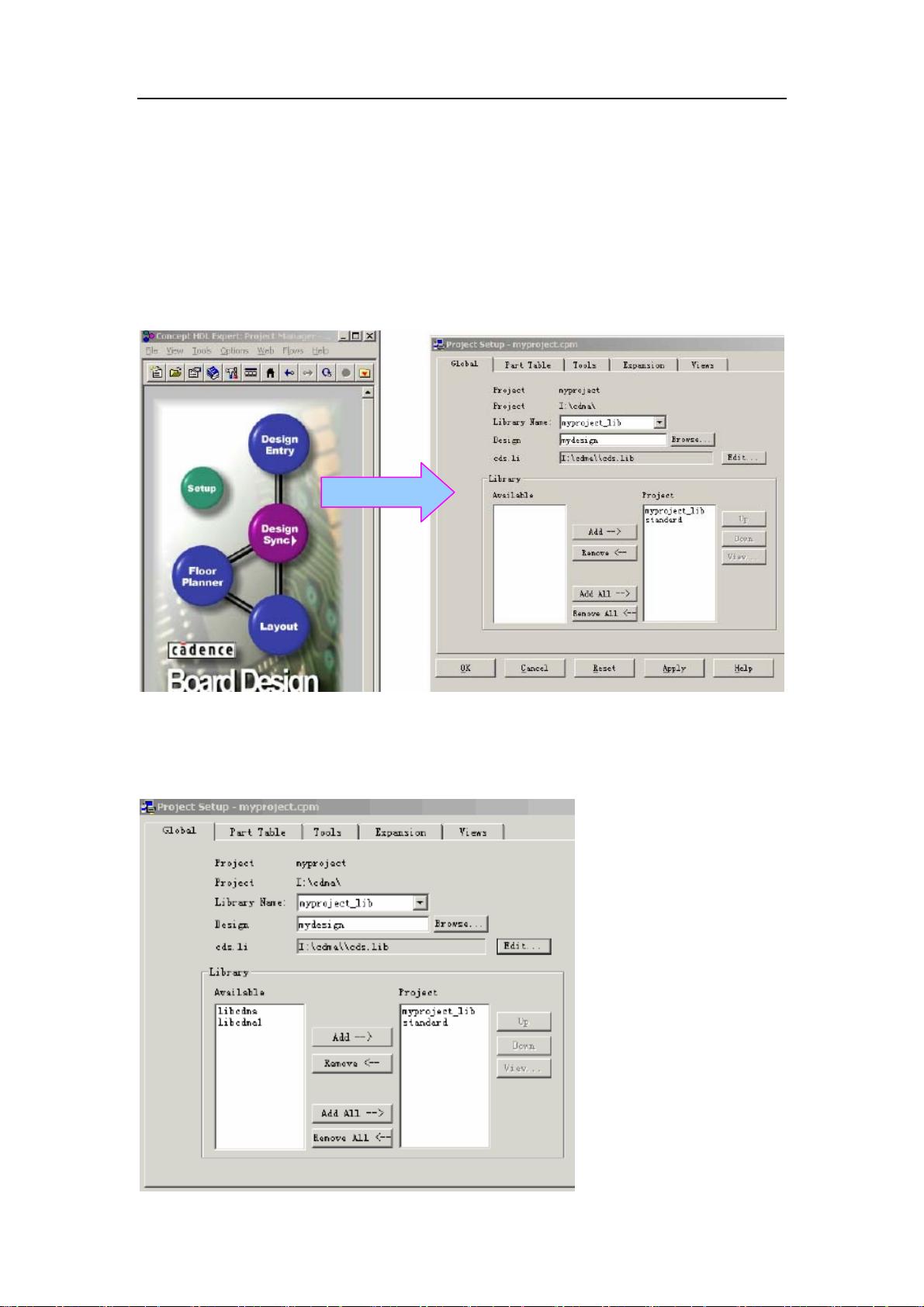

首先,创建一个新的工程是设计流程的起点。使用ProjectManager,设计者可以配置一个包含特定文件结构的项目目录。项目文件(`.cpm`)存储了设计的相关配置信息,如文件名、使用的库等。设计库(`designlibrary`)下则保存了原理图和其他相关设计数据。

在新建项目时,你需要提供项目名称,例如`myproject`,这将生成`myproject.cpm`和`myproject.lib`两个文件。接着,你可以选择需要的库,如`myproject_lib`,并将它们添加到`ProjectLibrary`中。设计目录的配置完成后,你可以开始使用这些库来创建你的设计。

共享原理图库对于团队协作至关重要,因为它们确保所有设计者使用的元件模型是一致的。例如,教程提到了`libcdma`和`libcdma1`,这两个库分别用于IS95项目前后。为了确保本地库与共享库同步,你需要在开始设计前更新本地库。在`cds.lib`文件中定义库路径,如`definelibcdmad:\libcdma`和`definelibcdma1d:\libcdma1`,然后通过`Setup`和`Add`功能将这些库添加到可用库列表中。

此外,教程可能还涵盖了其他高级主题,如元件放置、网络表生成、设计规则检查(DRC)和电气规则检查(ERC),这些都是确保设计无误的重要环节。元件放置涉及在原理图上布置各个组件,而网络表则是描述各组件之间连接关系的文件。DRC检查确保设计符合制造工艺限制,ERC则验证电路的电气完整性,防止短路或开路等问题。

Cadence Allegro的原理图设计涉及项目管理、库管理和设计验证等多个方面。掌握这些基本操作是成为熟练的Allegro用户的第一步,也是电子设计工程师必备的技能。通过持续学习和实践,设计者可以更加高效地利用Allegro进行复杂电路设计,从而提高整个电子产品开发的效率和质量。

3401 浏览量

157 浏览量

830 浏览量

954 浏览量

1005 浏览量

279 浏览量

564 浏览量

728 浏览量

lrsiner

- 粉丝: 0

- 资源: 3