FPGA实现的ASN.1解码模块设计与应用

"该文介绍了一种针对ASN.1基本编码规则(BER)设计的FPGA解码模块,主要用于解析GB61850-8-1和GB61850-9-2标准下的GOOSE和SV的MAC层帧。设计能够处理TAG不超过30、数据长度在1到2047之间、TLV层次不超过4级的数据流。文中详细阐述了BER编码的TLV结构,以及TAG和LENGTH的编码方式。"

asn.1基本编码规则(BER)是asn.1编码规范中的一个重要组成部分,常用于网络协议和数据交换的标准,如电力系统的GB61850标准。此规则定义了数据如何以Tag-Length-Value(TLV)的形式进行编码和解码。在FPGA实现的解码模块中,理解这些规则至关重要。

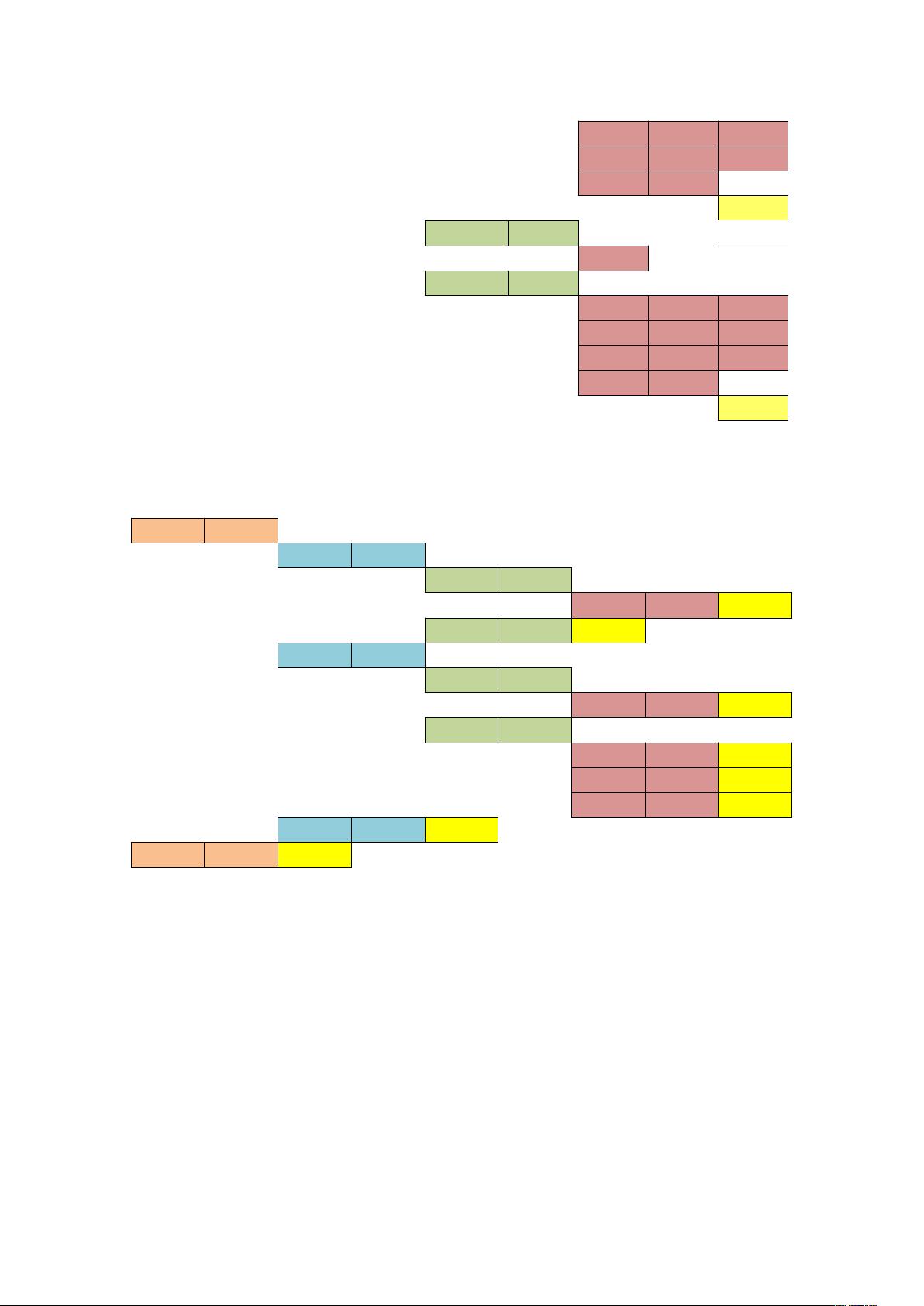

TAG在BER编码中起着标识数据类型的作用。对于TAG编码,小于30的值可以直接在一个八位组中表示。若TAG值大于30,需要使用扩展编码,第一个八位组的后五位全为1,后续八位组最高位为1表示继续,为0表示TAG结束。在GB61850标准下,实际使用的TAG值均小于30,因此只需一个字节即可表示。

LENGTH域用于指示VALUE字段的长度,有定长和不定长两种形式。定长情况下,如果长度小于或等于127,直接在一个八位组中编码;超过127时,第一个八位组的低七位表示LENGTH域本身的长度,后面跟的八位组组合起来表示VALUE的长度。不定长情况下,LENGTH的编码为0x80,然后根据具体情况编码VALUE的长度。

在设计的解码模块中,需要处理的数据长度范围是1到2047,且最多支持四层的TLV结构。这意味着模块必须能处理复杂的数据结构,并确保正确解码不同层级的TAG和LENGTH。对于超过这些限制的数据,可能需要对设计进行扩展或优化。

FPGA实现的解码模块的优势在于并行处理能力和实时性,这使得它能快速解析和处理大量的数据流,满足实时通信系统的需求。在电力自动化系统中,如GB61850标准规定的GOOSE(Generic Object Oriented Substation Event)和SV(Sampled Values)通信,这样的高速解码能力是必不可少的。

为了实现这样的解码模块,开发者需要深入理解asn.1编码规则,熟悉FPGA设计流程,并掌握Verilog或VHDL等硬件描述语言。设计过程中,需考虑到模块的灵活性和可扩展性,以适应不同应用场景和未来可能增长的数据量需求。同时,还需要进行充分的测试和验证,确保解码模块在各种条件下都能正确、高效地工作。

2011-03-08 上传

2020-12-02 上传

点击了解资源详情

点击了解资源详情

2010-09-16 上传

2008-07-10 上传

2012-03-14 上传

2021-08-29 上传

准瘦子

- 粉丝: 20

- 资源: 8

最新资源

- sebii : mighty failing ranger en live-crx插件

- appman-api-spec:RESTful API for Appman的规范

- nypority,源码转补码的c语言程序,c语言

- PaintCodeStar:个人资源

- AnaLight

- chromedriver-win32-V124.0.6367.91 稳定版

- 数据结构

- Driving-School-Test-System:该系统解决了潜水学校测试学生学习成绩的问题。 该系统可以方便地为老师生成试卷,学生可以在Internet上答复试卷

- linkedin mieux-crx插件

- 2000-2020年白城市500米植被净初生产力NPP数据

- credit

- kettle 的war包下载,webspoon9.0,kettle基于web的数据清洗工具

- 矩芯 sdk 矩芯 sdk 矩芯 sdk 矩芯 sdk

- 46005671,会员管理系统c语言源码,c语言

- 登山雪山风格网站模板

- resume:我的简历