NVMe协议详解:PCI头与功能配置

需积分: 9 130 浏览量

更新于2024-07-09

收藏 19.37MB PDF 举报

本文档是关于NVM-Express (NVMe) 1.2.1版本的协议介绍,其中详细阐述了如何构建PCI头、PCI功能以及PCIe扩展功能,适用于对NVMe协议感兴趣的读者。

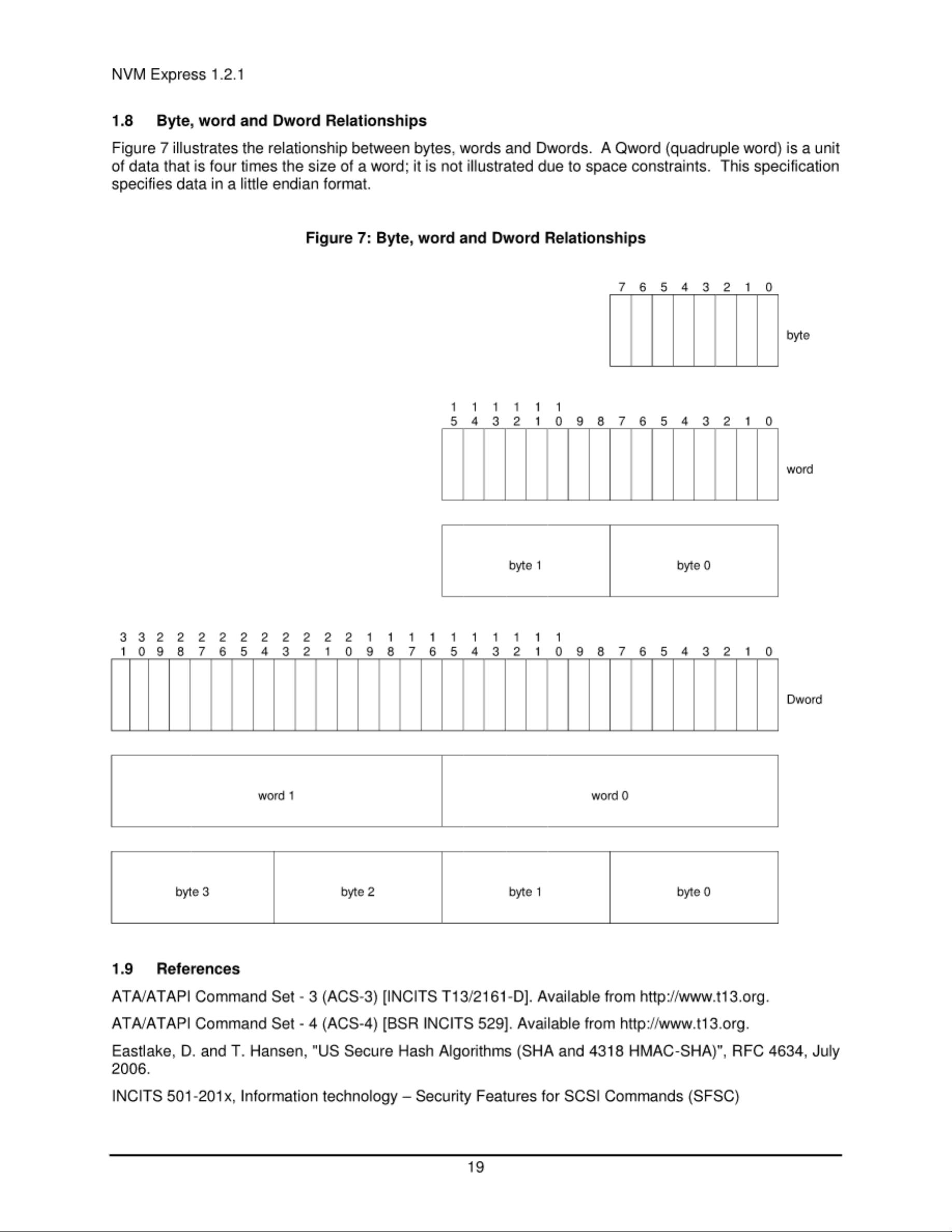

NVMe(Non-Volatile Memory Express)是一种高速接口标准,用于固态硬盘(SSD)等非易失性存储设备,它优化了PCI Express (PCIe)总线的性能,减少了I/O延迟并提高了系统吞吐量。在NVMe规范中,详细规定了控制器和驱动器之间的交互方式。

在描述中提到的PCI头、PCI功能和PCIe扩展功能是NVMe设备在PCI配置空间中的关键部分。例如,0x40、0x50、0xB0和0x70等地址是特定的寄存器,它们在NVMe设备的功能和行为中起到重要作用。

- 0x40寄存器(ID=0x01)通常与设备的配置和状态有关,某些读操作可能会改变其值,这在NVMe协议中是不可预读取的。

- 0x50寄存器(ID=0x05)涉及控制器的电源管理状态,当控制器从D3状态转移到D0时,如果该位为1,控制器不会执行内部重置。

- 0xB0寄存器可能与设备的中断机制和MSI(Message Signaled Interrupts)有关,系统软件会编程这个16位字段,如果启用MSI,其内容会在MSI内存写入事务的数据阶段驱动到低字节。

- 0x70寄存器(ID=0x10)与IO队列的大小限制相关,防止发出超过规定大小的读请求,以避免不定义的行为。

NVMe协议还强调了主机和控制器之间的兼容性和一致性,例如,不允许对两个或更多寄存器的部分进行访问,这可能是为了保持数据完整性和操作的原子性。控制器支持的IO命令集和仲裁机制通过特定的位来表示,如“独立的”和“通过PCIE实现的nvme协议”。

IO队列的创建和管理是NVMe的核心部分。在初始化之前,必须正确设置IO完成队列和IO提交队列的大小,否则可能导致控制器中止操作或返回错误状态。每个IO队列条目的大小和仲裁机制的选择(如轮训调度)会影响系统的性能和响应时间。

在寄存器中,有一个紧急优先级类的加权循环(WRR with Emergency Priority Class),它允许主机软件根据需求设置优先级。此外,控制字段决定控制器是否处理命令,清除该字段会导致控制器重置,移除所有IO队列,并将硬件恢复到空闲状态,但不影响PCI寄存器和管理队列寄存器。

NVMe协议1.2.1版本详细规定了NVMe设备在PCIe环境下的工作方式,包括寄存器配置、队列管理、电源管理、仲裁机制等多个方面,为高性能存储系统的设计提供了基础。

2022-07-15 上传

2014-10-06 上传

2017-12-04 上传

2019-06-18 上传

2020-06-24 上传

2021-07-07 上传

danpianji89s52

- 粉丝: 39

- 资源: 6

最新资源

- Voice-User-Interface:LaunchTech支持助理

- school-ms-netcorewebapi:学校管理系统-使用.NET Core构建的Web API

- OLgallery-开源

- 用于在Python中构建功能强大的交互式命令行应用程序的库-Python开发

- ThreatQ Extension-crx插件

- GeoDataViz-Toolkit:GeoDataViz工具包是一组资源,可通过设计引人注目的视觉效果来帮助您有效地传达数据。在此存储库中,我们正在共享资源,资产和其他有用的链接

- SQL-IMDb:关于IMDb数据集的各种约束SQL查询

- AlgaFoodAPI:藻类食品原料药

- wikiBB-开源

- 参考资料-基于SMS的单片机无线监控系统的设计.zip

- emptyproject-pwa:空项目:PWA + jComponent + Total.js

- React计算

- ux_ui_hw_17

- tamarux-开源

- pytest框架使编写小型测试变得容易,但可以扩展以支持复杂的功能测试-Python开发

- StellarTick-crx插件