6 Chapter 1

1.4.1 DSP Architecture

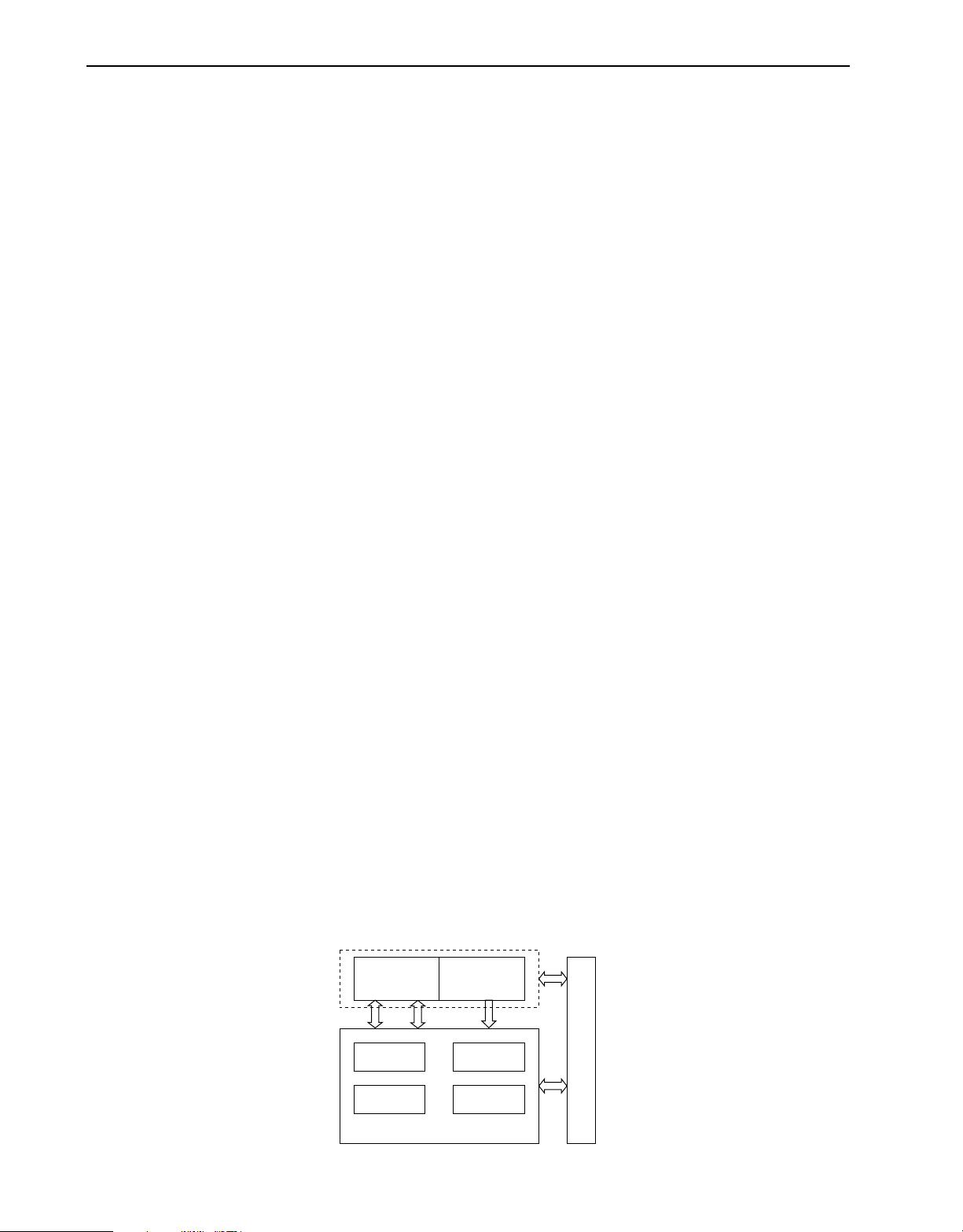

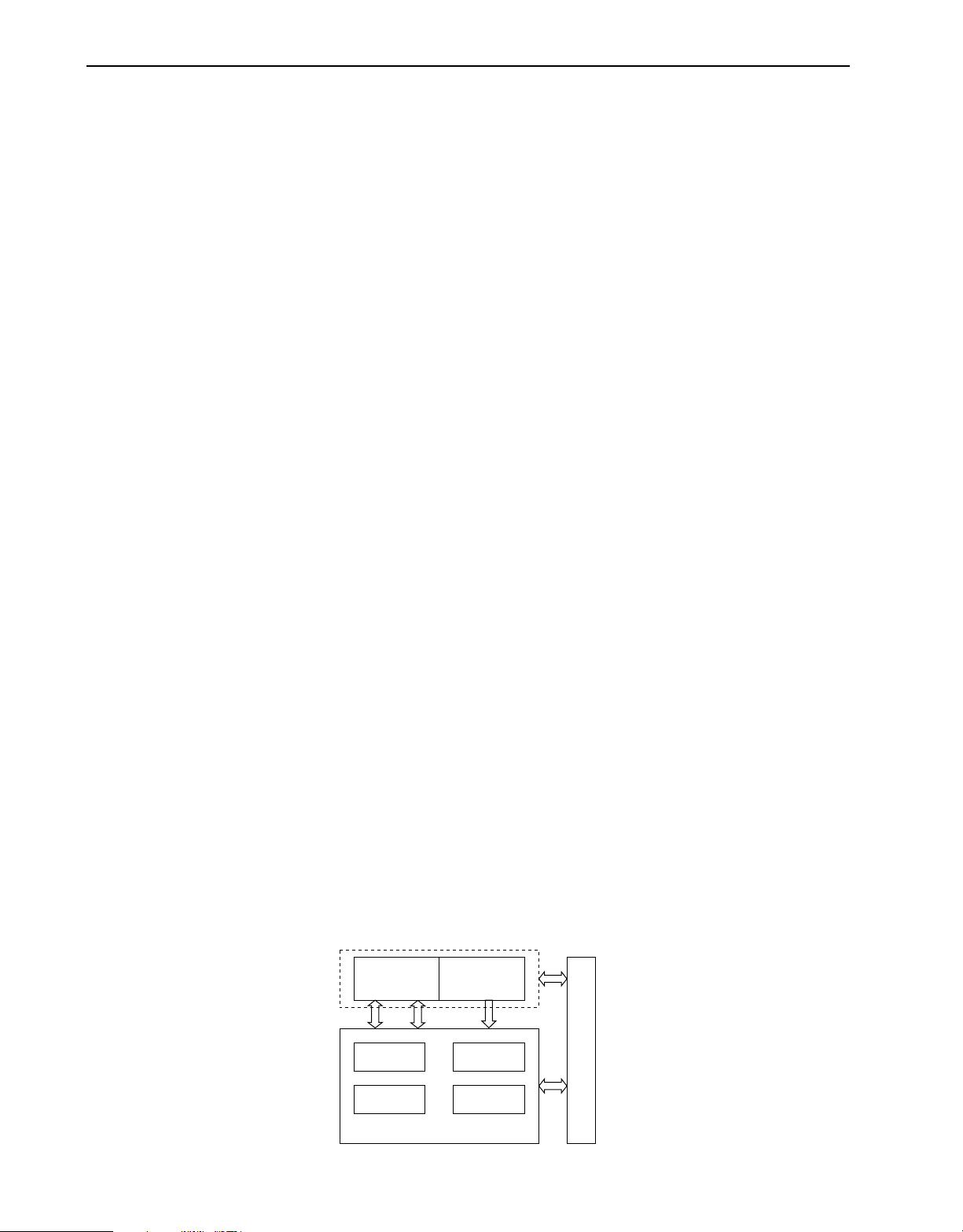

A simplified block diagram of embedded DSP architecture is shown in Figure 1.1. The m ain architectural

blocks of an embedded processor are the processor core (with register sets, ALU, data address generator [DAG],

sequencer, etc.), memory (for holding instructions and data, for stack space, etc.), peripherals (e.g., serial periph-

eral interface [SPI], parallel peripheral interface [PPI], serial ports [SPORT], general-purpose timers, universal

asynchronous receiver transmitter [UART], watchdog timer, and general-purpose I/O) and a few others (e.g.,

JTAG emulator, event controller, direct memory access [DMA] controller). Embedded processor peripherals and

memory architectures are discussed in some detail in Chapter 16.

The peripheral features are important when we talk about the overall application. In this book, we assume

that the architecture comes with all necessary peripherals to enable a particular application. Also, we assume

that the program code and data required for algorithm processing are residing in the faster memory (or le vel 1,

L1) memory, which can be accessed at the speed of the processor core. If we cannot fit data and program in L1

memory, then we store the extra data or program in L2/L3 memory and use DMA to get the data or program

from L2/L3 memory without interrupting the processor core. From an algorithm-implementation point of view,

the important things are processor core architecture, availability of L1 memory, and internal bus bandwidth.

Even more important than getting data into (or sending it out from) the processor, is the structure of the

memory subsystem that handles the data during processing. It is essential that the processor core access data in

memory at rates fast enough to meet application demands. L1 memory is often split between instruction and data

segments for efficient utilization of memory bus bandwidth. Most DSP architectures support this Harvard-like

architecture (in which data and instruction memories are accessed simultaneously, as shown in Figure 1.1) in

combination with a hierarchical memory structure that views memory as a single, unified gigabyte address space

using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers,

occupy separate sections of this common address space.

The register file contains dif ferent register types (e.g., data registers, accumulators, address registers) to hold

the information temporarily for ALU processing or for memory load/store purposes. The processor’s compu-

tational units perform numeric processing for DSP algorithms and general control algorithms. Data moving in

and out of the computational units go through the data register file. The processor’s assembly language provides

access to the data register file. The syntax lets programs move data to and from these registers and specify a

computation’s data format at the same time.

The DAGs generate addresses for data moving to and from memory. By generating addresses, the DAGs let

programs refer to addresses indirectly using a DAG re gister instead of an absolute address.

The program sequencer controls the instruction execution flow, including instruction alignment and decoding.

The program sequencer determines the next instruction address by examining both the current instruction being

executed and the current state of the processor. Generally, the processor executes instructions from m emory in

sequential order by incrementing the look-ahead address. However, when encountering one of the following

structures, the processor will execute an instruction that is not at the next sequential address: jumps, conditional

branches, function calls, interrupts, loops, and so on.

ALU Unit

Registers DAG Unit

Sequencer

Peripherals

Data

Memory

Instruction

Memory

DSP Core

Figure 1.1: Simplified diagram of DSP architecture.