西南交通数电:十进制可逆计数器设计与实现

版权申诉

实验三:西南交通大学电子工程课程中的十进制可逆计数器设计与实现

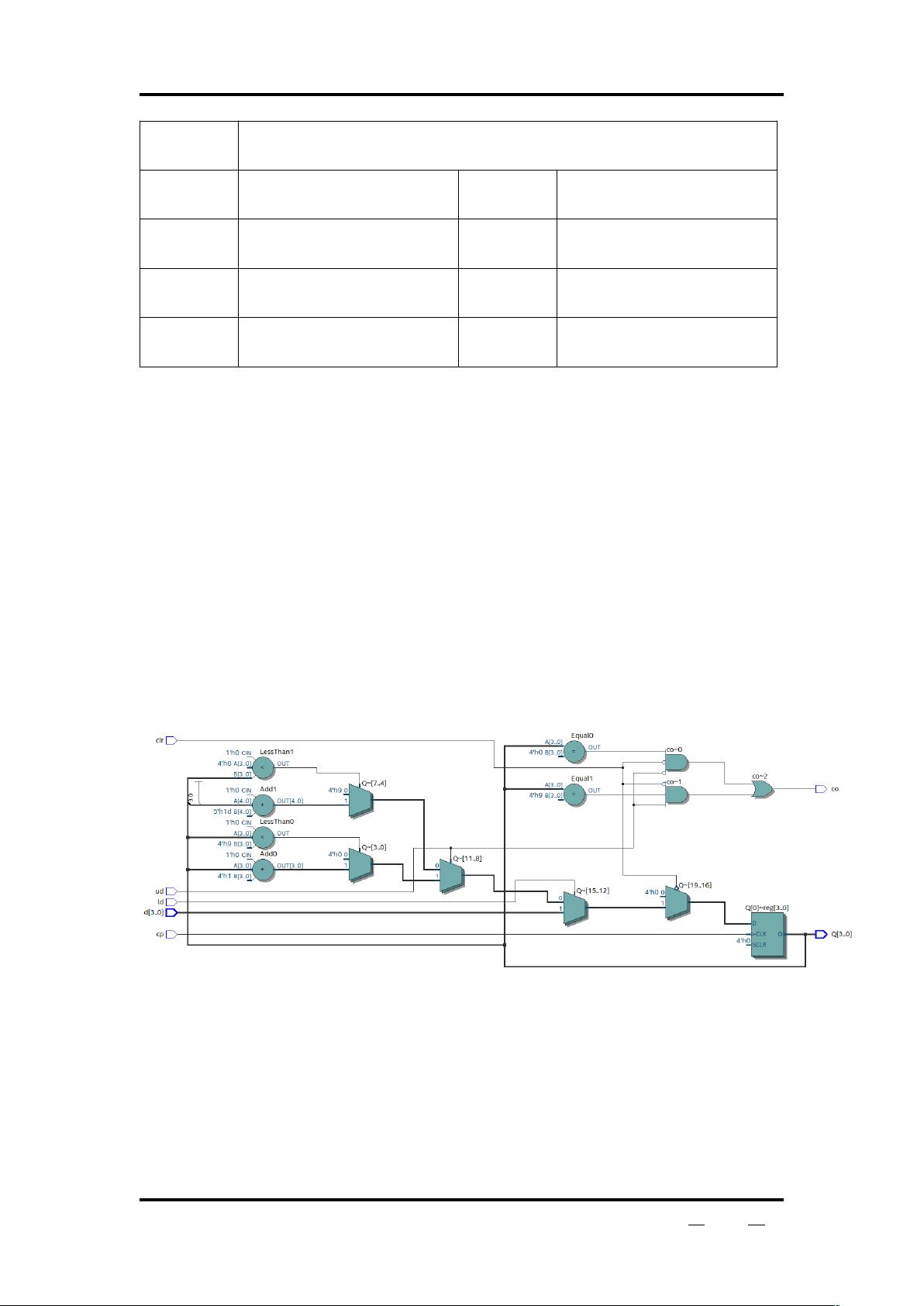

在这个实验中,学生被要求构建一个可逆的十进制计数器,用于执行加法和减法操作,并能处理进位和借位逻辑。首先,预习思考题引导学生对计数器的工作原理和基本概念进行复习。实验的核心是通过Verilog语言编写了一个名为`zzc_2292_3`的模块,它接收四个输入信号:`cp`(时钟信号)、`clr`(清零功能)、`ud`(加减选择)和`ld`(装载信号),以及一个4位的输入数据`d`,并输出4位的`Q`结果和一个表示进位或借位的标志`co`。

模块内部的`always @(posedge cp)`语句描述了计数过程。在非清零状态下,如果装载信号有效,就将输入数据载入计数器;否则,根据加减选择信号决定是递增还是递减计数。当计数器达到最大值(9)或最小值(0)时,会自动清零或置满。`co`信号的计算则基于`clr`、`ud`和`Q`的当前状态。

实验还包括了电路图、状态图和流程图的设计,这些图表有助于理解计数器的工作流程。程序代码中提供了详细的注释,便于初学者理解和学习Verilog编程。仿真部分展示了计数器在不同输入条件下的行为,包括时序波形图,显示了计数器在时钟信号作用下各个信号的变化情况。

接着,实验要求学生制作引脚分配表,将电路中的信号与实际硬件连接对应起来,以便于在实际硬件平台上进行实验。实验现象的记录和数据整理分析是验证设计正确性的重要步骤,学生需要记录实验过程中观察到的计数器行为,并对其进行数据分析。

此外,实验报告中还包括了学生的个人信息(姓名、班级、学号、实验时间等),预习成绩以及验收记录,记录了一次验、二次验或补验的过程,以及指导老师的评价。最后,学生应该反思他们在实验中遇到的问题,总结经验教训,分享个人的心得体会,这有助于提升他们的实践能力和问题解决能力。

这个十进制可逆计数器实验不仅涵盖了数字逻辑设计的基础知识,如计数器结构、Verilog编程和模拟验证,还锻炼了学生的实验操作技能和理论与实践相结合的能力。

相关推荐

六不过不改

- 粉丝: 22

最新资源

- 微信小程序开发教程源码解析

- Step7 v5.4仿真软件:s7-300最新版本特性和下载

- OC与HTML页面间交互实现案例解析

- 泛微OA官方WSDL开发文档及调用实例解析

- 实现C#控制佳能相机USB拍照及存储解决方案

- codecourse.com视频下载器使用说明

- Axis2-1.6.2框架使用指南及下载资源

- CISCO路由器数据可视化监控:SNMP消息的应用与解析

- 白河子成绩查询系统2.0升级版发布

- Flutter克隆Linktree:打造Web应用实例教程

- STM32F103基础之MS5单片机系统应用详解

- 跨平台分布式Minecraft服务端:dotnet-MineCase开发解析

- FileZilla FTP服务器搭建与使用指南

- VB洗浴中心管理系统SQL版功能介绍与源码分析

- Java环境下的meu-grupo-social-api虚拟机配置

- 绿色免安装虚拟IE6浏览器兼容Win7/Win8