FPGA实现的约束Viterbi译码器:优化路径存储与ACS设计

126 浏览量

更新于2024-08-30

收藏 419KB PDF 举报

本文主要探讨了从FPGA实现角度对大约束度Viterbi译码器中关键组件——路径存储单元的设计优化。Viterbi译码器,作为一种广泛应用在卫星通信和移动通信系统的最大似然译码算法,其复杂性随着约束长度k的增长呈指数级提升。大约束度导致硬件复杂度大幅增加,尤其是加比选(Add Compareselect,ACS)运算,其递归特性使得在FPGA中实现高效的流水线结构面临挑战。

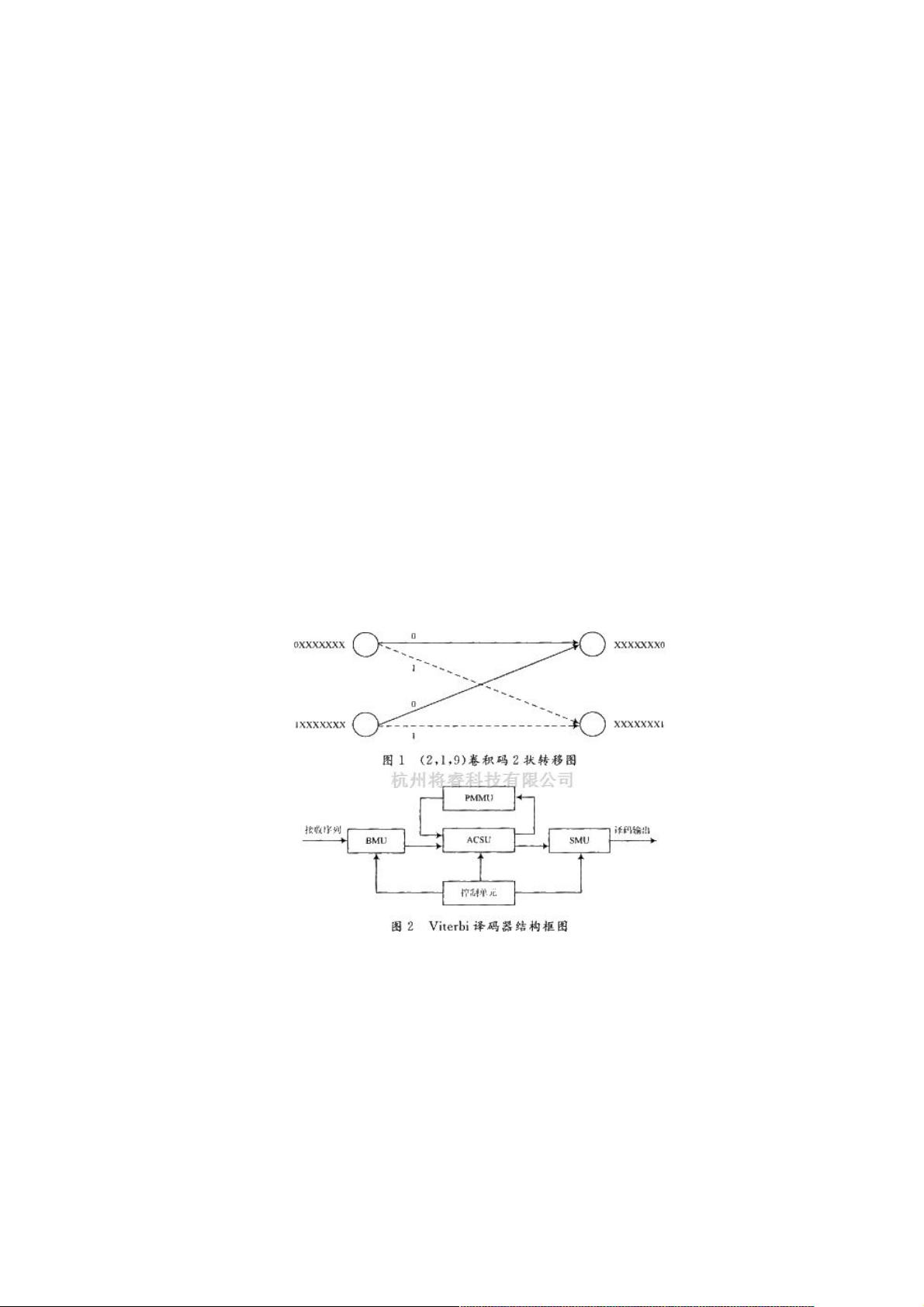

文章以(2,1,9)卷积码为例,FPGA实现中的核心目标是解决约束度带来的性能和面积的权衡。作者针对ACS运算采用了串并结合的设计策略,通过这种混合方法,可以在保持一定的计算能力的同时,兼顾硬件资源的占用,减少面积开销,提高译码效率。此外,文中还提及了路径度量存储的设计,采用同址存储方法,这样在有限的硬件资源下,仍能维持较高的译码速度。

Viterbi译码的基本流程包括分支度量单元(BMU)的计算,即计算每个可能路径与接收码的分支度量值,这是决定路径概率的关键因素。在这个过程中,作者详细介绍了状态转移图的构建和维特比搜索算法的操作,强调了在有限的FPGA资源内如何通过合理的架构设计来优化译码性能。

本文深入剖析了大约束度Viterbi译码器在FPGA上的实现策略,特别是针对路径存储单元的优化,以及如何通过改进ACS运算和利用流水线结构来克服约束度带来的性能瓶颈。这对于理解和设计高效、低功耗的无线通信系统具有重要意义,对于从事FPGA设计和通信系统工程的专业人士来说,提供了有价值的技术参考。

116 浏览量

152 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

668 浏览量

155 浏览量

2020-08-05 上传

weixin_38709139

- 粉丝: 7

- 资源: 935