Virtex-5 DDR2接口设计应用详解

需积分: 9 200 浏览量

更新于2024-07-22

收藏 1.04MB PDF 举报

DDR开发资料是一份针对DDR2 SDRAM应用的详细介绍文档,特别关注了V5和V4芯片上的操作流程,适合对高速内存接口设计感兴趣的工程师参考。该文档出自Xilinx公司,XAPP858(v2.2)发布于2010年9月14日,主要介绍了一个基于Virtex-5 FPGA的667 Mb/s DDR2 SDRAM接口实现。通过Xilinx的Memory Interface Generator (MIG)工具,用户可以定制化生成符合这种接口标准的设计。

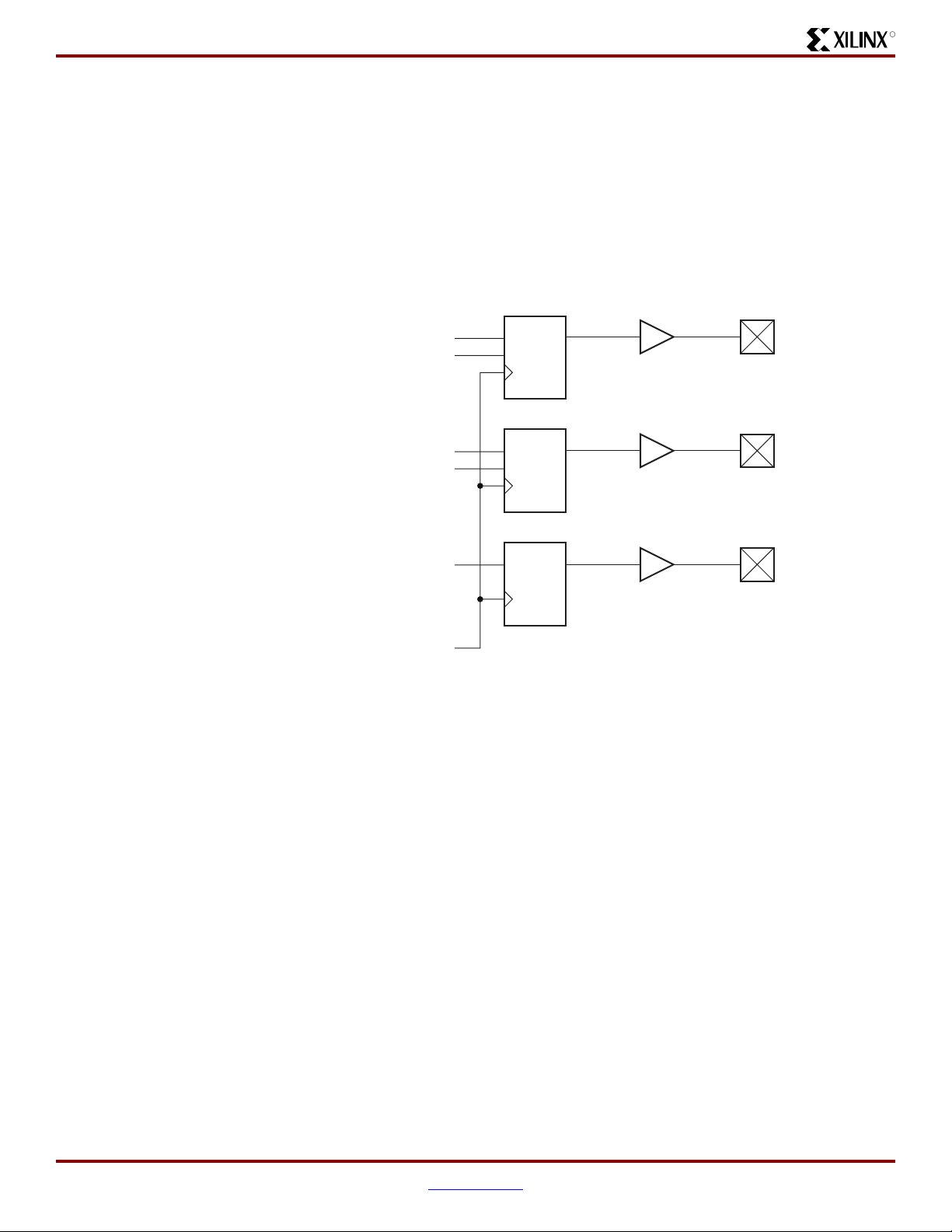

DDR2 SDRAM采用了同步传输方式,数据和 strobe信号在传输时边缘对齐,以便于接收。在Virtex-5 FPGA中,为了捕获到这些数据,需要对strobe或data信号进行适当的延迟。在这个设计中,读取的数据被存储在延迟后的strobe域中,然后通过输入双数据速率(IDDR) Flip-Flops以及可配置逻辑块(CLB) Flip-Flops转换成FPGA时钟域内的信号。

DDR2 SDRAM设备是DDR SDRAM系列的下一代产品,它们采用了SSTL1.8V I/O标准,提供了更高的数据传输速度和更先进的技术特性。相比于前一代,DDR2在带宽、频率和能效上都有显著提升,支持单次预取和更深的刷新模式,以支持更复杂的应用场景。

文档详细介绍了DDR2 SDRAM的工作原理、接口规范,以及如何在Virtex-5器件中实现高效的内存访问。此外,它还强调了使用MIG工具的优势,该工具能够简化设计过程,减少手动配置,从而节省时间和资源。对于从事FPGA设计特别是高速内存接口设计的工程师来说,这份文档是一个宝贵的参考资料,有助于理解和实现高性能的DDR2 SDRAM接口设计。

118 浏览量

205 浏览量

2025-01-03 上传

2024-10-30 上传

2024-10-30 上传

138 浏览量

fwf_mw

- 粉丝: 0

- 资源: 1

最新资源

- MDIO:操作员决策模型-卡塞拉(Cadeira do1ºSemestre do3º)诺米诺大学(Mino da MiEI da Minho)

- react-tictactoe:经典游戏的全栈JavaScript实现

- recipe-app

- 中国风客厅家装模型设计

- 使用红外传感器进行眼动跟踪-项目开发

- Unity Highlight Plus,模型轮廓高亮

- blockchain:测试区块链解决方案的游乐场

- 公司薪酬制度下载

- cse6040fa20:CSE 6040 校园 MSA 版本的课堂演示笔记本,2020 年秋季

- (修改)04-06黄仲秋 2013261878 华为技术有限公司手机出口存在的问题及对策分析.zip

- python_training:Python新手训练营,面向对象的编程第2部分

- 网站:简介CS 2的htmlcss文件

- insclix.ui.gwt:ui包装器组件

- 古牌楼3d模型

- 工伤事故报告表excel模版下载

- Learnist:这是在线课程网站登陆页面的基本前端网页设计