DDRx关键技术和原理解析:差分时钟与数据选取脉冲

136 浏览量

更新于2024-09-01

收藏 512KB PDF 举报

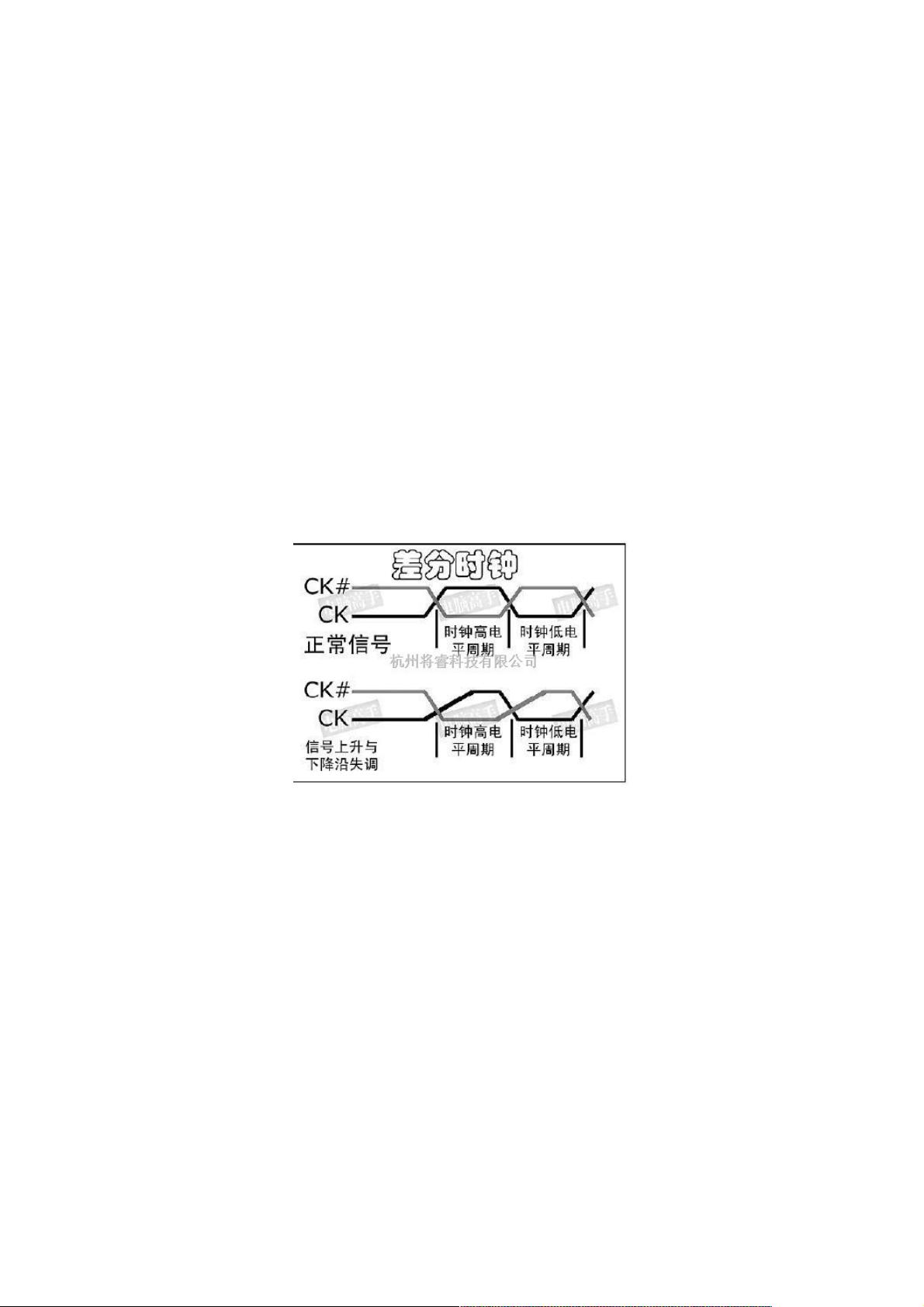

本文将深入探讨数据转换/信号处理中的关键技术DDRx,重点是差分时钟技术和数据选取脉冲(DQS)。首先,差分时钟技术在DDR内存系统中起着至关重要的作用。尽管许多人误认为CK#(CKN)是第二个触发时钟,实际上,它是用来校准触发时钟的,确保在数据传输过程中,由于CK的上升沿和下降沿之间的间隔(即周期)保持稳定。由于温度和电阻性能变化可能导致这个间隔不一致,CK#通过其特有的变化规律来补偿这一影响,从而保证数据传输的准确性。

DQS(Data strobe)信号,作为DDR内存中的另一个重要组成部分,负责在一个时钟周期内标识出每个数据传输周期,使得数据的同步传输得以实现。它在写入时由主控芯片发送,在读取时由DRAM芯片生成并反馈给主控。DQS与数据信号的同步至关重要,因为它们共同决定了何时进行数据交换。在读取过程中,数据实际上可能在DQS信号生成之前就已经准备好了,这就是所谓的预取操作。然而,由于预取的存在,DDR内存对数据从CAS(Command/address strobe)信号发出到DQS触发之间的时间间隔(tAC)有特定的要求,例如在DDR2-66标准下,tAC的范围有一定的限制。

总结来说,理解并掌握这些关键技术对于有效地设计和优化DDR内存系统至关重要,它们确保了数据的高效、准确传输,是现代高性能计算机和电子设备中不可或缺的信号处理基础。

263 浏览量

2021-10-29 上传

2022-08-04 上传

2024-10-25 上传

2024-10-25 上传

2024-10-25 上传

2024-11-18 上传

2024-11-25 上传

2024-11-27 上传

weixin_38717143

- 粉丝: 3

- 资源: 945

最新资源

- Java 制造业 MES 生成管理系统源码

- 按光速标记:Lightspeed设计团队可以设置CC标记

- Color Sudoku-开源

- FPGA蓝牙串口实验

- BoxInvert:用于高级图像反转的计算机视觉工具

- PugDoper-Compose:PupDopter:dog:是采用:red_heart:和:rocket:Jetpack Compose #AndroidDevChallenge的Puppy收养应用程序构建

- purescript-halogen-sprite-editor:用PureScript Halogen编写的Sprite编辑器

- CakePHP php框架 v3.7.2

- dbforge for sqlserver 2019.zip

- Coldest-开源

- college-quora:大学法定人数

- 1轴向诱导因a与周向诱导因子b迭代的程序.zip_1轴向诱导因a与周向诱导因子b迭代的程序_articlenyh_systemc

- web-components-slides:有关Web组件的幻灯片

- redis-desktop-manager-2020.4.0.0

- CustomAccelerateBall:加速球,加速球

- 基于SpringBoot的HRM(人力资源管理)系统前后端+SQL.rar