Allegro约束管理器进阶指南

"约束管理器-allegro高手进阶.pdf" 是一本针对 Allegro 软件高级用户的教程,详细介绍了如何使用约束管理器进行高效的设计管理。这本书涵盖了从基本概念到高级应用的各种主题,旨在帮助用户提升在 Allegro 中进行电路设计的技能。

Allegro 是 Cadence 设计系统公司开发的一款高级PCB设计软件,约束管理器是其核心功能之一,用于管理和优化设计中的各种约束,确保设计满足电气、信号完整性和时序要求。

在第一章中,作者介绍了约束管理器的基本概念和界面。约束管理器简介部分阐述了其在设计流程中的重要性,而界面简介则详细讲解了 worksheetselector、用户接口和 View 选项等关键组件,帮助用户熟悉工作环境。

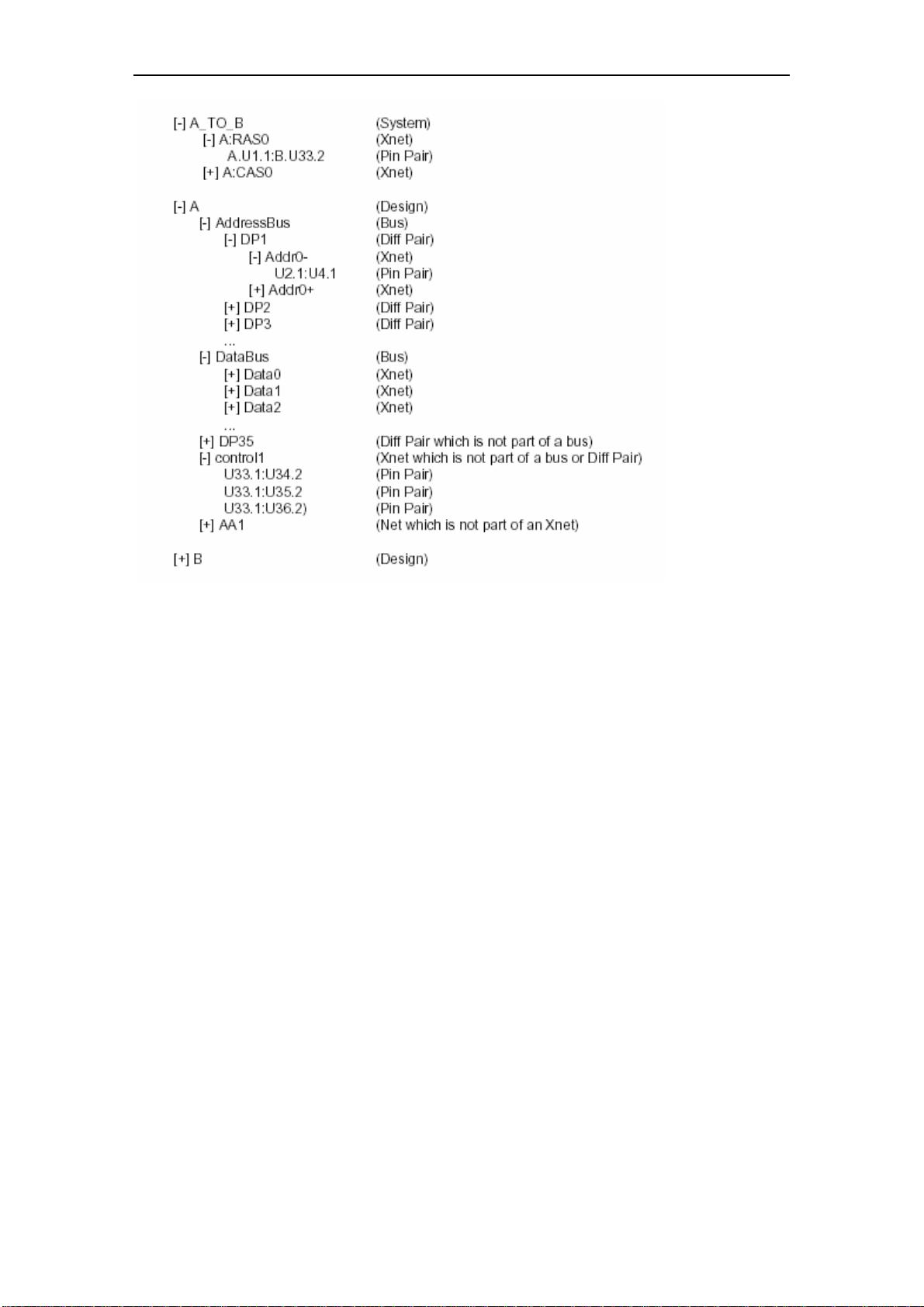

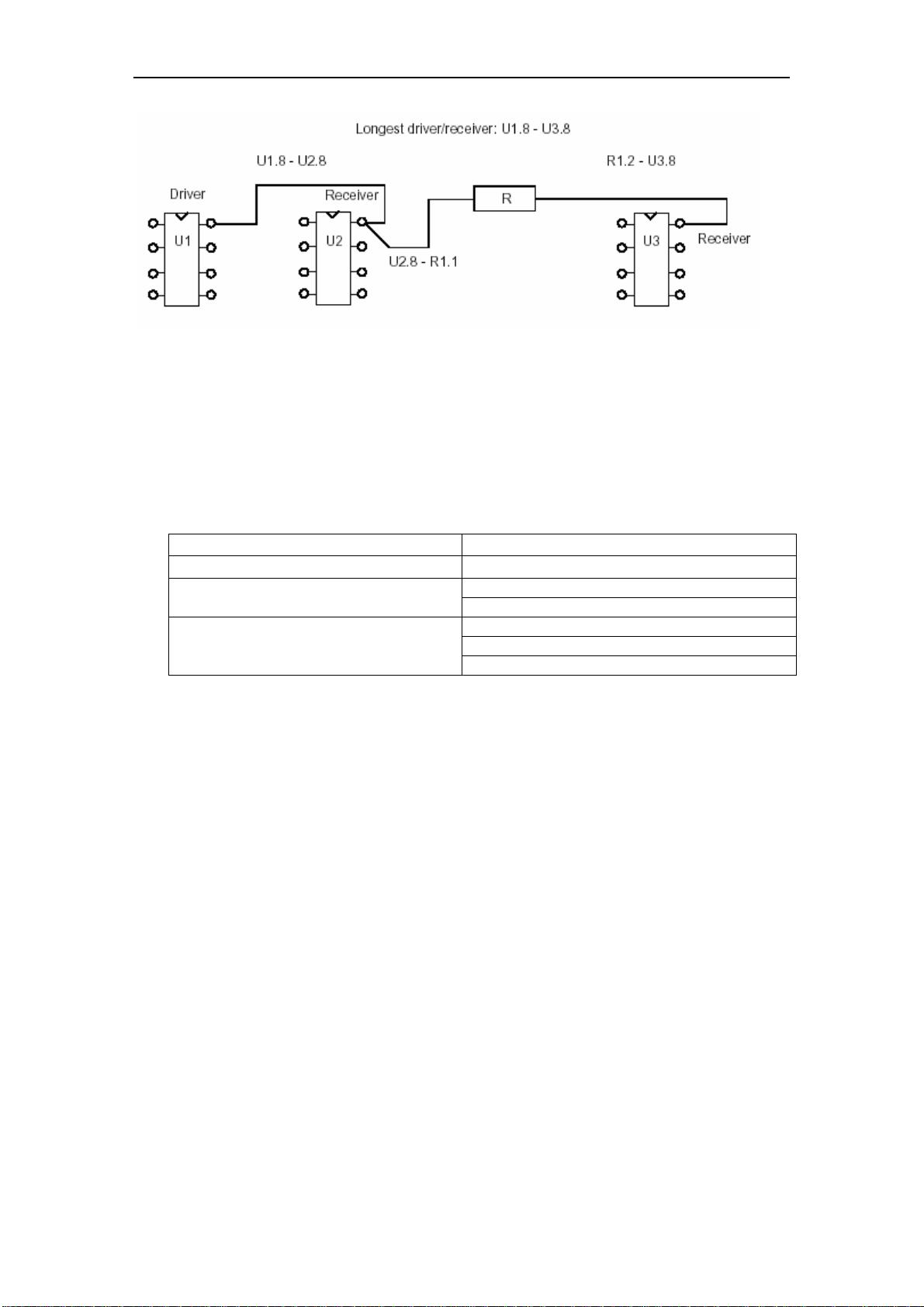

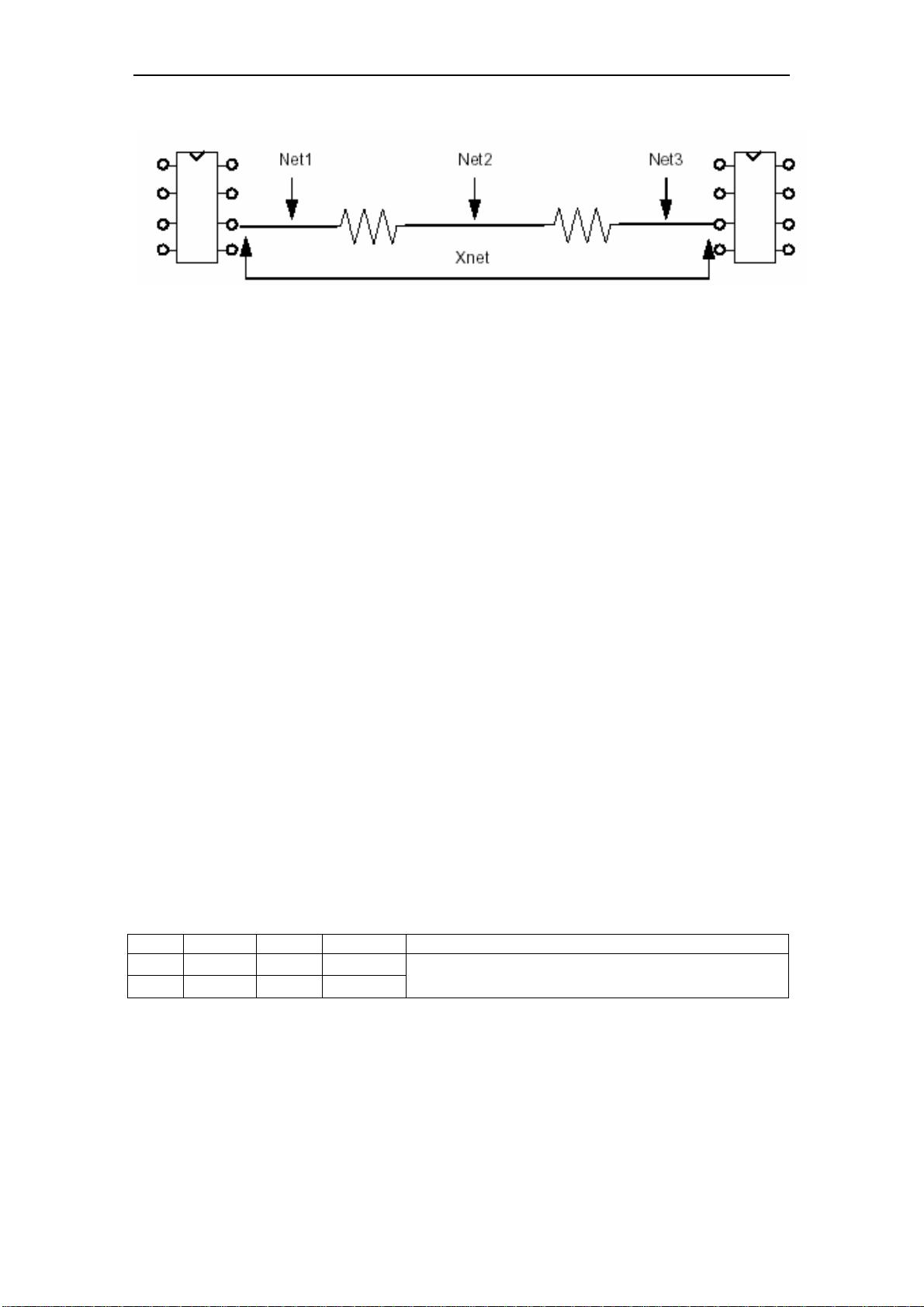

第二章深入讨论了各种设计对象,如 PIN-PAIRS、NETS 和 XNETS、BUSES、MATCHGROUPS 以及 DIFFPAIRS。PIN-PAIRS 规则允许用户定义特定的连接关系;NETS 和 XNETS 是网络分类,分别代表常规网络和扩展网络;BUSES 用于处理总线信号;MATCHGROUPS 和 DIFFPAIRS 关注于信号匹配和差分对的设定,包括目标PIN对的确定和差分对规则的配置。

第三章介绍了如何设置网络的走线约束,包括最大最小传输延迟、相对传输延迟以及差分对约束的设定,同时提供了查看网络规范格式和物理格式的方法,以确保设计的电气性能。

第四章关注时序和信号完整性约束的设置,时序约束确保逻辑路径满足时间要求,而信号完整性约束则关注信号质量,包括电气属性和反射属性的约束。

第五章讲解了电子约束(ECSET)的创建、应用以及如何忽略默认约束值,帮助用户自定义设计规则。

第六章介绍了 ECOS(Electrical Constraint Operating System)的实现,包括在原理图中添加、修改、查看和删除约束的步骤。

第七章详细阐述了在原理图与PCB之间同步约束的过程,包括从原理图输出约束、在PCB中查看和添加约束,以及两种不同的同步模式:用原理图约束覆盖PCB约束或导入PCB中的约束变更。

该文档通过实例和详细步骤,为 Allegro 用户提供了一个全面的约束管理指南,是提升设计效率和精度的宝贵资源。

点击了解资源详情

144 浏览量

111 浏览量

2023-04-24 上传

309 浏览量

111 浏览量

250 浏览量

点击了解资源详情

点击了解资源详情

XRF83

- 粉丝: 3

- 资源: 15

最新资源

- 2016“华山杯”CTF php250.rar

- 基于matlab的杂草优化算法IWO仿真+仿真操作录像

- HTML5五角星探照灯文字效果特效代码

- LZW-Compression:第一次提交

- 2018--D--

- 女巫 高清壁纸 新标签页 热门传说 主题-crx插件

- lollor.github.io

- StackStuff:各种测试的源代码

- 辛格洛

- CSS3鼠标经过文字分裂特效特效代码

- win7摄像头软件 计算机自带摄像头

- github_stats_report:与机器共存GitHub Stats报告

- 注册:由ReactJ和nodeJ组成的注册平台

- yamlw_vststask:yamlw的VSTS任务

- RankPook.AdmireTop.gaKlJNg

- Girly 新标签页 热门彩色 高清壁纸 主题-crx插件