Xilinx AXI to APB桥接器设计指南

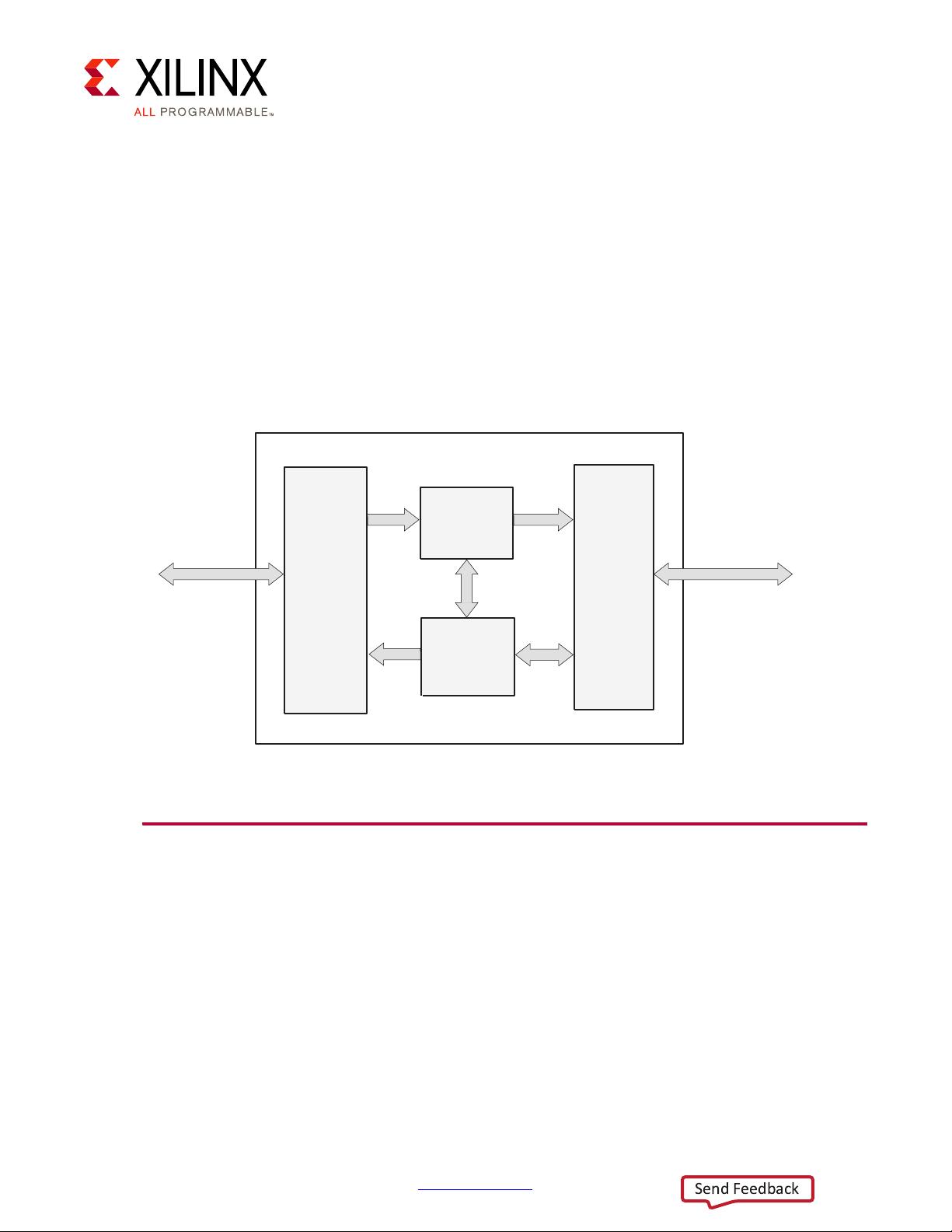

AXItoAPBBridge是Xilinx公司提供的一个逻辑内核IP,用于在Advanced eXtensible Interface (AXI) 和 Advanced Peripheral Bus (APB) 之间构建桥接。该产品指南适用于Vivado Design Suite,特别关注版本3.0,发布日期为2015年11月18日。AXItoAPBBridge的主要功能包括:

1. 功能概述:

- 这个设计允许AXI4-Lite协议的设备与遵循APB协议的外围设备进行数据交换。

- 它支持标准合规性,确保与其他系统组件无缝集成。

- 提供了通用设计指南,包括时钟管理、复位机制以及详细的时序图。

2. 产品规格:

- AXI4-Lite接口提供了灵活的数据传输,适合高性能应用。

- APB Master接口负责从APB总线读取和写入数据。

- IP占用资源情况和端口描述提供了对核心占用硬件资源的详细信息。

3. 设计流程:

- 设计者可以按照指南定制和生成核心IP。

- 需要考虑约束设置,如时钟树、电源管理等。

- 设计流程包括模拟、综合和实施步骤,确保设计的正确性和性能。

4. 示例设计:

- 提供了一个详细的示例设计,展示了如何在实际项目中使用AXItoAPBBridge。

- 包括设计目录结构、仿真和调试过程。

5. 测试与升级:

- 文档指导用户如何迁移至Vivado Design Suite和进行版本升级。

- 提供了在线帮助和调试工具,便于解决可能遇到的问题。

AXItoAPBBridge是一个实用的解决方案,适用于那些希望在AXI和APB之间建立连接,或者需要在高性能和低功耗的系统中优化资源分配的工程师。通过遵循本指南,设计师可以确保IP的正确配置和高效利用,同时享受到Xilinx产品的稳定性和安全性特性,如TrustZone和TEE(Trusted Execution Environment)的支持。

847 浏览量

316 浏览量

223 浏览量

253 浏览量

160 浏览量

152 浏览量

445 浏览量

IC小兵

- 粉丝: 17

- 资源: 7

最新资源

- React性的

- Distributed-Blog-System:分布式博客系统实现

- CloseMe-crx插件

- 欧式建筑立面图纸

- 北理工自控(控制理论基础)实验报告

- yolov7升级版切图识别

- 作业-1 --- IT202:这是我的第一个网站

- hit-and-run:竞争性编程的便捷工具

- Pytorch-Vanilla-GAN:适用于MNIST,FashionMNIST和USPS数据集的Vanilla-GAN的Pytorch实现

- SNKit:iOS开发常用功能封装(Swift 5.0)

- 创意条形图-手机应用下载排行榜excel模板下载

- 项目36

- 通过混沌序列置乱水印.7z

- reactive-system-design

- getwdsdata.m:从 EPANET 输入文件中获取配水系统数据-matlab开发

- 100多套html模块+包含企业模板和后台模板(适合初级学习)