Xilinx ISE12.3 ISim时序仿真实用指南

本指南深入探讨了Xilinx ISE12.3版本的ISim时序仿真的各个方面,专为那些希望充分利用这一高级FPGA设计工具进行系统级验证的工程师而设计。ISim是Xilinx ISE设计环境中的核心组件,用于模拟设计行为,确保硬件与软件接口的兼容性和性能。UG682(v13.3)发布于2011年10月19日,包含了详细的步骤、实例和最佳实践,涵盖了以下关键知识点:

1. 仿真概述:

- ISim提供了功能强大的时序仿真功能,支持波形视图、逻辑分析、时序分析和信号完整性检查,帮助设计师在实际硬件之前发现潜在的问题。

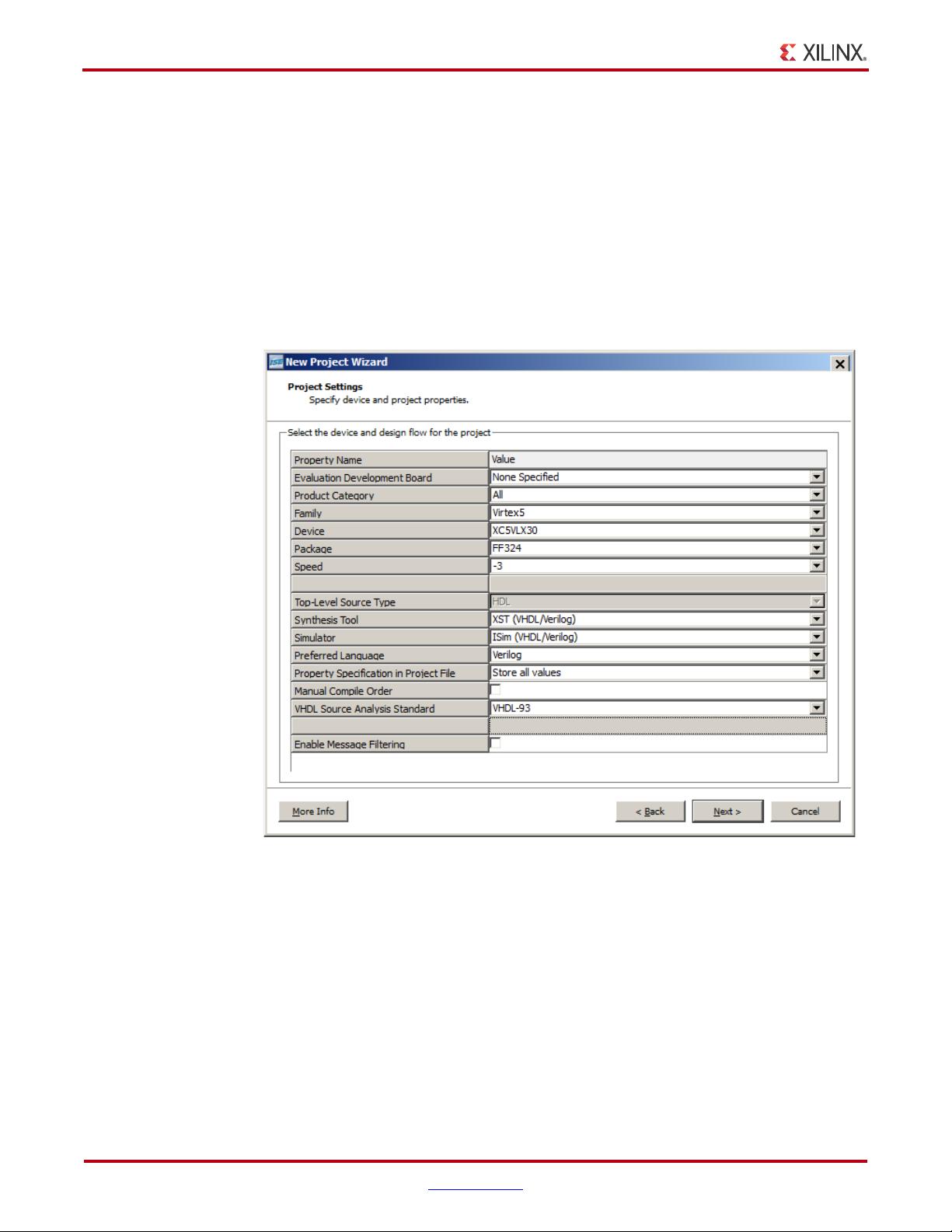

2. 安装与配置:

- 介绍如何安装并配置ISim,包括设置工具路径,配置项目文件,以及连接到相应的Xilinx FPGA开发板。

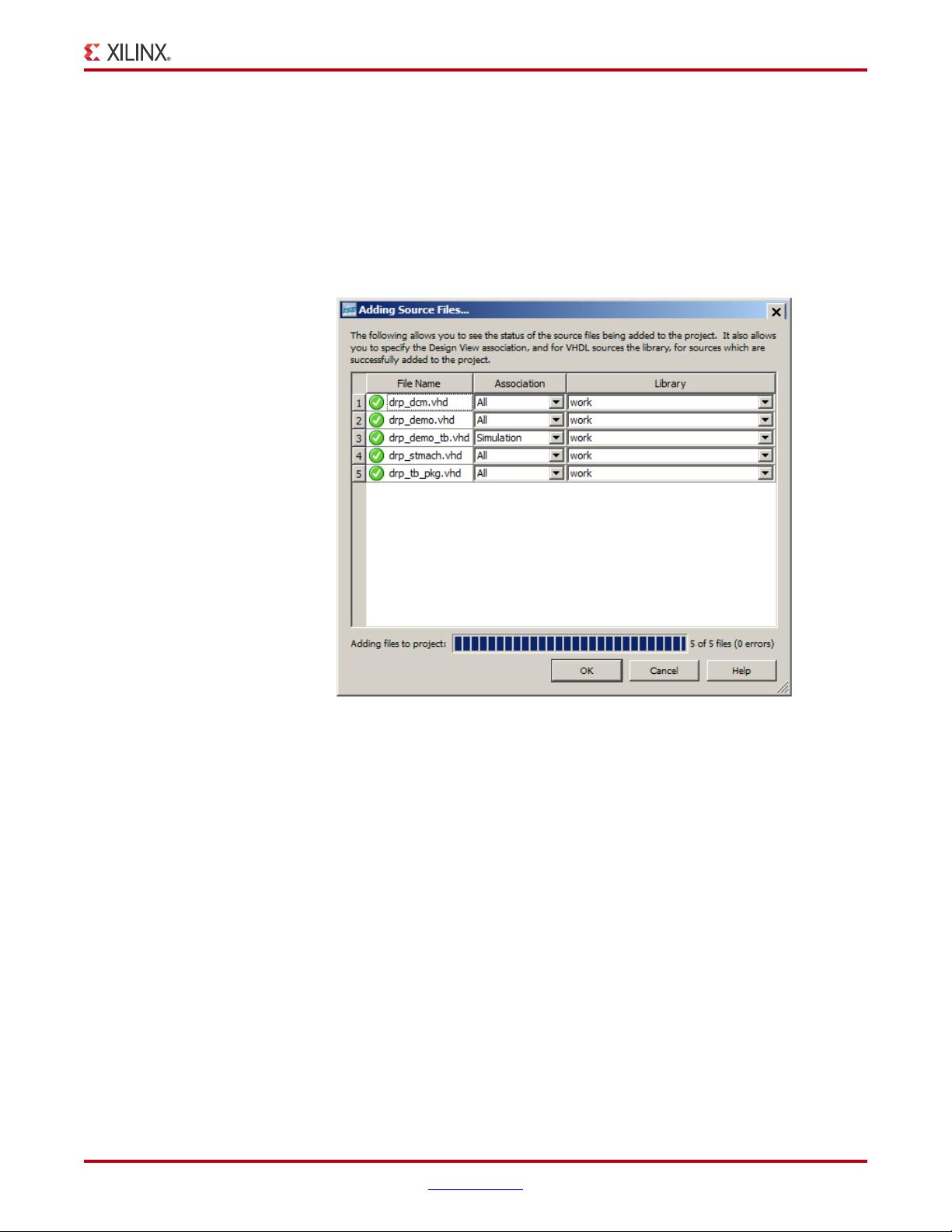

3. 模型创建:

- 解释如何构建和导入设计的VHDL或Verilog模型,以及如何设置设计参数和接口。

4. 时序分析:

- 描述了ISim的时钟分析器,如何设置时钟树分析、路径延迟测量,以及如何识别关键路径和潜在的时序问题。

5. 信号完整性分析:

- 提供了关于布线长度、负载和噪声对信号质量影响的指导,以及如何使用ISim工具进行SI/PI(信号完整性/电源完整性)分析。

6. 调试与日志管理:

- 如何设置断点、观察点和触发器,以及如何阅读和理解仿真报告和日志,以便找出设计中的异常。

7. 性能优化与模拟设置:

- 提供了关于如何调整仿真速度、设置并行处理和内存管理的技巧,以提高仿真效率。

8. 案例研究与实战演练:

- 通过一系列实例演示了ISim的实际应用,包括从简单模块到复杂系统的设计验证过程。

9. 版权和许可:

- 明确了文档的使用权限,强调未经Xilinx事先书面同意,用户不得复制、分发或以任何形式公开传播该文档。

尽管此份指南针对的是早期的ISE12.3版本,但其核心概念和功能仍然适用于后续的Xilinx ISE工具。对于现代的FPGA开发者来说,理解这些基础原理和工具使用方法仍然是至关重要的。随着技术发展,ISim的功能可能有所增强,但基本的工作流程和原则是相通的。因此,熟悉ISim的深入教程对于持续跟进Xilinx平台的最新进展至关重要。

102 浏览量

2021-05-09 上传

2021-03-05 上传

298 浏览量

164 浏览量

UserName2010

- 粉丝: 1

最新资源

- Windows CMD命令大全:实用操作与工具

- 北京大学ACM训练:算法与数据结构实战

- 提升需求分析技巧:理解冲突与深度沟通实例

- Java聊天室源代码示例与用户登录实现

- Linux一句话技巧大全:陈绪精选问答集锦

- OA办公自动化系统流程详解

- Java编程精华500提示

- JSP数据库编程实战指南:Oracle应用详解

- PCI SPC 2.3:最新规范修订历史与技术细节

- EXT中文教程:入门到进阶指南

- Ext2核心API中文详细解析

- Linux操作系统:入门与常用命令详解

- 中移动条码凭证业务:开启移动支付新时代

- DirectX 9.0 游戏开发基础教程:3D编程入门

- 网格计算新纪元:大规模虚拟组织的基础设施

- iReport实战指南:从入门到精通