Verilog实现SPI主机接口:带寄存器寻址设计解析

"本文档详细介绍了如何使用Verilog语言实现带有寄存器寻址功能的SPI主机接口设计,适用于FPGA或CPLD应用。内容包括SPI接口协议的基础知识、特点以及具体的设计实现方法,适合Verilog初学者参考学习。"

在Verilog中实现带寄存器寻址的SPI主机接口设计,首先需要对SPI接口协议有深入的理解。SPI(Serial Peripheral Interface)是一种广泛应用的同步串行通信接口,由Motorola公司开发,主要用于连接微控制器与各种外设,如EEPROM、Flash、RTC、ADC等。SPI接口仅需四根信号线:主设备时钟(SCK)、主设备输出/从设备输入(MOSI)、从设备输出/主设备输入(MISO)和从设备选择(SS),这使得它在硬件设计上具有高度的简洁性和成本效益。

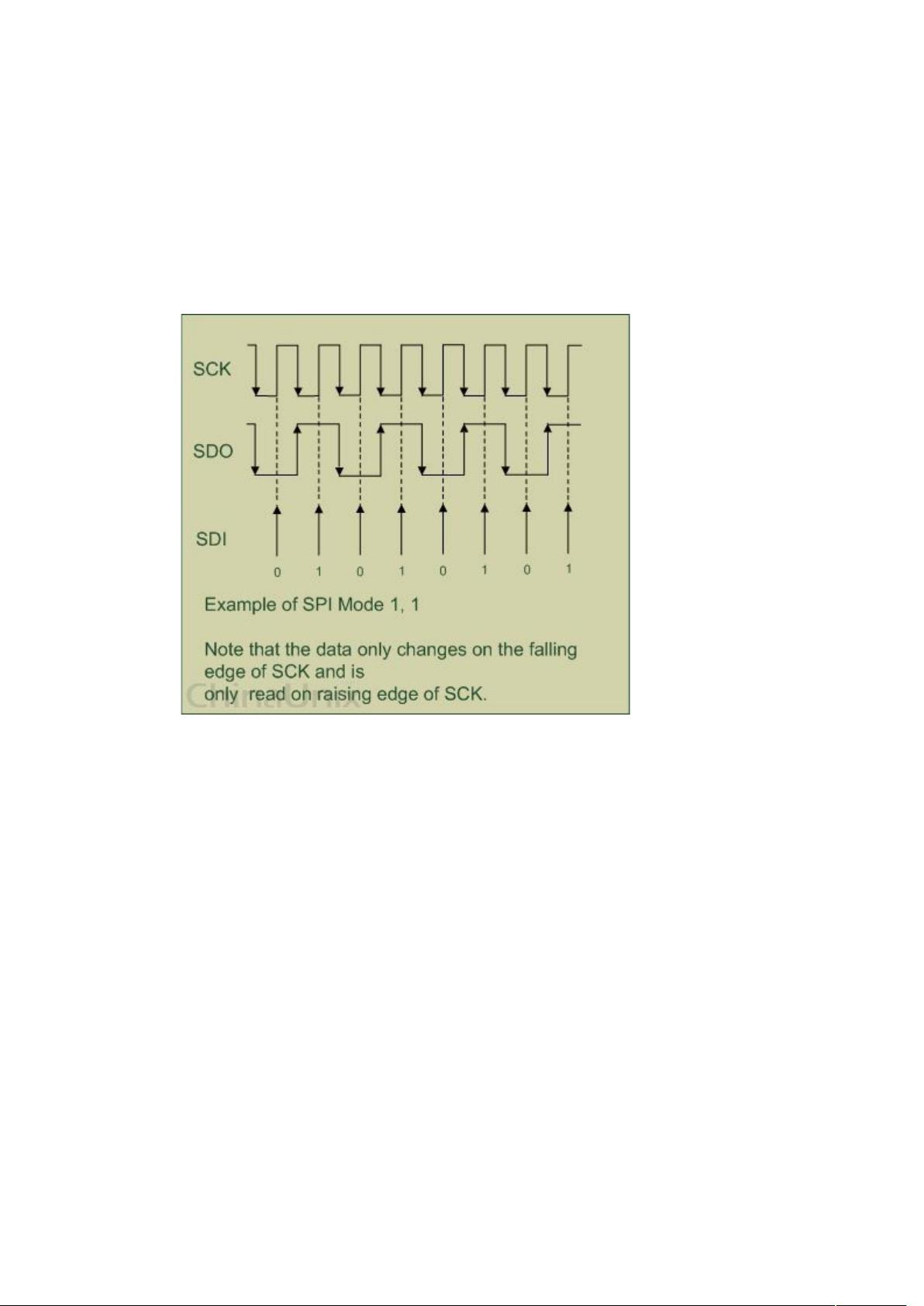

SPI通信模式采用主-从架构,即通信过程由主设备发起并控制。主设备提供时钟信号,通过片选信号选择与哪个从设备通信。从设备依赖于主设备提供的时钟信号,自身不产生时钟,没有时钟则无法正常工作。同步通信方式意味着数据传输与主设备产生的时钟信号同步,通过时钟极性(CPOL)和时钟相位(CPHA)来确定数据采样的时刻,确保数据在主从设备间的准确传输。

在Verilog实现SPI主机接口时,关键在于构建SPI协议所需的时序逻辑,包括时钟发生器、数据移位寄存器、片选控制逻辑以及寄存器寻址机制。寄存器寻址功能允许主机向特定的从设备地址发送数据或接收数据,通常需要一个地址总线和相应的解码逻辑来确定目标从设备。设计中,可能需要定义一个状态机来管理SPI通信的各个阶段,例如初始化、发送地址、发送数据、接收数据和结束通信等。

具体实现步骤可能包括:

1. 定义SPI接口的信号接口,包括SCK、MOSI、MISO和SS信号。

2. 设计状态机,控制SPI通信的流程。

3. 实现时钟发生器,生成满足SPI协议的时钟信号。

4. 编写地址解码逻辑,根据输入的地址选择对应的从设备。

5. 设计数据移位寄存器,用于在时钟脉冲下发送和接收数据。

6. 集成所有组件,完成完整的SPI主机接口模块。

在编写Verilog代码时,应遵循良好的编程风格,确保代码可读性强、易于维护。此外,还需要进行仿真验证,确保设计符合SPI协议规范,并能在实际硬件上正确工作。对于初学者来说,这样的项目提供了很好的实践机会,可以帮助理解并掌握Verilog语言和SPI通信协议。

2019-05-30 上传

2021-07-13 上传

点击了解资源详情

2019-07-22 上传

2024-06-09 上传

2022-07-15 上传

点击了解资源详情