MaxplusII与VHDL实验:位全加器设计与验证

版权申诉

117 浏览量

更新于2024-07-02

收藏 6.23MB PPT 举报

"这是一份针对VHDL实验的详细指导,主要内容围绕着如何使用EDA工具MaxPlus II设计和实现位全加器。实验的主要目的是让学生掌握MaxPlus II的使用,并通过实践理解VHDL语言在电路设计中的应用。全加器是基础逻辑设计,它由两个半加器和若干个或门组成,通过结构描述方法在顶层VHDL中模块化设计。

实验分为几个关键步骤:

1. 实验准备:首先,创建一个专门的工程文件夹,文件夹名需遵循特定规则,不能包含中文和空格。例如,可以命名为'myadder'。

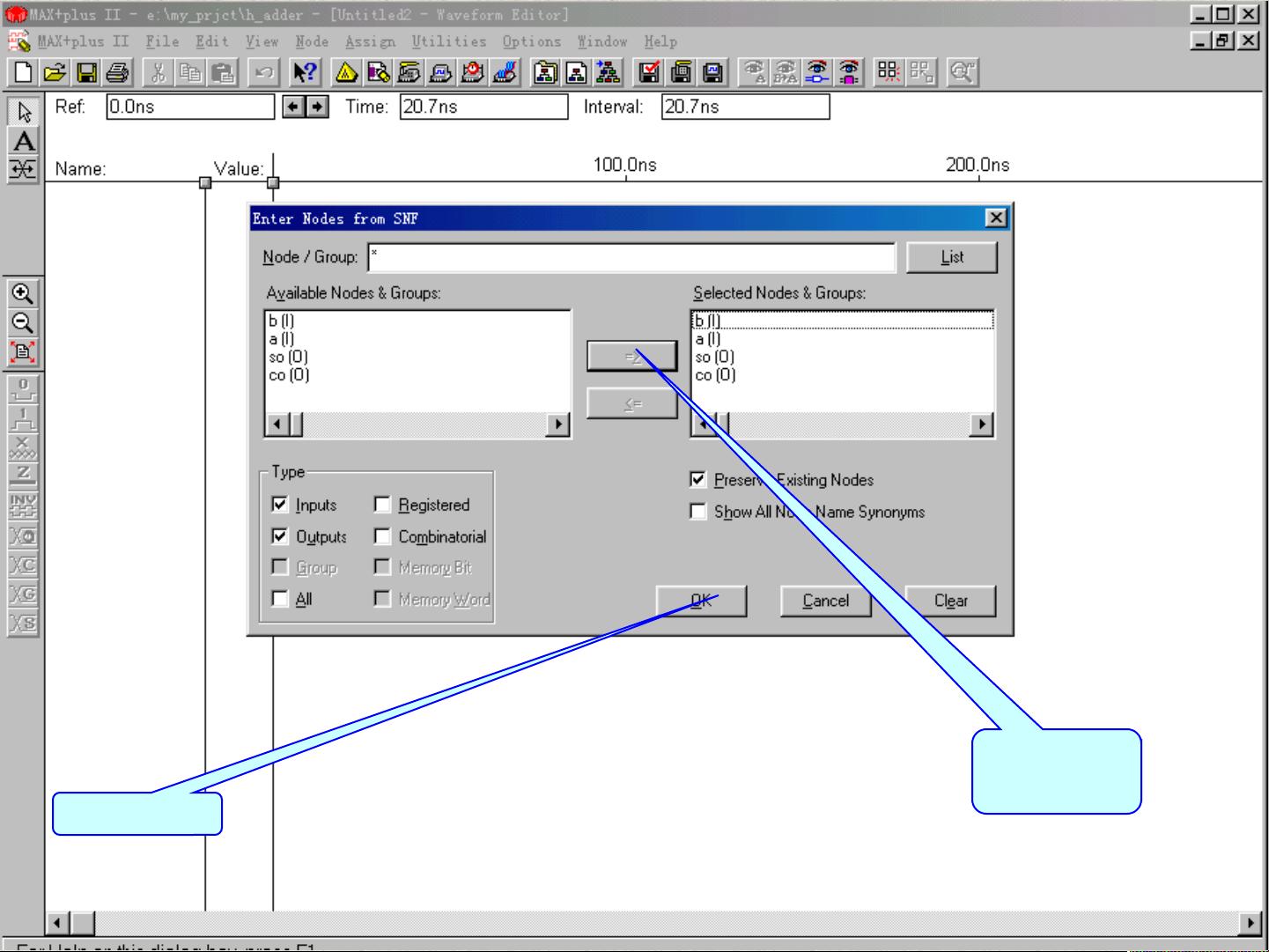

2. 设计输入:通过MaxPlus II,学生需以原理图或VHDL文本的形式输入设计。对于VHDL,从建立工作库开始,新建一个VHDL源文件(如'h_adder.vhd'),并输入相应的半加器设计代码。

3. 项目设置:将设计文件保存后,将其设置为项目,以便于后续操作。接下来,选择合适的硬件目标器件,并进行编译和综合,这是将VHDL转化为可执行的硬件描述语言的过程。

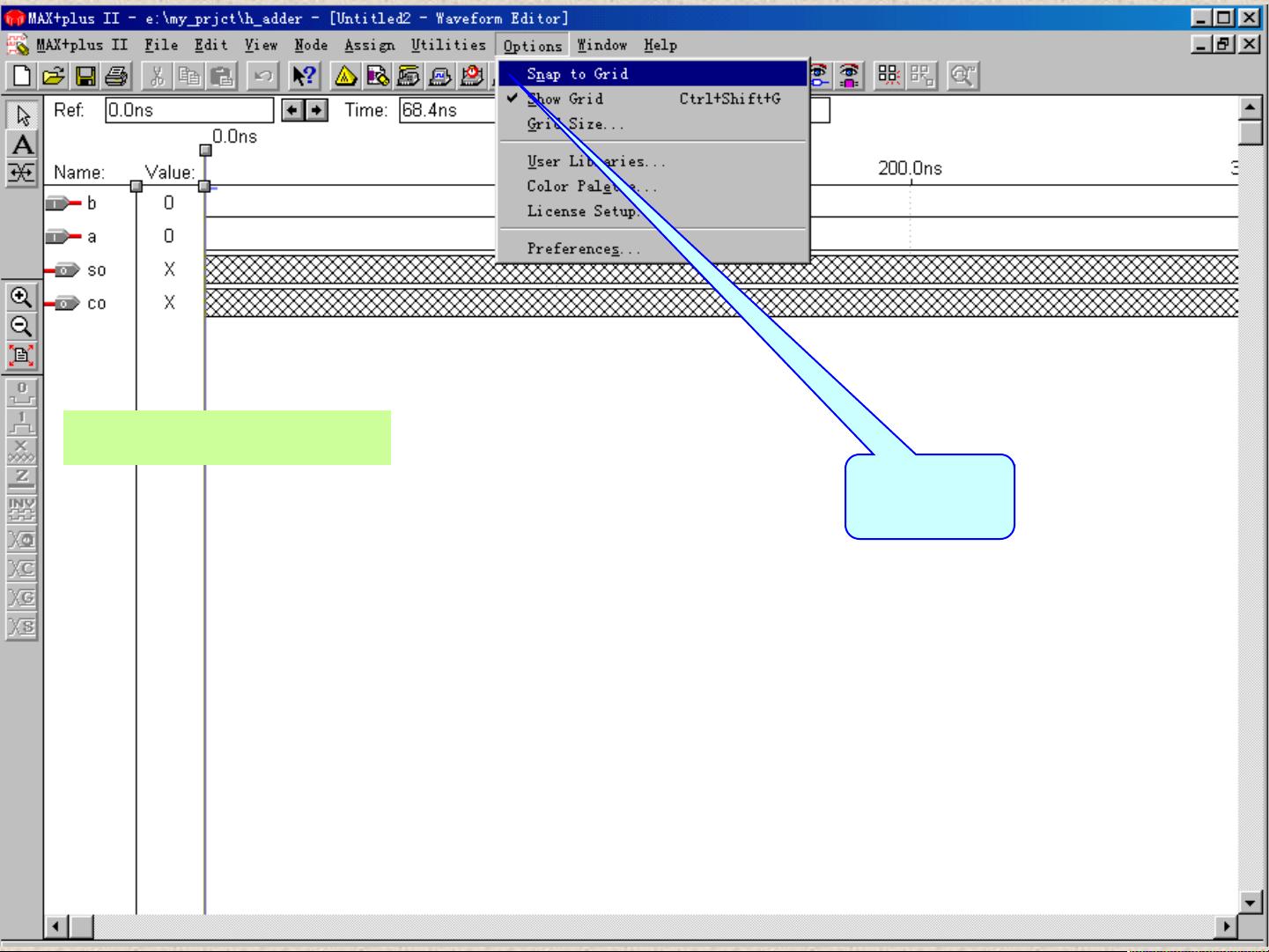

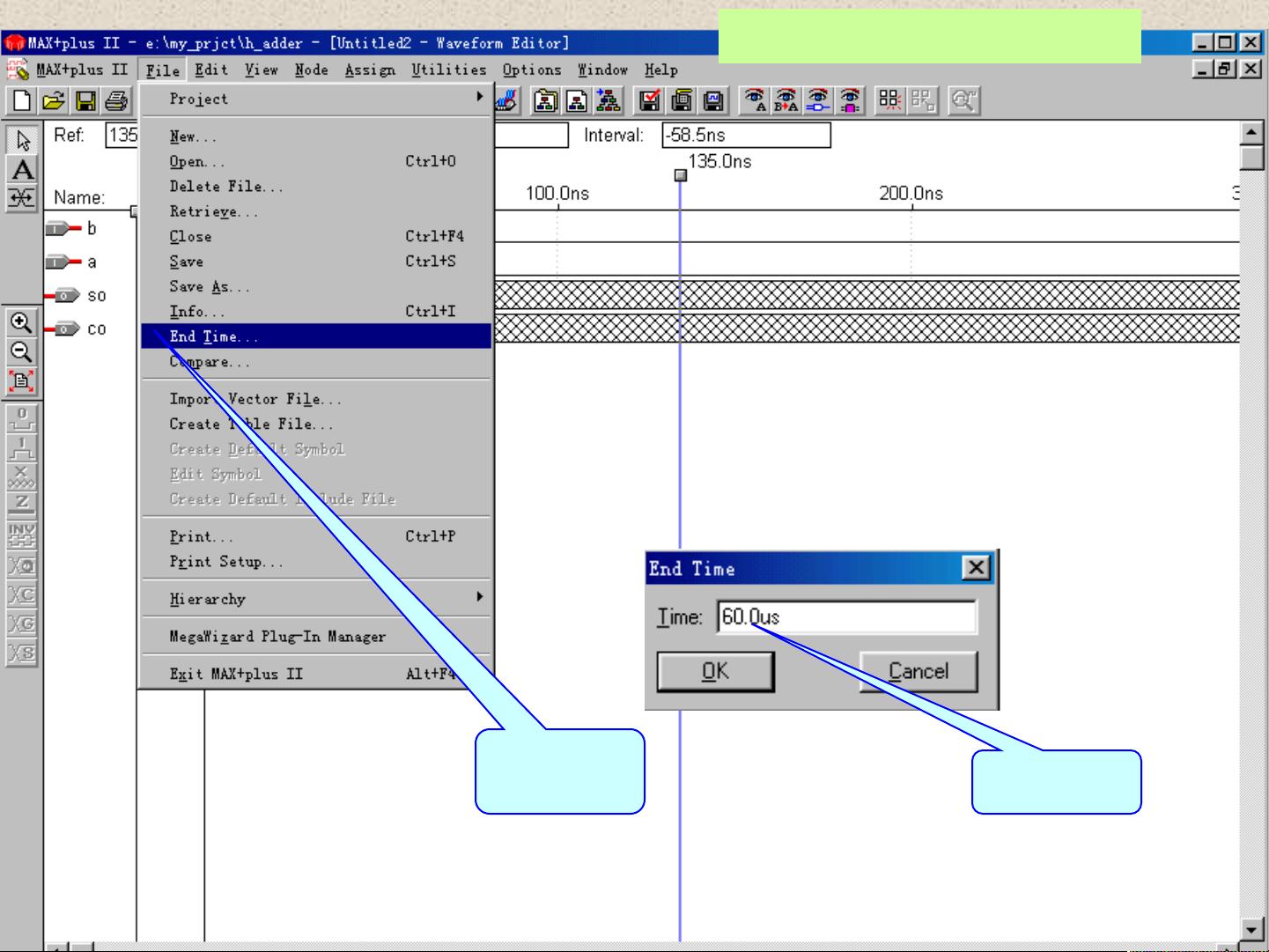

4. 仿真与验证:进行时序仿真以测试电路功能,观察仿真波形。然后,锁定引脚并再次编译和综合,确保硬件兼容性。接着,将设计下载到实验箱进行实际操作,验证全加器的功能是否符合预期。

5. VHDL源程序:提供了一段VHDL代码示例,展示了半加器的具体实现,包括输入、输出以及逻辑运算过程。

6. 设计流程:整个设计过程按照清晰的步骤进行,从建立工作库、输入设计、保存和命名,再到项目设置、器件选择、仿真、硬件测试和引脚锁定,每个环节都强调了注意事项。

这份VHDL实验不仅锻炼了学生的编程技能,也加深了他们对数字逻辑电路设计和仿真技术的理解。通过这个项目,学生可以熟练运用VHDL语言,提高电路设计和调试能力,为以后的专业学习打下坚实的基础。"

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-07-04 上传

2019-07-04 上传

2022-07-14 上传

2022-06-18 上传

2022-05-07 上传

2012-03-06 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器