入门指南:时序约束源同步接口详解与分析

需积分: 0 123 浏览量

更新于2024-07-19

收藏 1.88MB PDF 举报

"时序约束资料"是一份由Altera Corporation在2016年发布的应用笔记,名为"AN433: Constraining and Analyzing Source-Synchronous Interfaces"。这份文档专为初学者设计,详细介绍了如何处理和分析源同步接口的时序问题。源同步接口是一种高速数据传输模式,其中数据源和时钟源来自同一设备,如DDR内存、HyperTransport总线和SPI-4.2标准都采用这种架构。

在源同步接口中,确保正确的时序至关重要,因为它们涉及到数据和时钟之间的精确同步。这不仅影响到系统的性能,还可能决定其能否达到预期的工作速度和稳定性。文档强调了时序分析的复杂性,并指出Synopsys Design Constraints (SDC) 格式在进行有效分析时必不可少。SDC提供了一种精确描述设计约束的工具,这对于理解和优化时序行为是至关重要的。

在阅读这份应用笔记之前,建议读者首先熟悉SDC格式以及Quartus II的TimeQuest Timing Analyzer。TimeQuest Timing Analyzer是一款用于设计验证和时序分析的工具,它能够帮助工程师分析时序路径、确定延迟、设置时序约束等,从而确保设计满足系统时序要求。

此外,应用笔记中还可能包含以下内容:

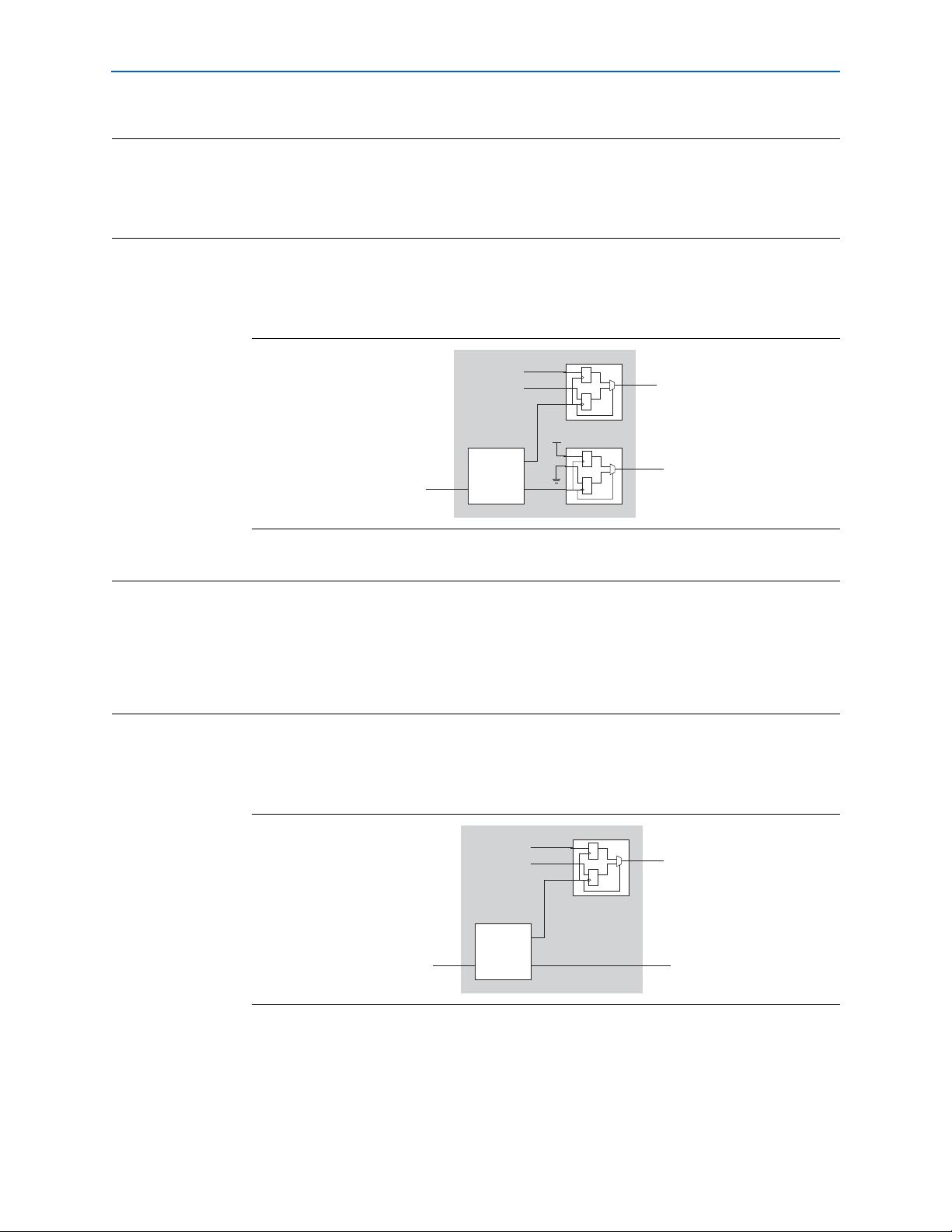

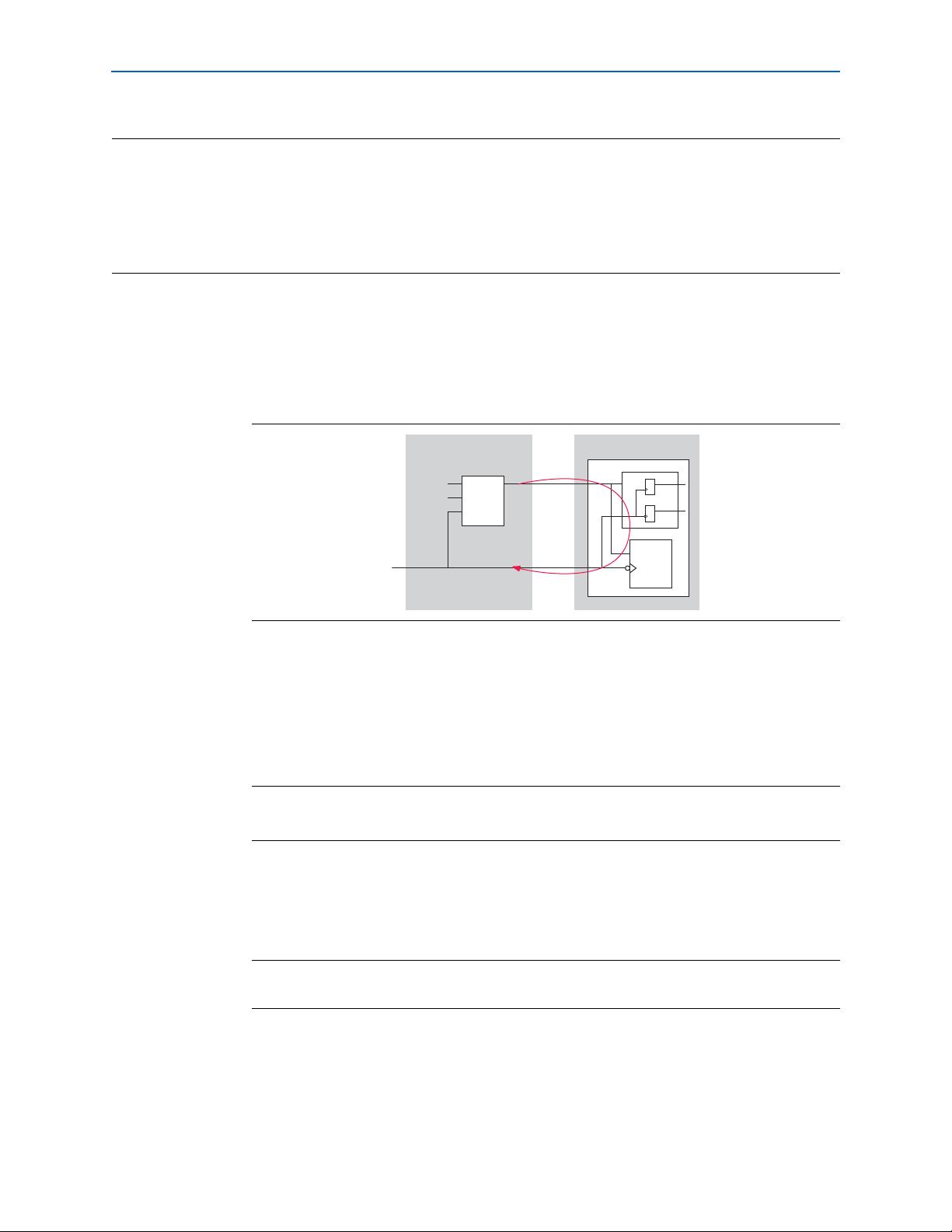

1. 接口概述:介绍源同步接口的基本结构和工作原理,包括数据和时钟的同步机制。

2. 时序约束类型:讲解不同的时序约束,如setup时间、hold时间、setup-hold时间等,以及它们在设计中的作用。

3. 常见问题与挑战:列出在设计过程中可能遇到的挑战,如信号完整性、噪声敏感性等,以及如何通过合理的约束来解决这些问题。

4. 案例研究:通过具体的例子展示如何在实际项目中应用SDC和TimeQuest Timing Analyzer进行约束和分析。

5. 最佳实践:分享优化源同步接口时序约束的实用技巧和策略,以提升设计效率和性能。

6. 参考文献:提供进一步学习和深入理解的资源,如官方手册、API文档等。

这份应用笔记是设计者和初学者理解并管理源同步接口时序约束的重要参考资料,它将理论知识与实践经验相结合,为高效的设计和分析提供了全面的指导。

2023-05-23 上传

2023-05-24 上传

2023-11-15 上传

2023-05-30 上传

2023-04-04 上传

2023-08-07 上传

zcl_33

- 粉丝: 16

- 资源: 61

最新资源

- R语言中workflows包的建模工作流程解析

- Vue统计工具项目配置与开发指南

- 基于Spearman相关性的协同过滤推荐引擎分析

- Git基础教程:掌握版本控制精髓

- RISCBoy: 探索开源便携游戏机的设计与实现

- iOS截图功能案例:TKImageView源码分析

- knowhow-shell: 基于脚本自动化作业的完整tty解释器

- 2011版Flash幻灯片管理系统:多格式图片支持

- Khuli-Hawa计划:城市空气质量与噪音水平记录

- D3-charts:轻松定制笛卡尔图表与动态更新功能

- 红酒品质数据集深度分析与应用

- BlueUtils: 经典蓝牙操作全流程封装库的介绍

- Typeout:简化文本到HTML的转换工具介绍与使用

- LeetCode动态规划面试题494解法精讲

- Android开发中RxJava与Retrofit的网络请求封装实践

- React-Webpack沙箱环境搭建与配置指南