掌握多思计算机组成原理:全加器实验与逻辑设计

本次实验是关于计算机组成原理的第一课——全加器实验。该实验主要目标是让学生熟悉多思计算机组成原理网络虚拟实验系统的操作流程,掌握全加器的基本逻辑结构、电路实现以及相关原理。实验通过实际操作,让学生理解1位和2位二进制加法器的工作过程,包括全加器的输入(Ai、Bi、Ci)和输出(Si、Ci+1)的计算逻辑。

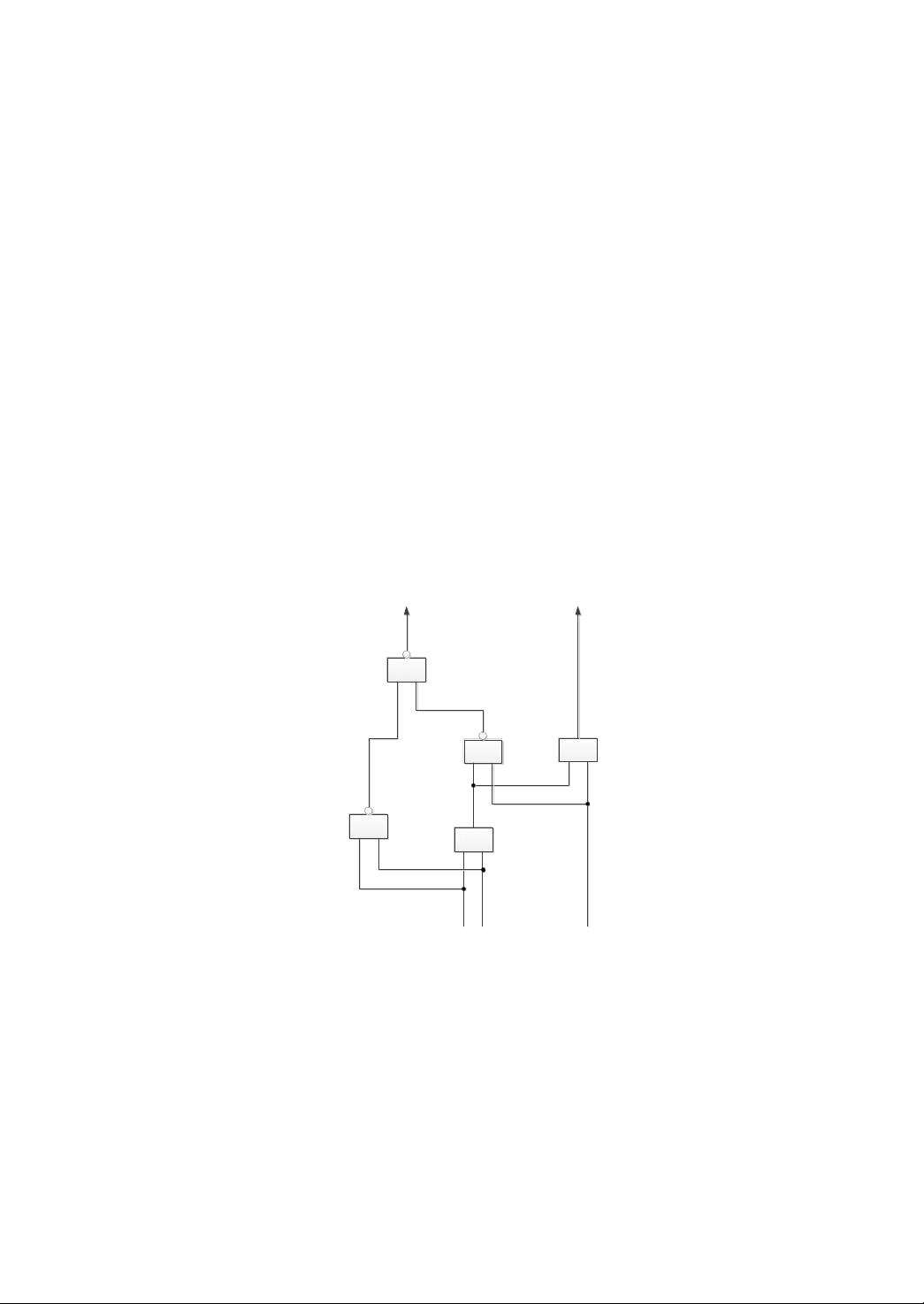

在实验的1.3节中,介绍了实验所需的元器件,如与非门、异或门、开关和指示灯,这些都是构成全加器的基本电子元件。实验电路的设计遵循全加器的逻辑方程,即Si=Ai⊕Bi⊕Ci和Ci+1=AiBi+BiCi+CiAi,这两个公式定义了全加器如何基于输入的二进制位进行加法运算,并产生相应的和输出和进位输出。

在1.4节,详细描述了实验的步骤,包括如何在虚拟实验系统中搭建电路,设置输入信号,观察和记录指示灯显示的结果。通过表格的形式,学生需要验证全加器的正确性,同时也训练了他们对实际运算结果的解析能力。

在1.6节,实验深入探讨了串行进位并行加法器的局限性,即由于进位的顺序依赖性导致运算速度较慢。提出了改进方法,即采用超前进位技术,通过预计算各位置的进位来提高效率,例如利用74ls283这样的芯片。此外,实验还触及了如何使用全加器构建补码加法/减法器的问题,指出在现代计算机中,加法和减法操作都是通过加法器来实现的,补码表示使得符号位与其他位一起处理,简化了加减运算。

这个实验不仅锻炼了学生的实践操作技能,还强化了他们对基本逻辑门电路的理解,以及计算机中加法运算原理的掌握,为后续学习更复杂的计算机体系结构打下基础。

7420 浏览量

2024-12-21 上传

378 浏览量

2773 浏览量

4551 浏览量

311 浏览量

703 浏览量

Werfgf

- 粉丝: 4361

最新资源

- 全面详实的大学生电工实习报告汇总

- 利用极光推送实现App间的消息传递

- 基于JavaScript的节点天气网站开发教程

- 三星贴片机1+1SMT制程方案详细介绍

- PCA与SVM结合的机器学习分类方法

- 钱能版C++课后习题完整答案解析

- 拼音检索ListView:实现快速拼音排序功能

- 手机mp3音量提升神器:mp3Trim使用指南

- 《自动控制原理第二版》习题答案解析

- 广西移动数据库脚本文件详解

- 谭浩强C语言与C++教材PDF版下载

- 汽车电器及电子技术实验操作手册下载

- 2008通信定额概预算教程:快速入门指南

- 流行的表情打分评论特效:实现QQ风格互动

- 使用Winform实现GDI+图像处理与鼠标交互

- Python环境配置教程:安装Tkinter和TTk