算术逻辑单元(ALU)设计与实现实验

需积分: 0 99 浏览量

更新于2024-08-05

收藏 435KB PDF 举报

算术逻辑单元(ALU)的设计与实现

本实验的目的是掌握全加器和行波进位加法器的结构,熟悉加减法运算及溢出的判断方法,掌握算术逻辑单元(ALU)的结构,并熟练使用 SystemVerilog 语言对 ALU 进行描述和实现。

一、全加器

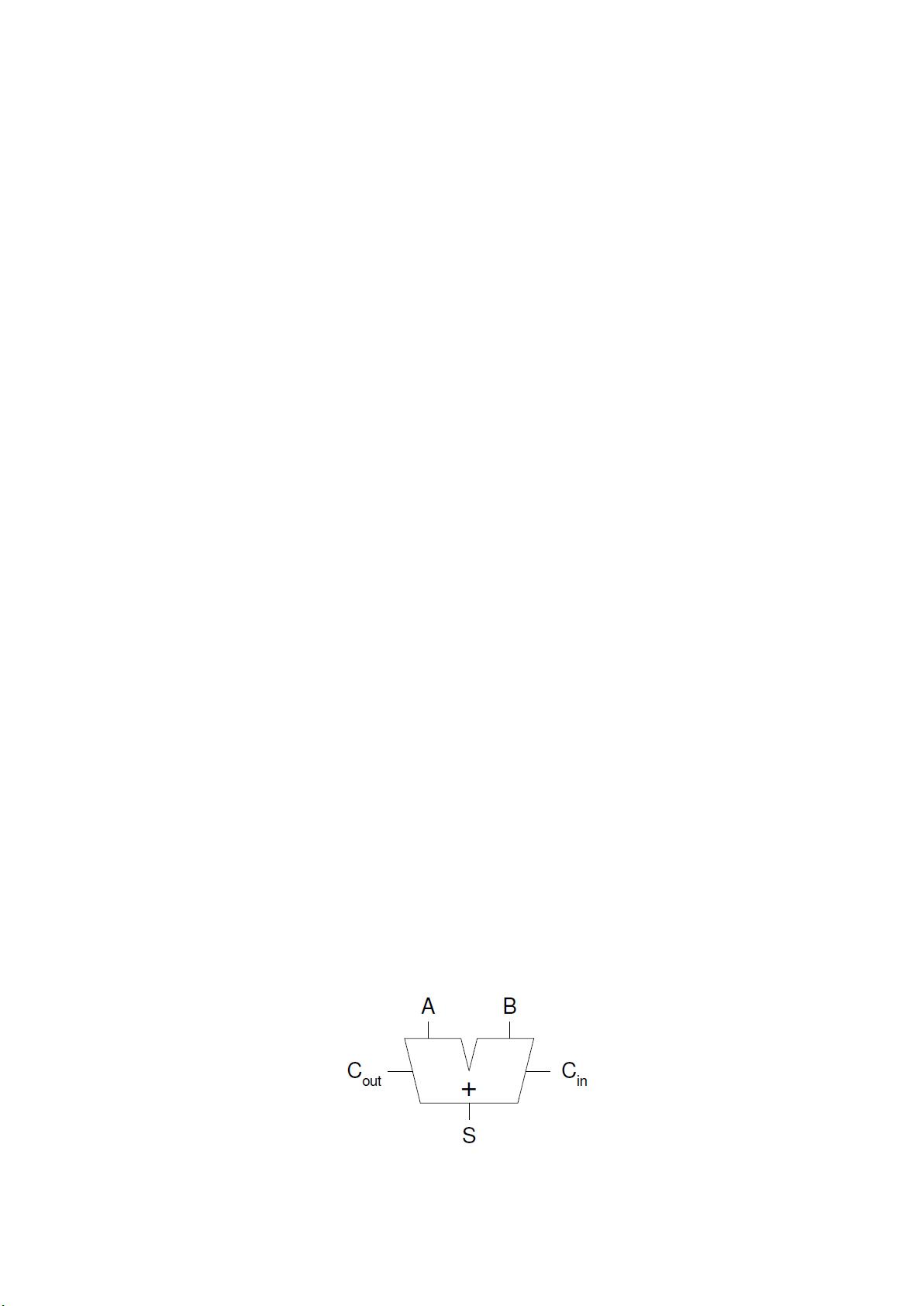

全加器是数字电路中最基本的组件之一,它可以将两个二进制数相加,并输出结果和进位。全加器的结构如图 2-1 所示,具有三个输入(A, B, Cin)和两个输出(S, Cout)。输入 A 和 B 各表示 1 位二进制数,两者相加,求和的结果通过 S 输出,进位通过 Cout 输出。

全加器的真值表如表 2-1 所示。根据真值表可以看到,全加器可以正确地实现二进制数的加法运算。

二、行波进位加法器

行波进位加法器(ripple-carry adder)是最简单的一种进位传播多位加法器(CPA)。它就是将 N 个全加器进行串联,每级的 Cout 就是下一级的 Cin,然后所有进位构成的通路称为进位链。

一个 3 位行波进位加法器的结构如图 2-2 所示。可以看到,行波进位加法器可以实现多位二进制数的加法运算。

三、算术逻辑单元(ALU)

算术逻辑单元(ALU)是现代计算机中执行算术和逻辑运算的数字电路。ALU 是计算机中处理器的最重要组成部分,甚至连功能最简单的微处理器也会包含 ALU。

ALU 的主要功能是进行二进制数的算术和逻辑运算,包括加法、减法、乘法(通常不含除法)、移位运算、逻辑与、逻辑或等等。一个 N 位 ALU 单元如图 2-3 所示。

ALU 有三个输入(A, B, aluop)和四个输出(alures0, alures1, zero, ov)。A 和 B 是两个 N 位的操作数,aluop 为操作类型控制信号,ALU 单元根据 aluop 信号确定对 A 和 B 进行何种操作。

使用 SystemVerilog 语言可以对 ALU 进行行为建模和结构化建模,实现 ALU 的设计和实现。

四、实验环境

实验环境包括操作系统(Windows 10 或 Ubuntu 16.04)、开发环境(Xilinx Vivado 2018.2)和硬件平台(远程 FPGA 硬件云平台)。这些环境将为实验提供必要的支持和资源。

五、实验原理

实验的原理是基于数字电路和计算机组成原理的。通过实验,可以掌握全加器和行波进位加法器的结构,熟悉加减法运算及溢出的判断方法,并掌握算术逻辑单元(ALU)的结构。同时,实验也将使用 SystemVerilog 语言对 ALU 进行描述和实现,为后续的实验奠定基础。

2010-07-03 上传

2022-07-05 上传

点击了解资源详情

点击了解资源详情

2022-08-03 上传

2021-12-31 上传

2015-09-08 上传

2022-08-08 上传

2021-08-18 上传