VerilogHDL入门指南:FPGA开发实战

需积分: 10 116 浏览量

更新于2024-07-28

收藏 18.38MB PDF 举报

“VerilogHDL那些事儿V3.0”是一本针对FPGA初学者的开发指导书籍,专为黑金开发板设计。本书通过简洁明了的语言和清晰的条理,帮助读者快速掌握FPGA设计的基础,特别是Verilog HDL语言的使用。

在FPGA设计中,Verilog HDL是一种广泛应用的硬件描述语言,它允许设计师以结构化的方式描述数字系统的逻辑行为。本书的第一章“前窥”引入了FPGA和Verilog HDL的基本概念,让读者对这一领域有一个初步的认识。

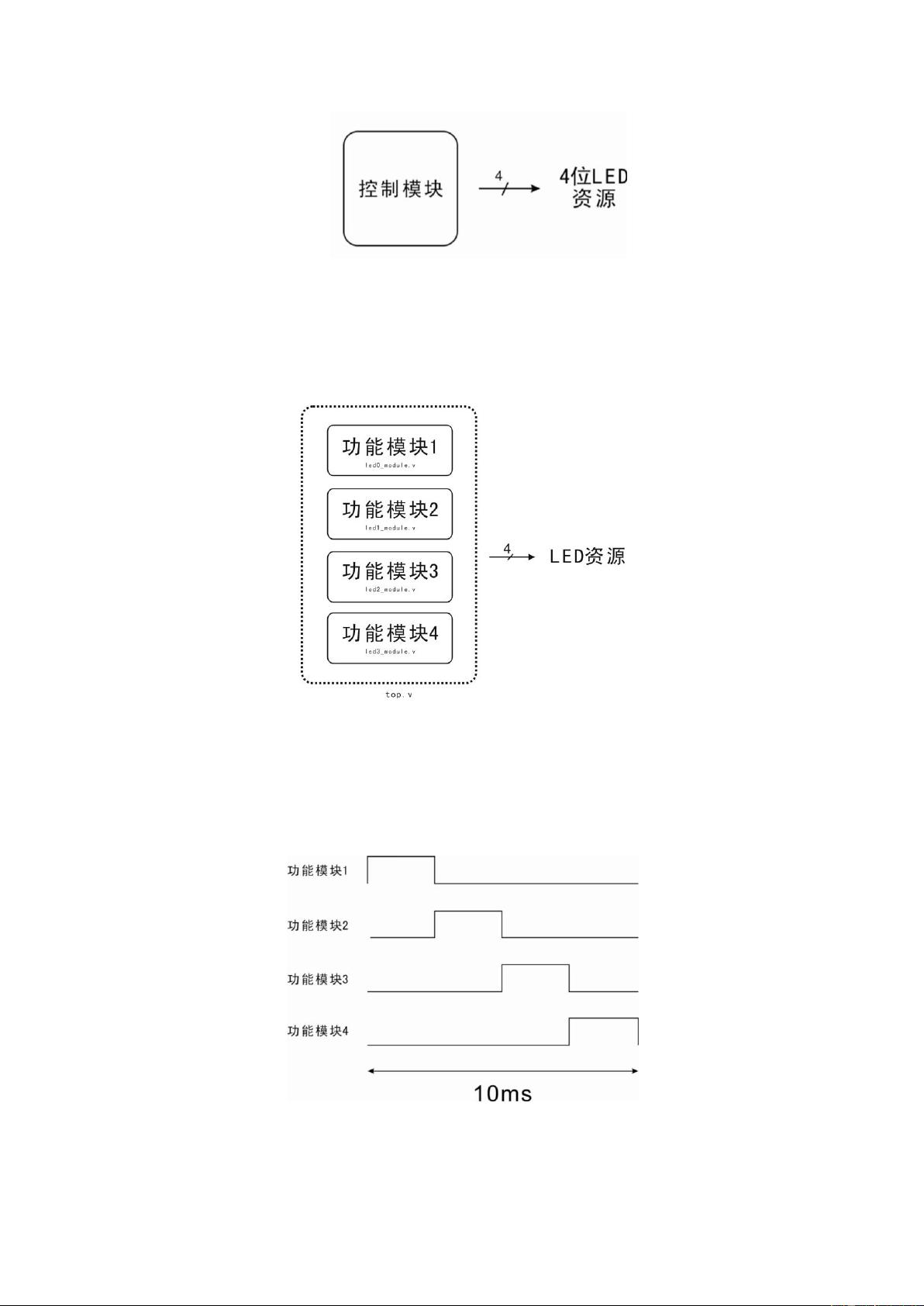

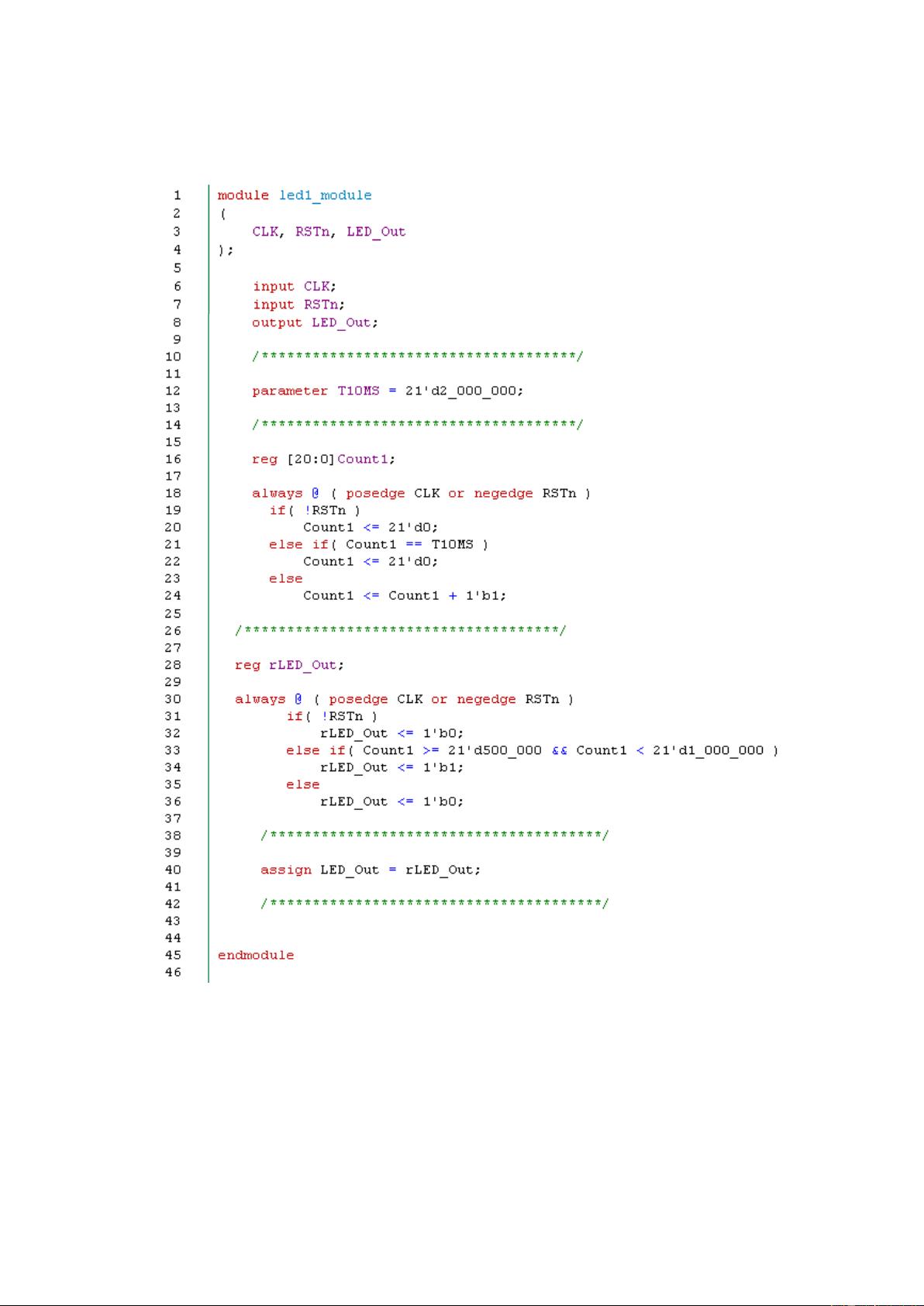

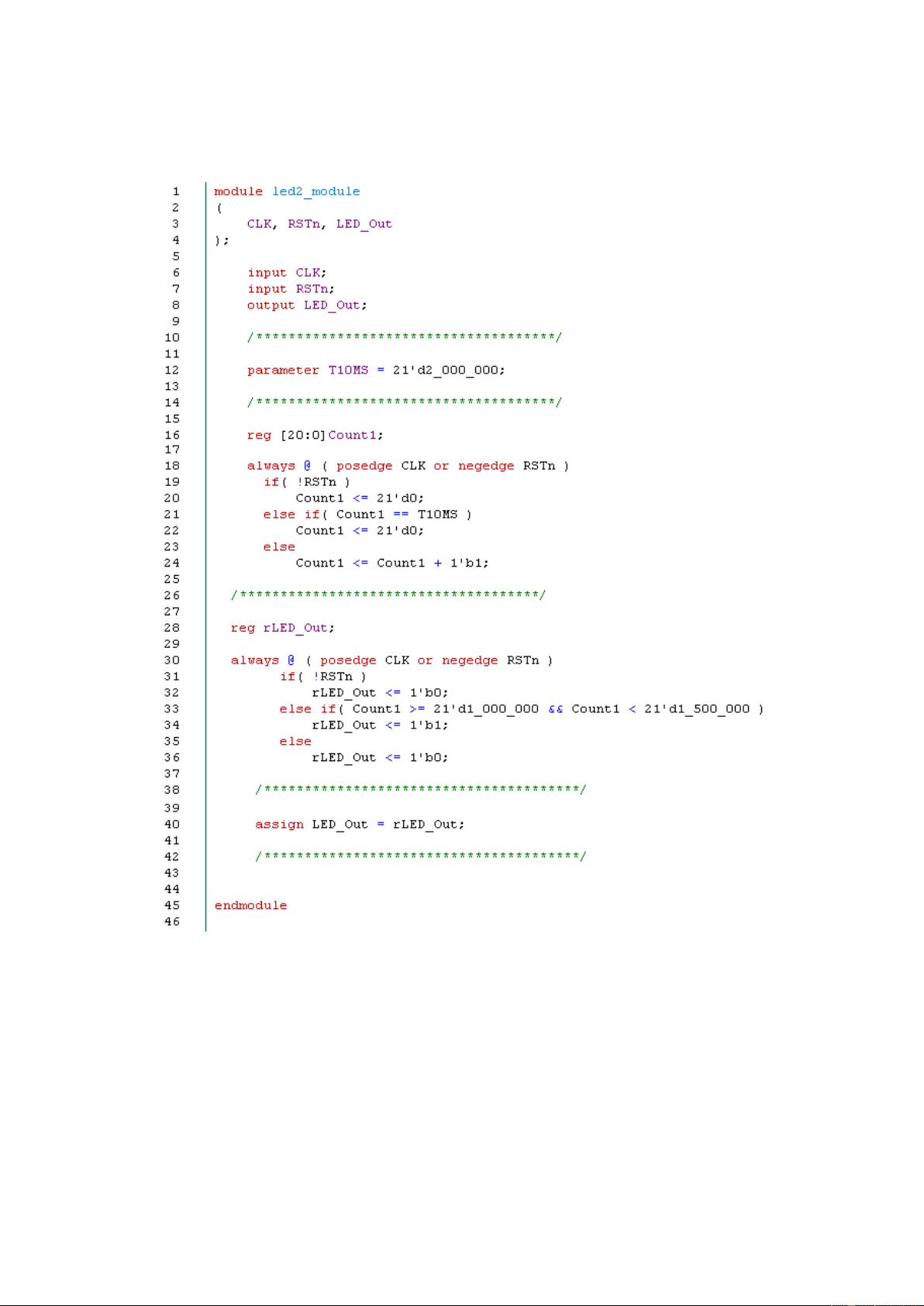

第二章“低级建模-基础知识”深入探讨了Verilog HDL的基础。2.1节介绍了预序操作和并行操作,通过一系列的实验,如永亮的流水灯,展示了如何用Verilog编写模块。实验一的四个子模块(led0_module.v至led3_module.v)和顶级模块(top_module.v)用于构建一个简单的LED控制电路,帮助理解并行执行的概念。2.2节进一步讨论了并行操作的重要性,并提供了闪灯和流水灯的实现(如flash_module.v和run_module.v)。2.3节强调Verilog HDL不是传统的编程,而是硬件建模,它描述的是实际硬件的行为。2.4节和2.5节分享了一些关于低级建模的故事和资源,展示了如何利用Verilog HDL进行硬件级别的设计。

书中还通过消抖模块(实验三和四)来教授如何处理信号噪声,避免误触发。实验三的detect_module.v、delay_module.v和debounce_module.v演示了如何实现基本的消抖功能,而实验四则更深入地探讨了这一主题。2.6节指出在控制模块设计时可能会遇到的挑战,通过实验五和六(SOS信号的生成)来实践控制逻辑的设计,如sos_module.v、control_module.v、sos_generator_module.v和inter_control_module.v,这些模块共同生成SOS求救信号,进一步强化了读者对控制逻辑的理解。

“VerilogHDL那些事儿V3.0”通过实例和理论相结合的方式,系统地介绍了Verilog HDL的基础知识和FPGA设计的基本步骤,对于想要进入FPGA领域的初学者来说是一本宝贵的参考资料。通过学习这本书,读者不仅可以掌握Verilog HDL的基本语法,还能了解到如何使用这种语言来创建复杂的数字系统模型。

2011-11-10 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

2024-12-28 上传

linbai5

- 粉丝: 1

- 资源: 8