计算机组成原理实验:32位ALU设计与分析

需积分: 0 86 浏览量

更新于2024-08-03

收藏 503KB PDF 举报

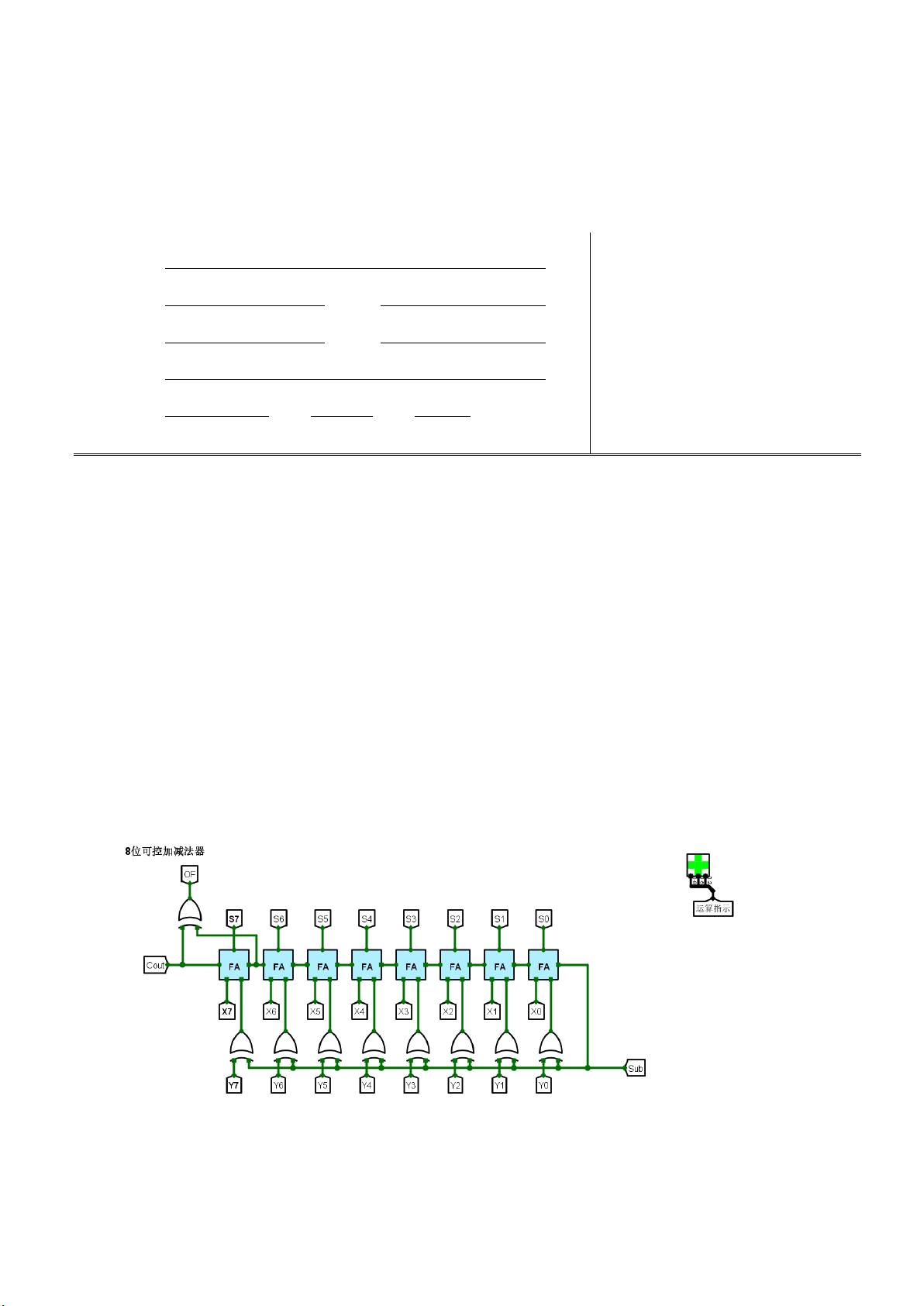

"桂林电子科技大学计算机与信息安全学院的一份实验报告,由学生邵嘉豪完成,实验主题为32位ALU(算术逻辑运算单元)设计。实验目的是掌握ALU的基本构成,学习Logisim软件中运算组件的使用,以及ALU的设计与仿真方法。实验内容包括8位可控加减法器、4位可级联先行进位电路、4位快速加法器、16位快速加法器和32位快速加法器的设计。"

在计算机硬件领域,ALU是计算机组成的核心部分,它负责执行基本的算术和逻辑运算。在本次实验中,邵嘉豪同学通过Logisim这个数字逻辑设计软件进行了一系列的ALU设计练习。首先,他设计了8位可控加减法器,利用全加器FA实现了加法和减法操作,通过控制sub信号来切换加法和减法。当sub为0时,执行加法,反之执行减法。

接着,设计了4位可级联先行进位电路,这个电路通过进位生成函数Gi和传递函数Pi,以及进位输入Cin,计算出高四位的进位输出C1到C4。这种设计可以快速传播进位信号,提高运算效率。

在第三关,邵嘉豪构建了4位快速加法器,它依赖于CLA74182芯片来并行计算进位值,该芯片能同时处理多个位的加法,减少了运算时间。通过Xi和Yi的异或运算和乘运算,结合CLA74182的进位输出,可以得到最终的运算结果。

第四关,他扩展了设计,构建了一个16位快速加法器。这里,32位输入数据被分成四个4位数据,分别送入四个4位快速加法器,然后结合进位信号Cin,生成低4位的运算结果S0到S3。此外,每个4位快速加法器的进位输出G*和P*连接到先行进位电路,进一步计算出高12位的进位。

最后一关,通过拼接两个16位快速加法器,实现了32位快速加法器。这种方法有效地利用了已有的16位设计,扩展到了更高级别的数据处理能力。

整个实验过程中,邵嘉豪不仅掌握了ALU的结构和工作原理,还锻炼了使用Logisim进行数字逻辑设计的能力。实验报告的撰写则要求他反思实验步骤,分析设计过程,这有助于深化对理论知识的理解,并提升问题解决和文档整理技能。

2024-01-03 上传

2024-03-09 上传

156 浏览量

2023-07-25 上传

2024-12-06 上传

2023-10-22 上传

枸橼酸镓

- 粉丝: 0

- 资源: 1

最新资源

- Kokoa-clone_var_2

- 毕业设计:基于图神经网络的异构图表示学习和推荐算法研究.zip

- SAMPLauncherNET:SAMPLauncherNET是San Andreas多人游戏的启动器

- learn-js:各种JavaScript示例的存储库,重点是更新的ES67代码

- Data-Science-Portfolio:所有DSC课程

- Splitfire:测试Splitfire

- 中兴盒子不开启adb情况下抓取日志和安装apk

- curso-django:在演示文稿中构建应用程序的通用框架或框架Django para Python nomóduloDjango durante或Bootcamp DevPro

- EventUtil.js:EventUtil.js

- 本科毕业设计的内容,社交媒体文本中的情感分析,运用了情感字典和机器学习的方法.zip

- TabbyNotes-crx插件

- 报名表格附件.rar

- quickcurver:著名游戏“ Achtung die Kurve”(也称为“ Curve Fever”)的QtC ++(OpenGL加速)实现

- startup-mashup:这个 repo 包含在 Startup Mashup 中举行的 Hackathon Web 问题的解决方案。 这里使用的语言是Java

- browsh:一种完全基于文本的浏览器,可渲染到TTY和浏览器

- Bitvavo Darker-crx插件