FPGA数字电路设计实战:模块调用与数码管显示

版权申诉

46 浏览量

更新于2024-09-07

收藏 325KB PPTX 举报

本资源是一份关于基于FPGA的数字电路设计与实现的专题资料,主要针对2021-2022年的教学需求,由卢有亮教授分享。内容涵盖了如何在FPGA设计中实现模块间的互相调用,以构建复杂功能,以数字显示系统为例进行讲解。

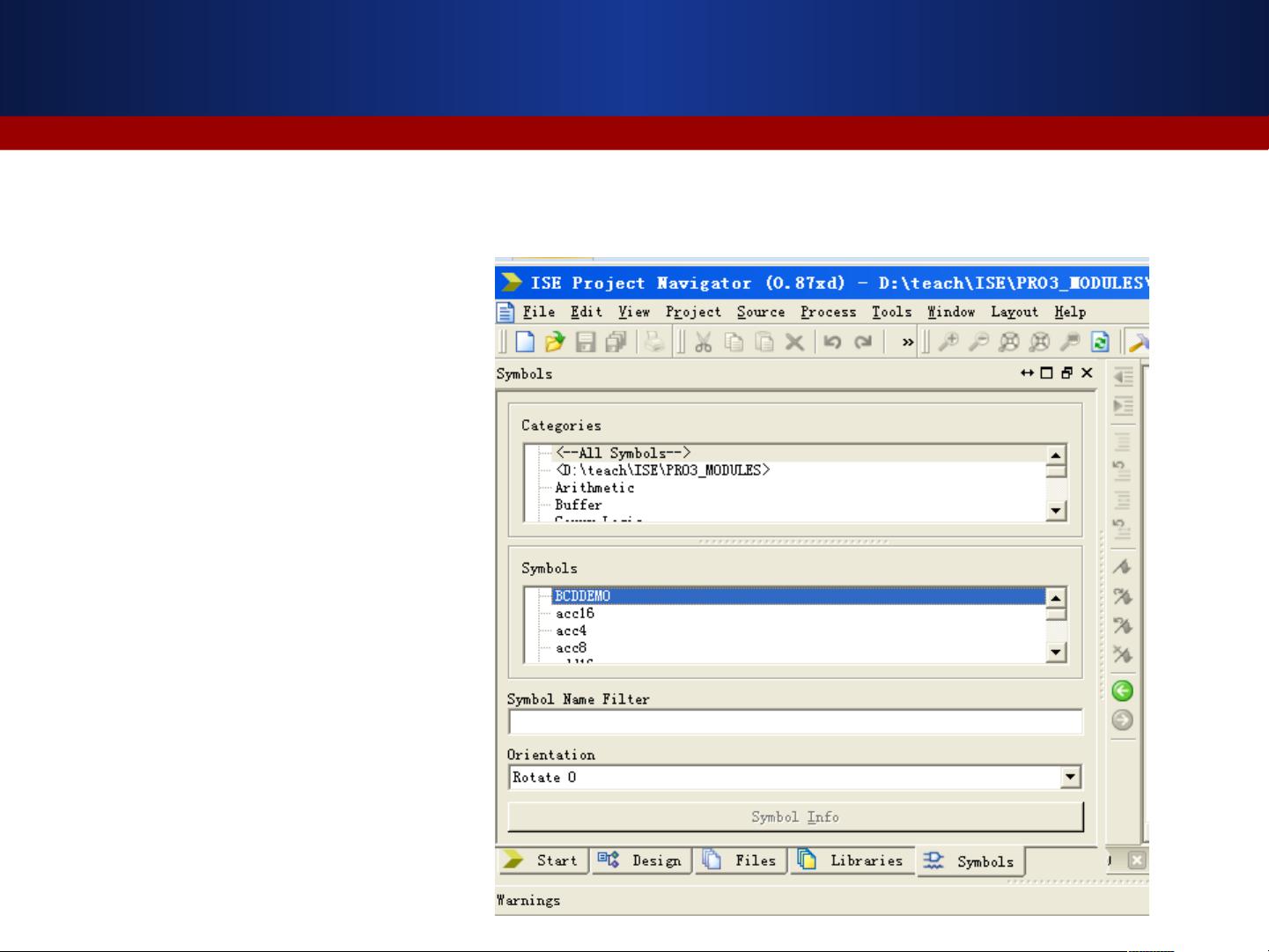

在第三课中,重点讨论了如何在顶层模块中集成之前开发的独立模块。首先,要创建一个新的工程并将前一节的代码引入。为了使顶层模块能够使用这些模块,关键步骤是将模块转换为可使用的元件。这涉及到使用CreateSchematicSymbol工具将模块文件转换为符号,以便在原理图中添加和管理。

顶层模块开始于创建一个新的原理图文件,并将自定义模块作为符号添加到各个页面中。在这里,模块名为BCDDEMO,它包含了输入的时钟(clock)、数据(data)、以及输出的数码管段码(seg)和位码(dig)。为了实现数码管的动态显示,模块内部还定义了寄存器如rseg、rdig、disp_dat和计数器(count)。

在模块的实现中,通过信号分配语句(assign)将模块内部变量映射到顶层模块的输出。例如,`assign seg = rseg;` 和 `assign dig = rdig;`。时序逻辑部分通过异步边沿触发器(always @(posedge clock))控制计数器的递增和显示数据的更新,确保每次时钟上升沿都会进行一次计数和数码管状态的改变。

计数器用于控制数码管的切换,当计数值为预设的二进制表示(如2'h0~2'h3分别对应数码管的显示顺序)时,rdig会被设置为相应的位码序列,使得每个数码管在特定时刻显示对应的数字。此外,当disp_dat存储的数字值改变时,根据不同的数值,顶层模块会更新rseg寄存器中的段码,从而驱动数码管显示相应的字符。

这部分内容展示了FPGA设计中的模块化思想,即通过模块间的组合和交互来实现复杂的功能。通过这种方式,设计师可以复用已有的模块并灵活地组合它们,提高设计的效率和可维护性。同时,它也强调了时序逻辑在同步电路设计中的重要性,以及如何通过条件分支(case语句)来控制不同情况下的行为。这对于理解和应用FPGA技术,特别是对于初学者来说,是非常实用和重要的知识点。

2021-10-03 上传

2023-02-26 上传

2023-05-26 上传

2023-05-26 上传

2024-10-27 上传

2023-03-21 上传

2024-10-30 上传

chenlu0528

- 粉丝: 2

- 资源: 48万+

最新资源

- NeuMedia:一个简单易用的高级媒体播放器-开源

- 行业分类-设备装置-跨分布式控制系统服务器的实时事件查看.zip

- techsith-redux

- 飞翔的小鸟java源码-java:Java

- 30daysofdev:开发30天的官方网站

- 约会管理系统

- 华为简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- EDGER:创建用于测量恒星流出腔的半张角的算法

- 数据可视化驾驶舱-07.zip

- shop:商家和客户的Payngolinky前端

- 自己常用shader(自连).zip

- 21本搜索书

- snippits

- ndef-tools-for-android:从 code.google.compndef-tools-for-android 自动导出

- mw1utils:mw1utils:Waldorf微波工具-开源

- Andersnormal.us