TI ADC09SJ1300:1.3-GSPS 9位高速模数转换器

需积分: 5 110 浏览量

更新于2024-06-28

4

收藏 6.69MB PDF 举报

"TI-ADC09SJ1300.pdf 是一款由TI(德州仪器)推出的高性能模拟数字转换器(ADC),具有四通道、双通道和单通道配置,采样率为1.3 GSPS,9位分辨率,并集成了JESD204C串行数据接口。这款ADC主要应用于高速数据采集系统,如通信、雷达和测试测量设备等高精度信号处理场景。"

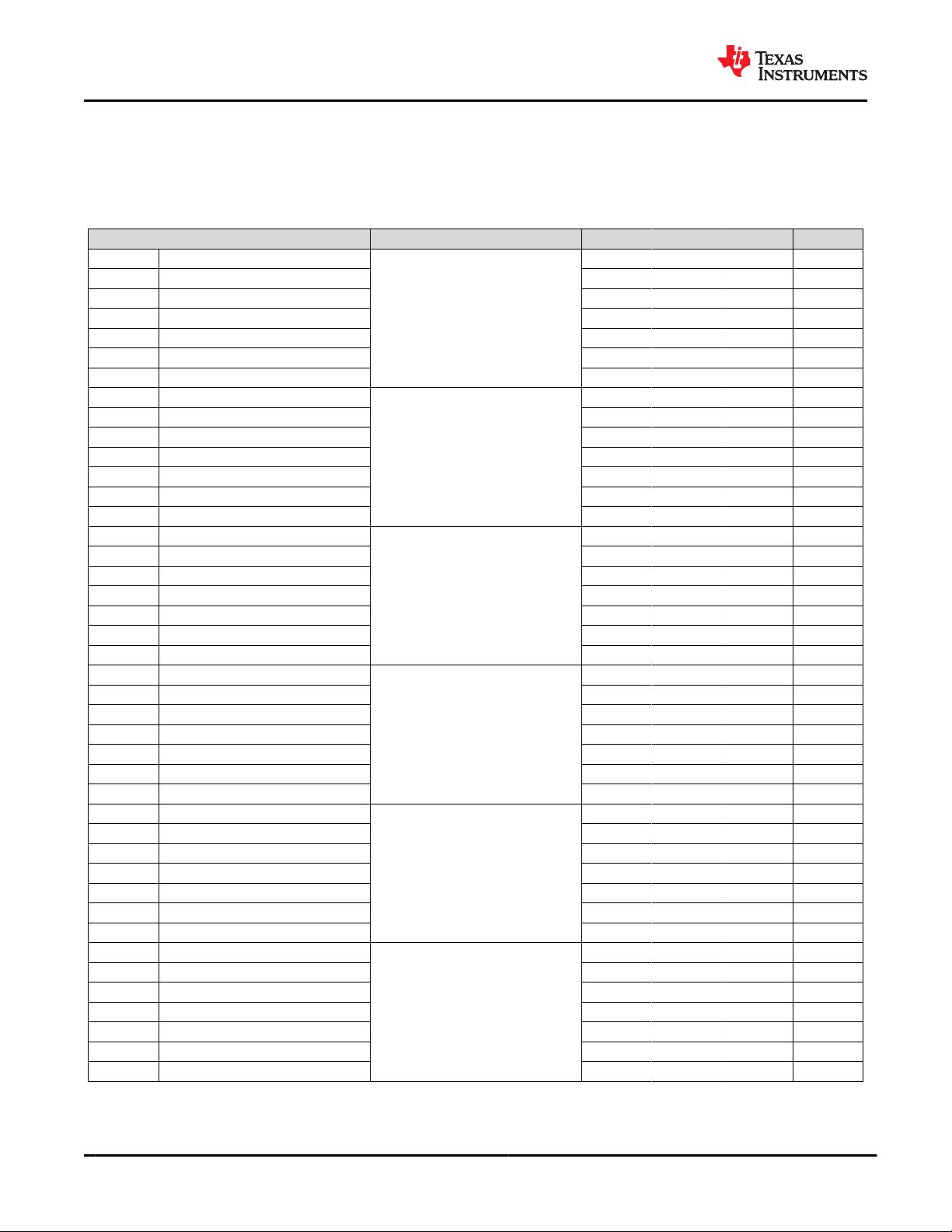

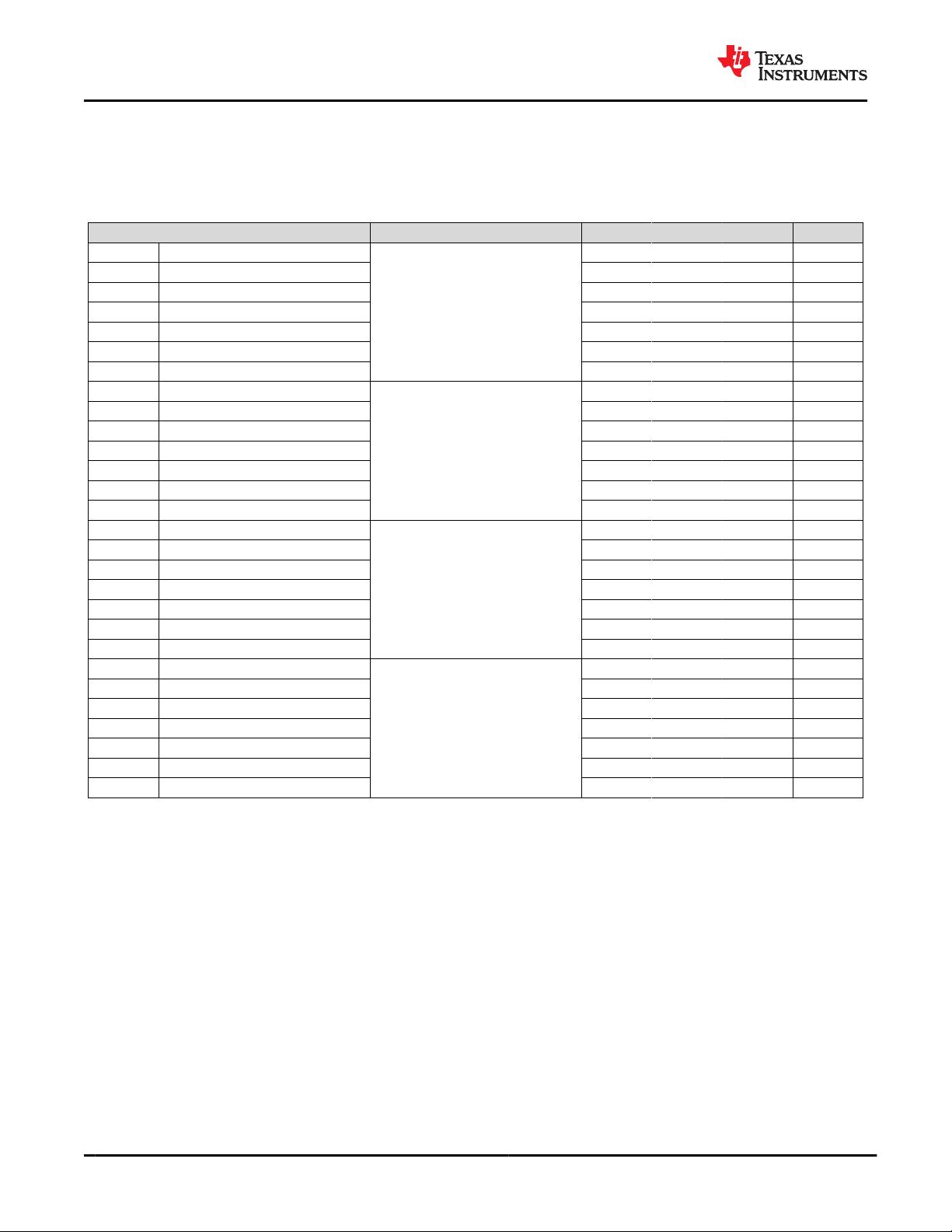

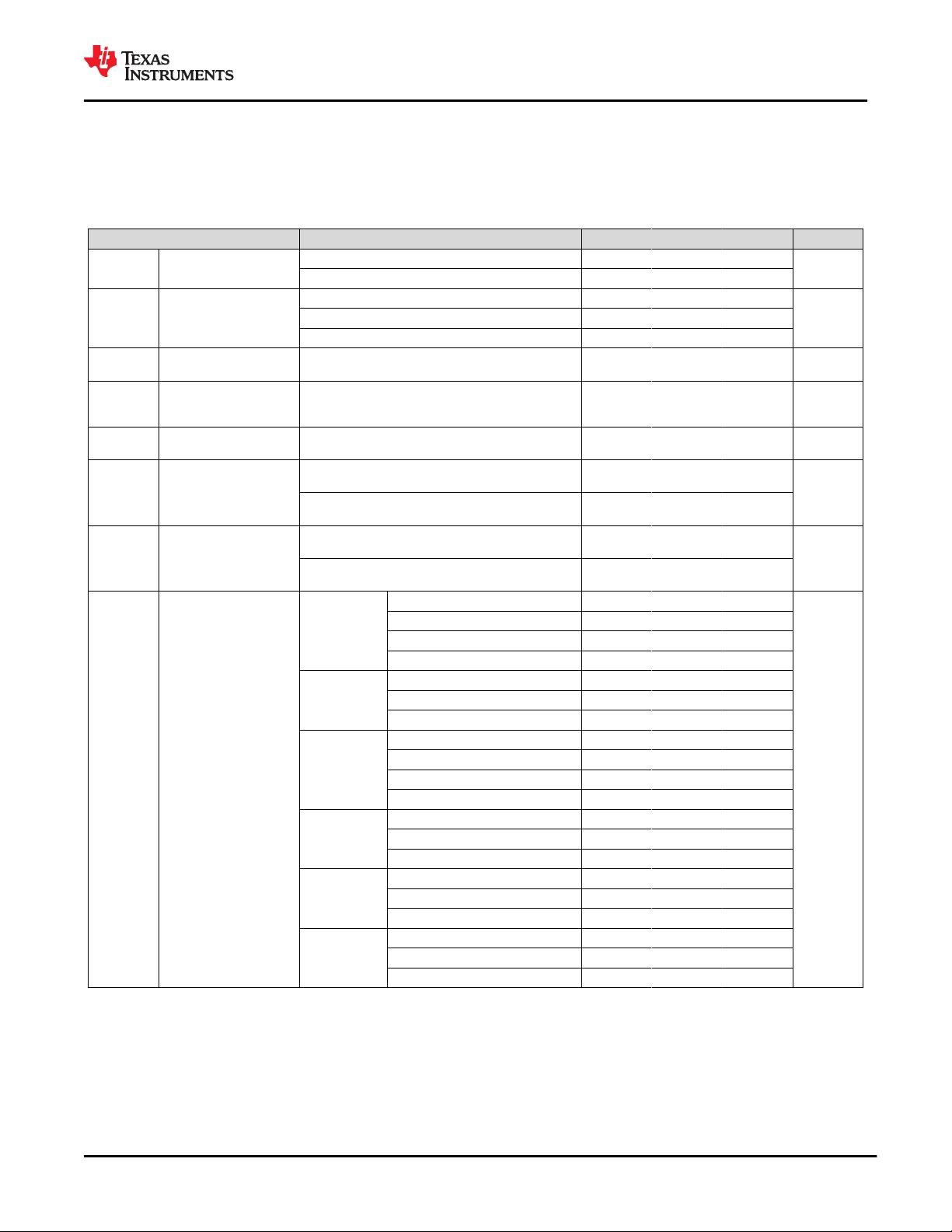

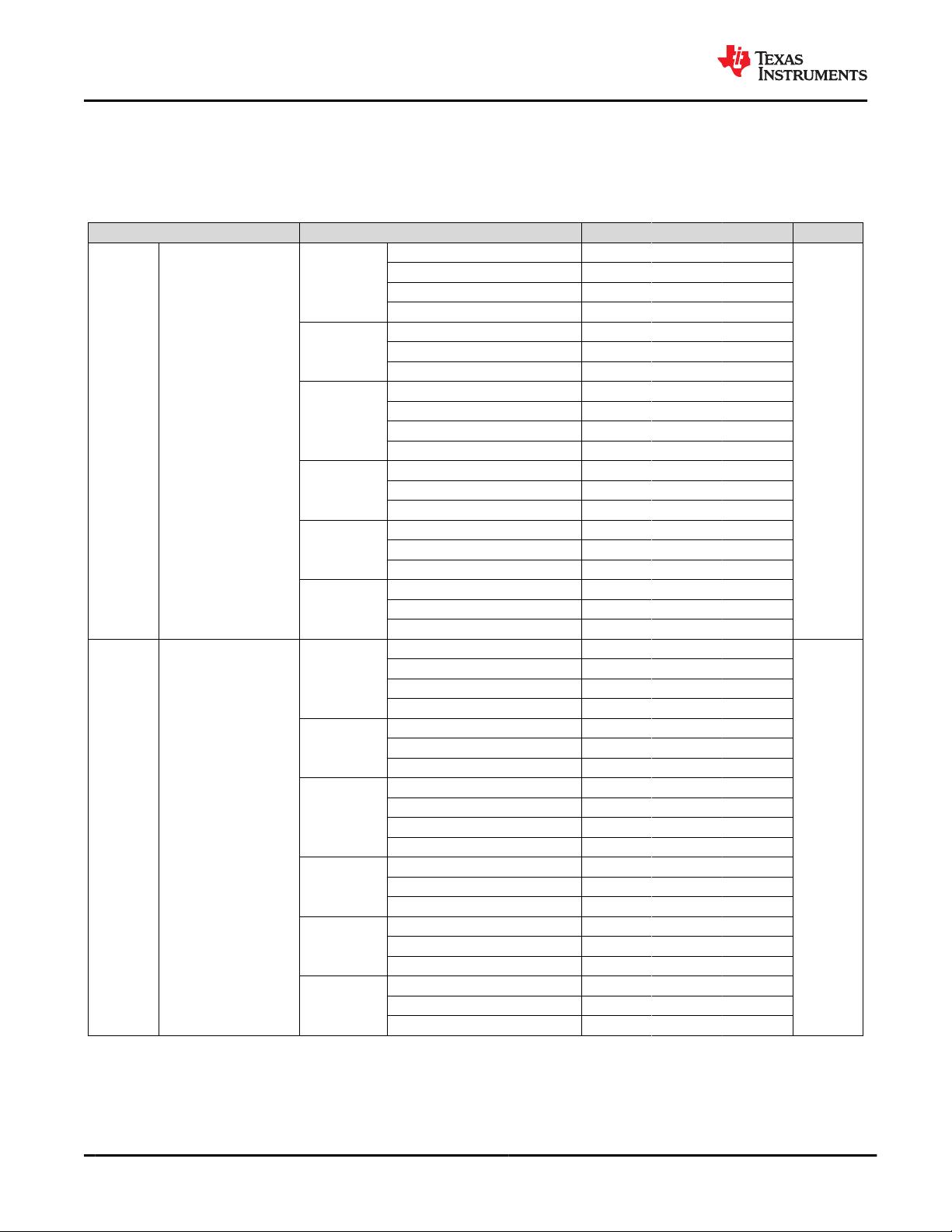

TI的ADC09xJ1300系列ADC的核心特性包括:

1. **分辨率与采样率**:该器件提供9位的分辨率,最大采样率可达1.3吉采样每秒(GSPS),满足高速数据转换的需求。

2. **非交织架构**:非交织设计意味着每个通道独立工作,无需复杂的交织逻辑,简化了系统设计。

3. **内部抖动减少**:内置的抖动减少功能通过内部dither技术降低了高阶谐波,提高了信号质量。

4. **性能规格**:在-1dBFS输入功率下,信噪比(SNR)达到53.5dBFS,有效位数(ENOB)为8.5位,无杂散动态范围(SFDR)为64dBc,噪声地板在-20dBFS时为-143dBFS,体现了其出色的信号转换性能。

5. **全尺度输入电压**:满尺度输入电压为800mV差分峰峰值,适用于各种输入信号范围。

6. **全功率输入带宽**:高达6GHz的全功率带宽,确保了对高频信号的有效处理。

7. **JESD204C串行数据接口**:支持2到8个(四通道/双通道)或1到4个(单通道)SerDes通道,最大波特率可达17.16Gbps,兼容64B/66B和8B/10B编码模式,以及JESD204B接收机,同时支持子类1的确定性延迟特性。

8. **内部时钟生成**:提供内部PLL和VCO(7.2-8.2GHz),减少了外部时钟组件的需求,简化系统设计。

9. **SYSREF窗口同步**:SYSREF窗口功能简化了系统中的同步操作,确保多ADC之间的精确时间对齐。

10. **四路时钟输出**:可以为FPGA或其他相邻ADC提供参考时钟,同时也为SerDes收发器提供参考时钟,优化系统时钟管理。

11. **时间戳输入和输出**:对于脉冲系统,时间戳功能可实现事件的精确时间记录和处理。

12. **功耗**:在1GSPS运行时,四通道模式下的功耗未具体给出,但表明了其高效能表现。

TI-ADC09SJ1300是一款高集成度、高性能的ADC,适合需要高速、高精度转换的系统应用,其JESD204C接口和丰富的辅助功能使其在现代高速数字系统中具有广泛的应用前景。

2022-12-16 上传

2022-11-27 上传

2022-11-27 上传

2022-11-27 上传

2022-11-27 上传

2022-11-27 上传

2022-11-27 上传

2022-11-27 上传

2022-12-03 上传

不觉明了

- 粉丝: 6313

- 资源: 5764

最新资源

- 毕业设计&课设--分享一个适合初学者的图书管理系统(毕业设计)无框架原生.zip

- marvel_api

- Chrome-Memory-Manager:此扩展仅在 chrome 的开发者频道上有效。 Chrome合金

- Broad-Learning-System:BLS代码

- 毕业设计&课设--东北大学本科毕业设计模板.zip

- mcmc_clib:C程序简化ODE模型参数的歧管MALA采样

- yii2-meta-activerecord:一个简单的Yii2扩展,扩展了ActiveRecord功能,以允许在补充表中使用WordPress样式的元字段

- job-recover-client:JobRecover的客户端文件(前端)

- TestDrive-Titanium:使用这个空白的 Titanium 应用程序试驾 Kinvey

- final-form-focus::chequered_flag:最终表单“装饰器”,它将在尝试提交表单时尝试将焦点应用于第一个字段,但会出现错误

- keras-recommendation:使用Keras实施推荐系统

- Excel模板年度工程类中初级打分汇总表.zip

- GoIT-Course:这是我在GoIT课程中的第二门课程

- 毕业设计&课设--高校毕业设计管理系统(毕业设计).zip

- PyTorchZeroToAll:DL-SEMINAR第1周任务

- Geo_Aggs-Map