Astro物理设计软件:数字电路后端设计与流程解析

需积分: 43 133 浏览量

更新于2024-07-21

收藏 2.44MB PDF 举报

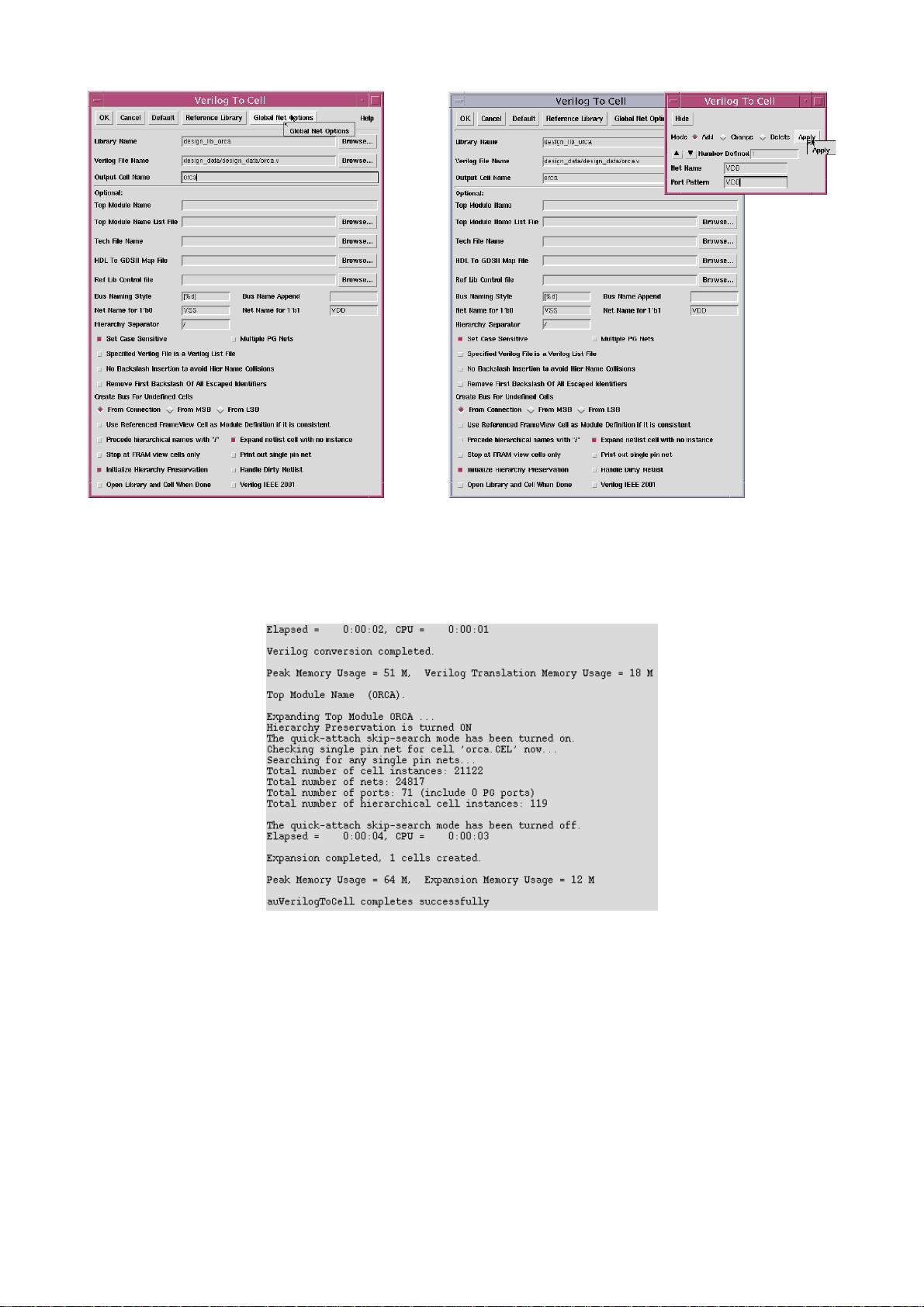

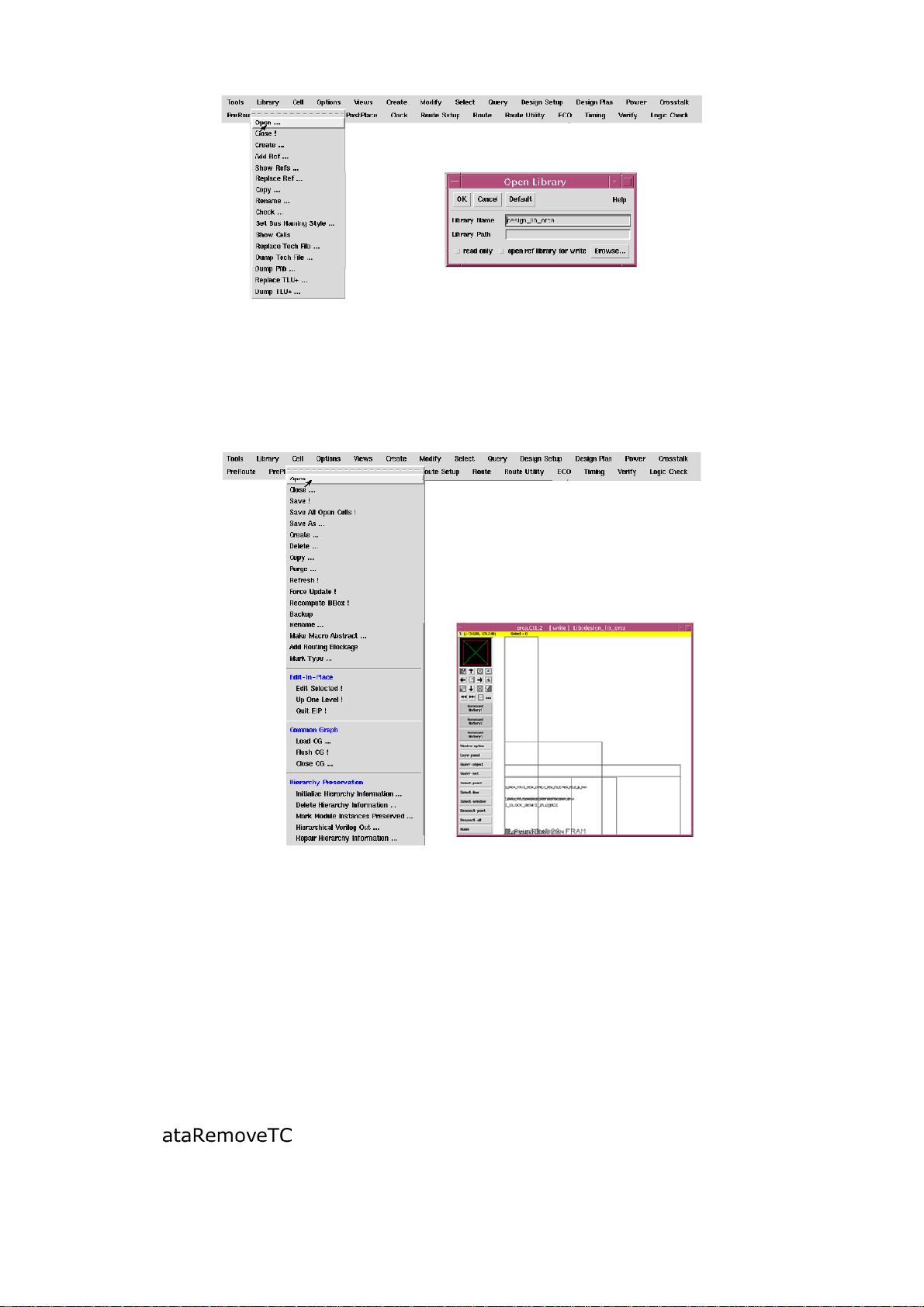

"Astro是Synopsys公司开发的一款用于物理设计的软件,它在深亚微米工艺中扮演重要角色,着重于降低连线延迟,优化时序性能,以满足现代集成电路设计的需求。 Astro的物理设计流程包含了多个步骤,如数据准备、布局、布线和时序优化等。在数据准备阶段,需要输入网表文件、时序约束文件、参考库、TDF文件以及工艺tf文件。网表通常由Design Compiler (DC) 综合生成,而时序约束文件(SDC)则需经过修正,确保Astro能正确识别时钟源。参考库包括标准单元库和IO库,由Foundry提供,用于指导设计过程。整个流程旨在帮助设计者理解Astro如何在复杂设定下实现高效物理设计。"

在数字电路的后端设计中,Astro的布局布线流程是关键步骤。随着工艺技术的进步,连线延迟成为决定电路性能的关键因素,因此,设计者必须不仅仅关注逻辑门的布局,更要考虑如何优化连线以减少延迟。Astro提供了这样的能力,它的一站式流程能同时进行布局和布线,且内置时序优化功能,确保设计的物理实现能够达到预定的性能指标。

在数据准备阶段,首先需要网表文件,这是前端设计的结果,通常采用Verilog (.v)格式。DC是常用的综合工具,可以生成符合Astro需求的网表。其次,时序约束文件(SDC)定义了设计的时序要求,需要调整以适应Astro,特别是时钟定义,必须明确指向网表中的实际时钟源。参考库包含必要的标准单元信息,由Foundry提供,对于正确布局和布线至关重要。此外,TDF文件定义了PAD的位置和顺序,而工艺tf文件则包含了工艺相关的参数,这两者都是Astro运行的必要输入。

在Astro的流程中,布局阶段涉及逻辑模块的物理定位,以减少信号路径长度和提高效率。布线阶段则连接这些模块,同时优化路径以减少延迟。时序优化环节会根据SDC文件的约束,不断调整布局和布线,确保设计满足时序闭合的要求。

总结来说,Astro作为一款强大的物理设计工具,其流程涵盖了从数据准备到时序优化的全过程,旨在在深亚微米工艺环境下,通过精确布局和布线,有效地优化电路的时序性能。理解并掌握Astro的工作原理和使用方法,对于任何从事集成电路后端设计的工程师来说都至关重要。

129 浏览量

830 浏览量

229 浏览量

318 浏览量

590 浏览量

2021-10-04 上传

3469 浏览量

thekingliujian

- 粉丝: 0

- 资源: 2

最新资源

- 图书管理备案系统.rar

- the_computer_vision_app:一款可在网络上执行常见的计算机视觉任务的应用程序

- java笔试题算法-C5:用于C#/.NET的C5泛型集合库

- comment2votes:seq2seq架构,用于预测reddit评论的投票

- andyseoDB

- 家居城促销顾客须知(转盘上摇奖的注意事项)

- 永宏PLC编成软件 适合FBE FBS B1Z等型号.rar

- file-system-access:公开用户设备上的文件系统,以便Web应用程序可以与用户的本机应用程序进行互操作

- jstl-tld.zip

- Ikasumi-crx插件

- 超可爱卡通动物图标下载

- 任务一-使用监督的机器学习预测:根据编号预测学生的百分比。 学习时间

- CSE212_DataStructures_Guide

- 初级java笔试题-awesome-php-resources:精选的很棒的php列表

- ךופה לע ךופה - הפוך על הפוך-crx插件

- 作业六